10进制计数器设计方案汇总(六款电路设计原理及程序分享) |

您所在的位置:网站首页 › 利用一片74ls74组成两位异步二进制加法计数器的方法 › 10进制计数器设计方案汇总(六款电路设计原理及程序分享) |

10进制计数器设计方案汇总(六款电路设计原理及程序分享)

|

计数器是一种能够记录脉冲数目的装置,是数字电路中最常用的逻辑部件。计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能。计数器由基本的计数单元和一些控制门所组成,计数单元则由一系列具有存储信息功能的各类触发器构成。计数器在数字系统中应用广泛,如在电子计算机的控制器中对指令地址进行计数。本文为大家带来六种10进制计数器设计方案。 10进制计数器设计方案一:JK触发器实现的同步十进制加法计数器

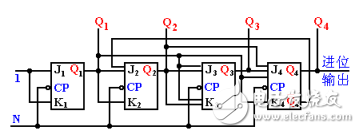

同步十进制加法计数器逻辑图 在上图所示的同步十进制加法计数器中:

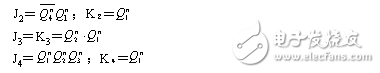

将这些关系代入各JK触发器的特性方程,则得计数器的状态方程为:

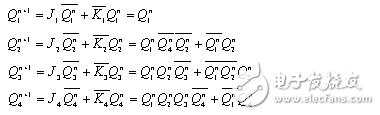

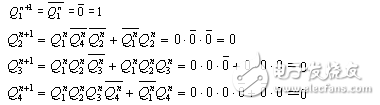

设计数器初始状态为0000,第1个计数脉冲来到后,

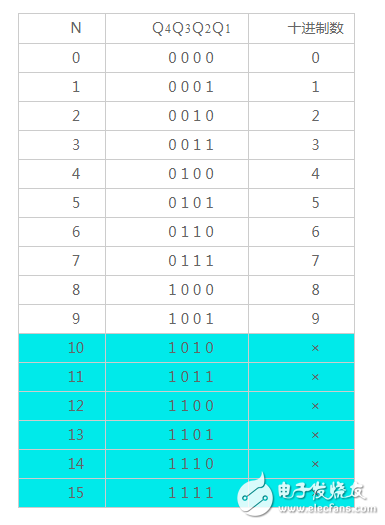

即计数器的状态为0001。可以算得,第2个计数脉冲来到后,其状态为0010。以下类推,可以得到如表Z1503所示的状态表。但需注意,在第9个脉冲来到后,亦即计数器处于1001态时,

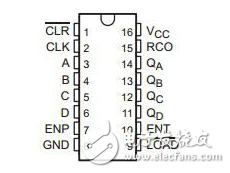

同步十进制加法计数器状态表 10进制计数器设计方案二:CD54HC160异步复位的BCD同步十进制计数器CD54HC160是具有异步复位的BCD同步十进制计数器。其引脚图如图2-30所示。其中,CLR为计数器复位端,CLR=0时,QDQCQBQA=0000;LOAD是计数器的预置端,DCBA是预置数据输入端。当LOAD=0时,在CLK的上升沿作用下,QDQCQBQA=DCBA;ENP和ENT是计数器的功能控制端,ENP和ENT均为高电平时计数器才能计数,它们中有任何一个为低电平时,计数器的装备不会发生变化,而是处于保持状态。RCO是计数器的进位输出,RCO=ENT× QDQA。

CD54HC160引脚图 步骤1.根据十进制计数器的原理和特点,利用VHDL语言的基本描述语句编写出十进制计数器的VHDL语言程序。 2.对所设计的十进制计数器的VHDL程序进行编译,然后利用波形编辑器对其进行仿真,初步验证程序设计的正确性。 3.利用开发工具软件,选择所用可编程逻辑器件,并对十进制计数器进行管脚配置。 4.通过下载电缆将编译后的*.sof文件下载到目标器件之中,并利用实验开发装置对其进行硬件验证。 程序LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY CD54HC160 IS PORT( CLK,D,C,B,A, CLR, LOAD,ENP,ENT: IN STD_LOGIC; QD,QC,QB,QA,RCO: BUFFER STD_LOGIC); END CD54HC160; ARCHITECTURE behave OF CD54HC160 IS SIGNAL EN: STD_LOGIC_VECTOR(1 DOWNTO 0); SIGNAL D_SIGNAL: STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL Q_SIGNAL: STD_LOGIC_VECTOR(3 DOWNTO 0); BEGIN PROCESS(LOAD,D,C,B,A,CLK,CLR, ENP,ENT) BEGIN EN D_SIGNAL IF (CLR=‘0’) THEN Q_SIGNAL‘0’); ELSE IF CLK‘EVENT AND CLK=’1‘ THEN IF (LOAD=’0‘) THEN Q_SIGNAL ELSIF (EN=“11”) THEN IF Q_SIGNAL Q_SIGNAL ELSE Q_SIGNAL’0‘); END IF; ELSE Q_SIGNAL END IF; END IF; END IF; QD QC QB QA RCO END PROCESS; END behave; 10进制计数器设计方案三:74LS161的六位十进制计数器设计

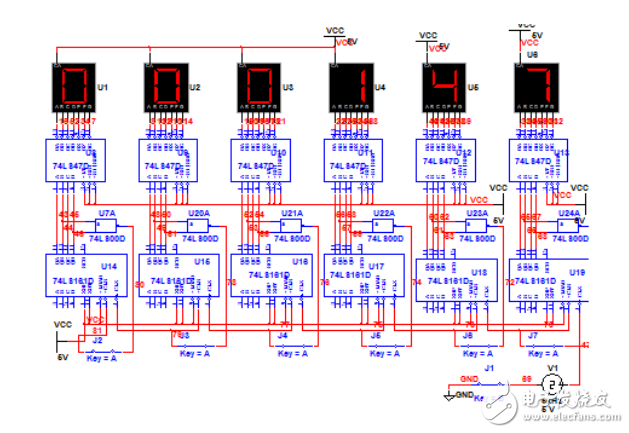

仿真电路(如上图)脉冲信号首先进入74LS161的CLK端,其QA~QD端接入74LS47A~D后B端和D端接逻辑与非门,当74LS161计数到1010使该芯片进位,并产生一个脉冲,到下一个74LS161的CLK端如此循环完成0-999999的计数功能。用开关控制锁存完成锁存功能,其中CLK为数据输入端,QA~QD为数据输出端可以用来驱动74LS47芯片完成正常译码。开关控制CLK和CLR,当CLK和CLR为高电平时,OA---OG为正常逻辑状态,可以用来驱动显示器使其完成0—9的正常显示,当CL为低电平时,即不驱动显示器,但内部的逻辑操作不受影响。CET和CEP为锁存允许端。 |

【本文地址】

今日新闻 |

推荐新闻 |