ISA总线标准定义 |

您所在的位置:网站首页 › isa标准温度怎么算 › ISA总线标准定义 |

ISA总线标准定义

|

ISA总线标准定义

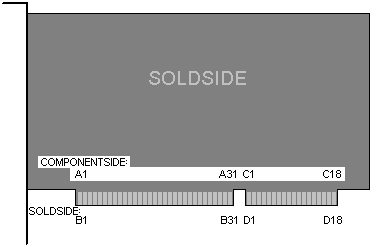

参考链接:http://www.51hei.com/chip/354.html ISA 是 Industry Standard Architecture 的缩写 ISA插槽是基于ISA总线(Industrial Standard Architecture,工业标准结构总线)的扩展插槽,其颜色一般为黑色,比PCI接口插槽要长些,位于主板的最下端。其工作频率为8MHz左右,为16位插槽,最大传输率16MB/sec,可插接显卡,声卡,网卡已及所谓的多功能接口卡等扩展插卡。其缺点是CPU资源占用太高,数据传输带宽太小,是已经被淘汰的插槽接口。 ISA 是8/16bit 的系统总线,最大传输速率仅为8MB/s ,但允许多个CPU 共享系统资源。由于兼容性好,它在上个世纪80年代是最广泛采用的系统总线,不过它的弱点也是显而易见的,比如传输速率过低、CPU占用率高、占用硬件中断资源等。后来在PC‘98 规范中,就开始放弃了ISA 总线,而Intel 从i810 芯片组开始,也不再提供对ISA 接口的支持。 ISA总线扩展插槽由两部分组成,一部分有62引脚,其信号分布及名称与PC/XT总线的扩展槽基本相同,仅有很小的差异。另一部分是AT机的添加部分,由36引脚组成。这36引脚分成两列,分别称为C列和D列。

ISA接口卡的外观 ISA插槽的外观 ISA接口引脚定义 引脚 定义 说明 A1 /I/O CH CK I/O channel check; active low=parity error A2 D7 Data bit 7 A3 D6 Data bit 6 A4 D5 Data bit 5 A5 D4 Data bit 4 A6 D3 Data bit 3 A7 D2 Data bit 2 A8 D1 Data bit 1 A9 D0 Data bit 0 A10 I/O CH RDY I/O Channel ready, pulled low to lengthen memory cycles A11 AEN Address enable; active high when DMA controls bus A12 A19 Address bit 19 A13 A18 Address bit 18 A14 A17 Address bit 17 A15 A16 Address bit 16 A16 A15 Address bit 15 A17 A14 Address bit 14 A18 A13 Address bit 13 A19 A12 Address bit 12 A20 A11 Address bit 11 A21 A10 Address bit 10 A22 A9 Address bit 9 A23 A8 Address bit 8 A24 A7 Address bit 7 A25 A6 Address bit 6 A26 A5 Address bit 5 A27 A4 Address bit 4 A28 A3 Address bit 3 A29 A2 Address bit 2 A30 A1 Address bit 1 A31 A0 Address bit 0 B1 GND Ground B2 RESET Active high to reset or initialize system logic B3 +5V +5 VDC B4 IRQ2 Interrupt Request 2 B5 -5VDC -5 VDC B6 DRQ2 DMA Request 2 B7 -12VDC -12 VDC B8 /NOWS No WaitState B9 +12VDC +12 VDC B10 GND Ground B11 /SMEMW System Memory Write B12 /SMEMR System Memory Read B13 /IOW I/O Write B14 /IOR I/O Read B15 /DACK3 DMA Acknowledge 3 B16 DRQ3 DMA Request 3 B17 /DACK1 DMA Acknowledge 1 B18 DRQ1 DMA Request 1 B19 /REFRESH Refresh B20 CLOCK System Clock (67 ns, 8-8.33 MHz, 50% duty cycle) B21 IRQ7 Interrupt Request 7 B22 IRQ6 Interrupt Request 6 B23 IRQ5 Interrupt Request 5 B24 IRQ4 Interrupt Request 4 B25 IRQ3 Interrupt Request 3 B26 /DACK2 DMA Acknowledge 2 B27 T/C Terminal count; pulses high when DMA term. count reached B28 ALE Address Latch Enable B29 +5V +5 VDC B30 OSC High-speed Clock (70 ns, 14.31818 MHz, 50% duty cycle) B31 GND Ground

C1 SBHE System bus high enable (data available on SD8-15) C2 LA23 Address bit 23 C3 LA22 Address bit 22 C4 LA21 Address bit 21 C5 LA20 Address bit 20 C6 LA18 Address bit 19 C7 LA17 Address bit 18 C8 LA16 Address bit 17 C9 /MEMR Memory Read (Active on all memory read cycles) C10 /MEMW Memory Write (Active on all memory write cycles) C11 SD08 Data bit 8 C12 SD09 Data bit 9 C13 SD10 Data bit 10 C14 SD11 Data bit 11 C15 SD12 Data bit 12 C16 SD13 Data bit 13 C17 SD14 Data bit 14 C18 SD15 Data bit 15 D1 /MEMCS16 Memory 16-bit chip select (1 wait, 16-bit memory cycle) D2 /IOCS16 I/O 16-bit chip select (1 wait, 16-bit I/O cycle) D3 IRQ10 Interrupt Request 10 D4 IRQ11 Interrupt Request 11 D5 IRQ12 Interrupt Request 12 D6 IRQ15 Interrupt Request 15 D7 IRQ14 Interrupt Request 14 D8 /DACK0 DMA Acknowledge 0 D9 DRQ0 DMA Request 0 D10 /DACK5 DMA Acknowledge 5 D11 DRQ5 DMA Request 5 D12 /DACK6 DMA Acknowledge 6 D13 DRQ6 DMA Request 6 D14 /DACK7 DMA Acknowledge 7 D15 DRQ7 DMA Request 7 D16 +5 V

D17 /MASTER Used with DRQ to gain control of system D18 GND Ground |

【本文地址】

今日新闻 |

推荐新闻 |