【计算机组成与体系结构Ⅰ】实验7 IP核的使用、D触发器 |

您所在的位置:网站首页 › 自动编程系统的组成和原理图 › 【计算机组成与体系结构Ⅰ】实验7 IP核的使用、D触发器 |

【计算机组成与体系结构Ⅰ】实验7 IP核的使用、D触发器

|

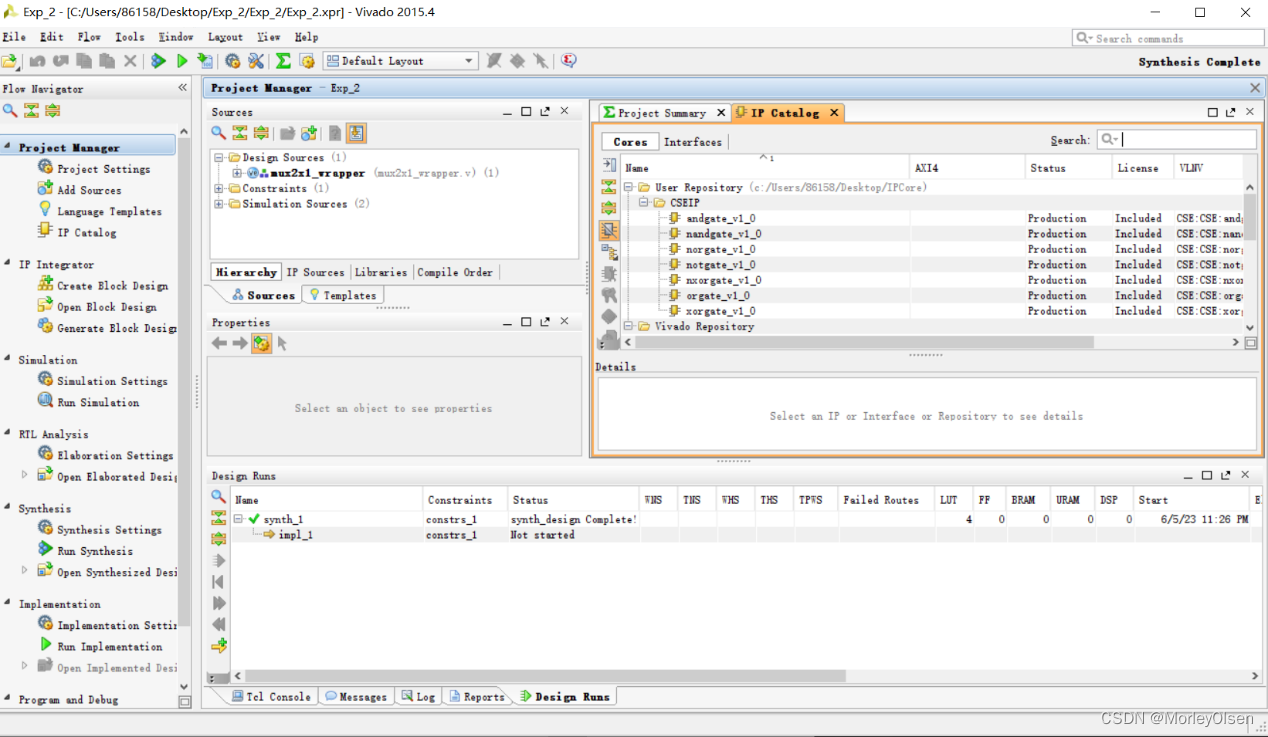

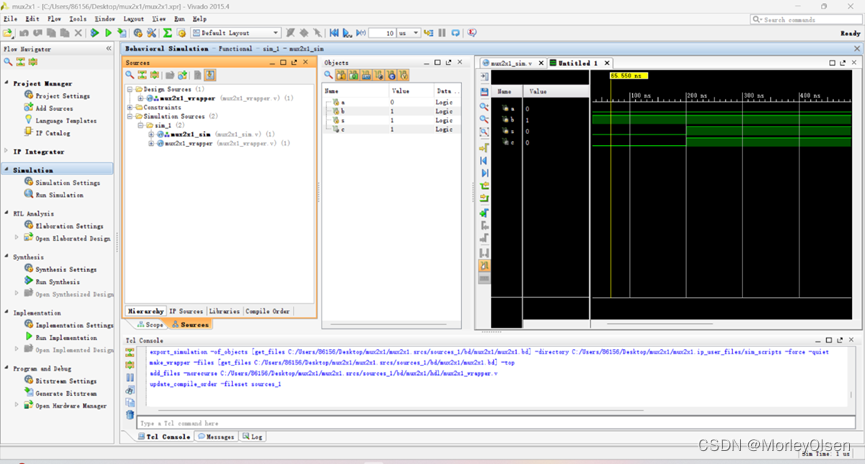

一、实验目的 1:学会设计用IP核和原理图的方式设计电路,完成涉及1位数据的2选1多路选择器。 2:设计带异步置零和写使能端的D触发器。 二、实验环境 软件:Vivado 2015.4操作系统:Windows 10三、实验内容 2.2.1 多路选择器的设计 1:添加IP核文件

2:添加bd文件,在Block Design界面中进行设计

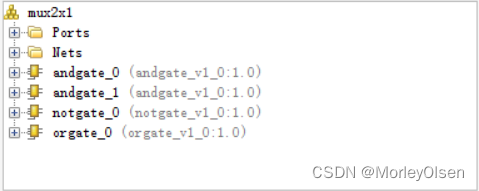

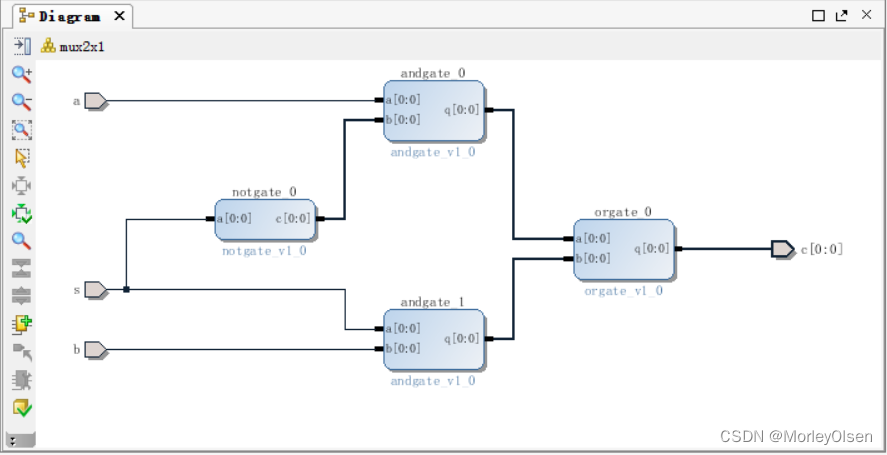

3:放置门电路及端口

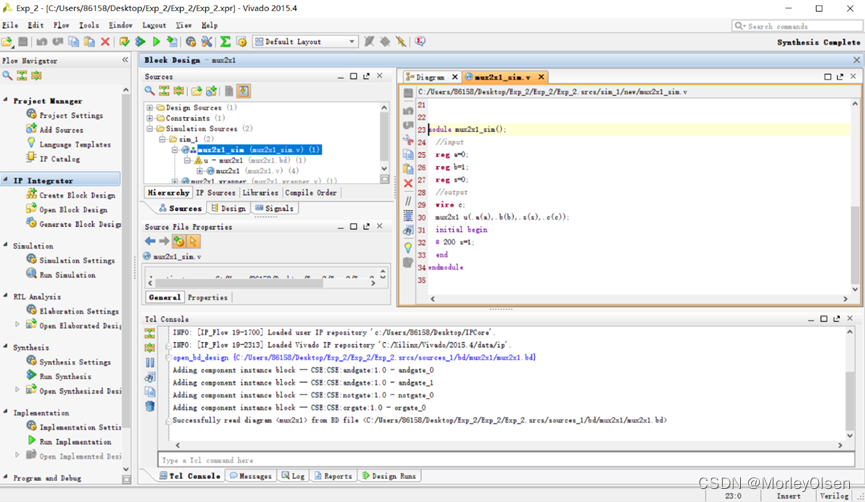

4:添加仿真文件并仿真

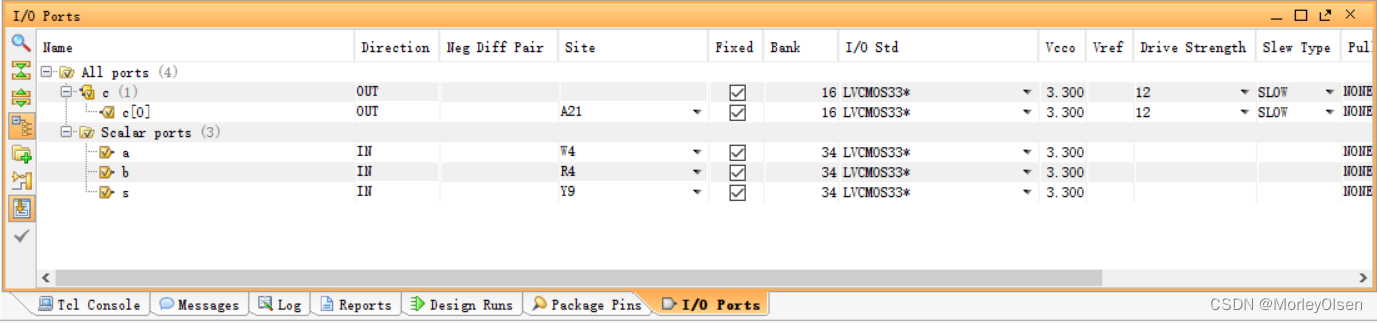

5:管脚分配 由于本实验不需要进行硬件实验,故2.2.1至此完毕

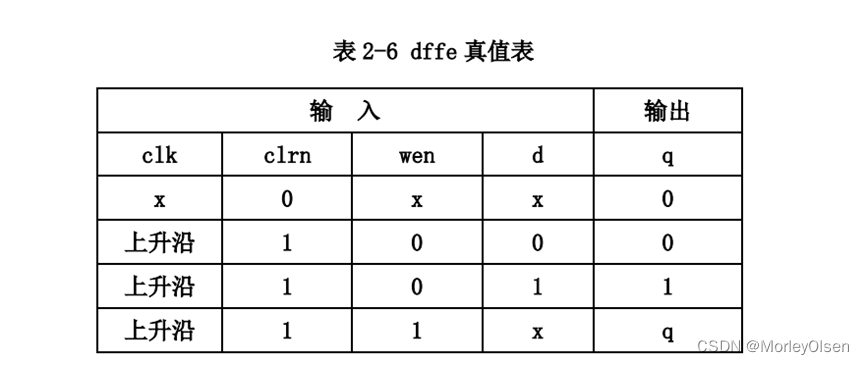

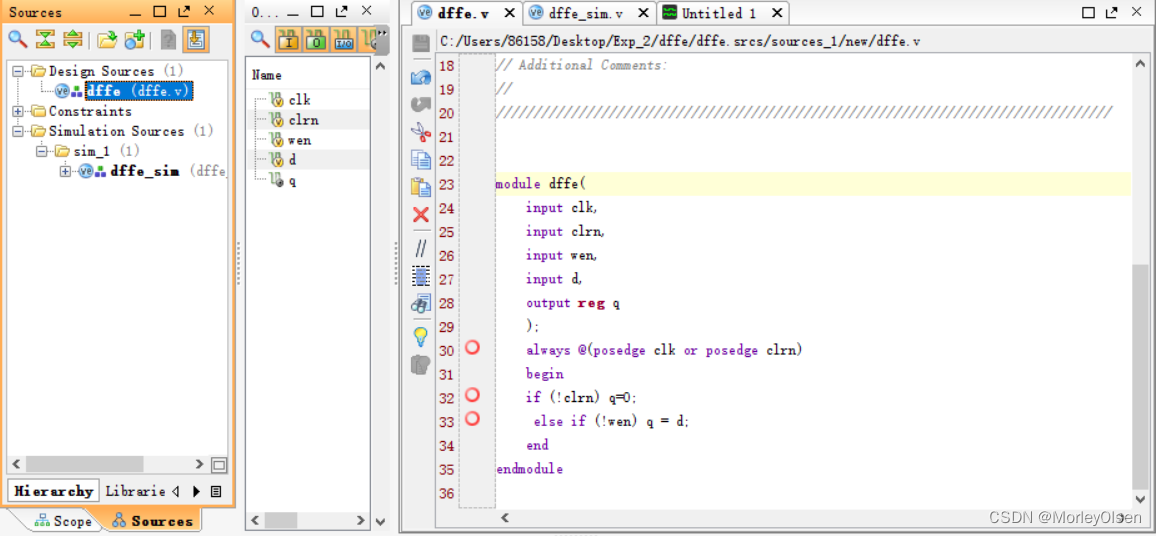

2.3.1 D触发器的设计 1:设置输入输出端口

2:编写源程序文件

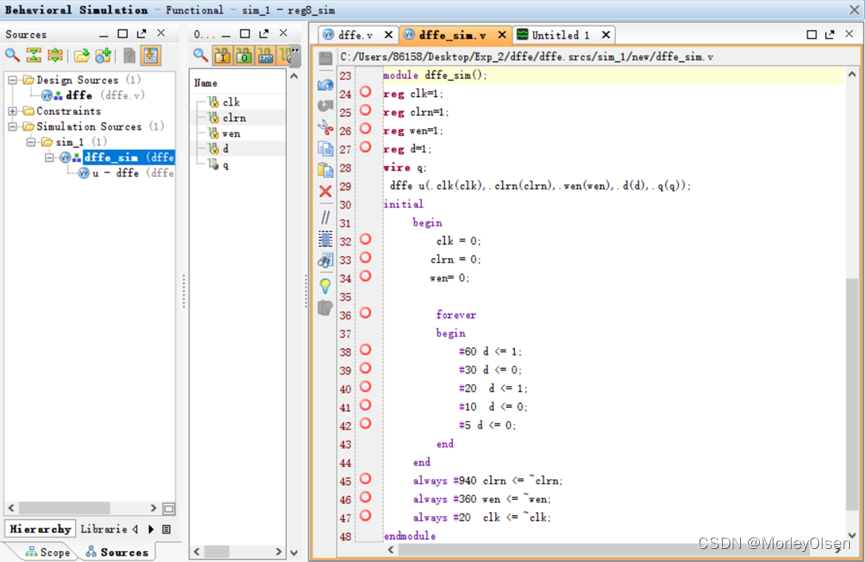

3:编写仿真程序文件

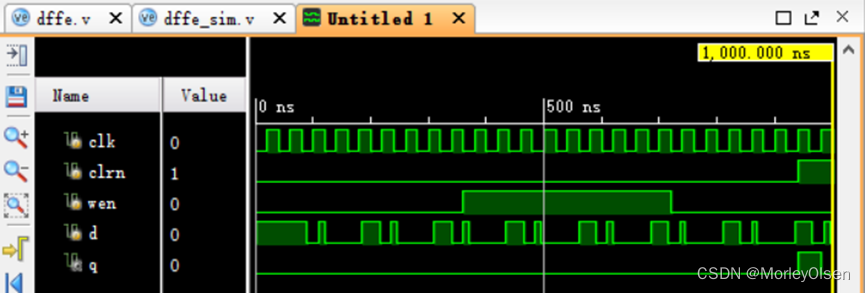

4 :仿真得到模拟图

四、分析Verilog 程序的功能,并编写仿真测试程序 源程序分析: module reg8( input clk, // 输入时钟信号 input clrn, // 输入清除信号 input wen, // 输入写使能信号 input [7:0] d, // 输入数据信号 output [7:0] q // 输出数据信号 ); reg [7:0] p; // 定义一个 8 位寄存器变量 p always @(posedge clk or negedge clrn) // 在时钟上升沿或清除信号下降沿时执行以下语句 if(!clrn) // 如果清除信号为 0 p |

【本文地址】

今日新闻 |

推荐新闻 |