FPGA实现FIR滤波器 |

您所在的位置:网站首页 › 滤波器如何实现滤波 › FPGA实现FIR滤波器 |

FPGA实现FIR滤波器

|

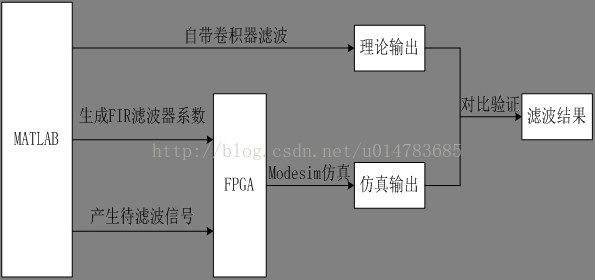

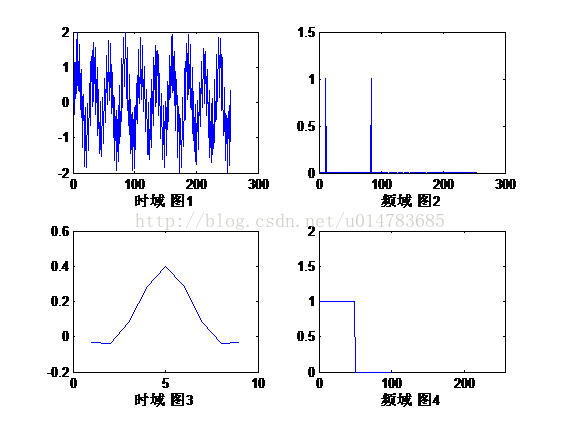

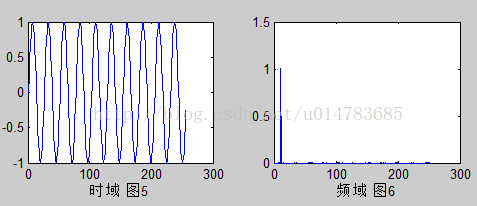

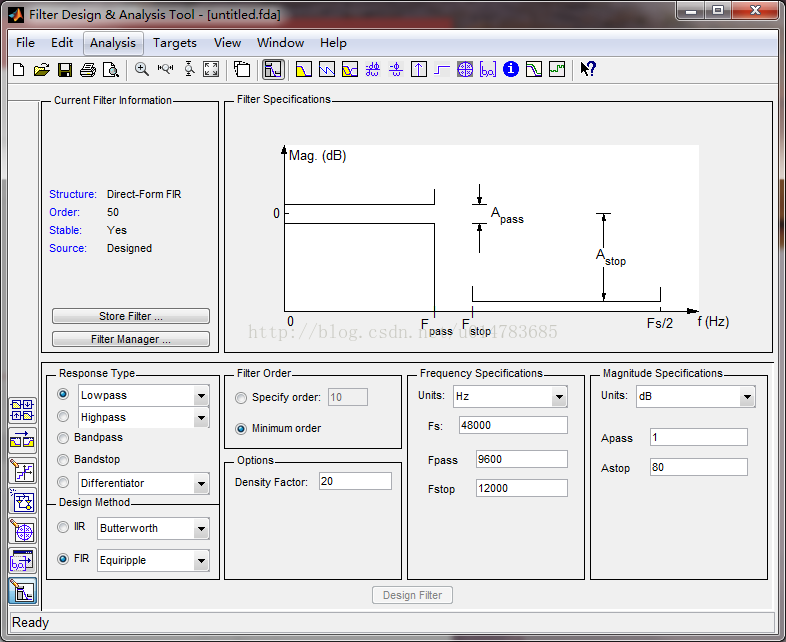

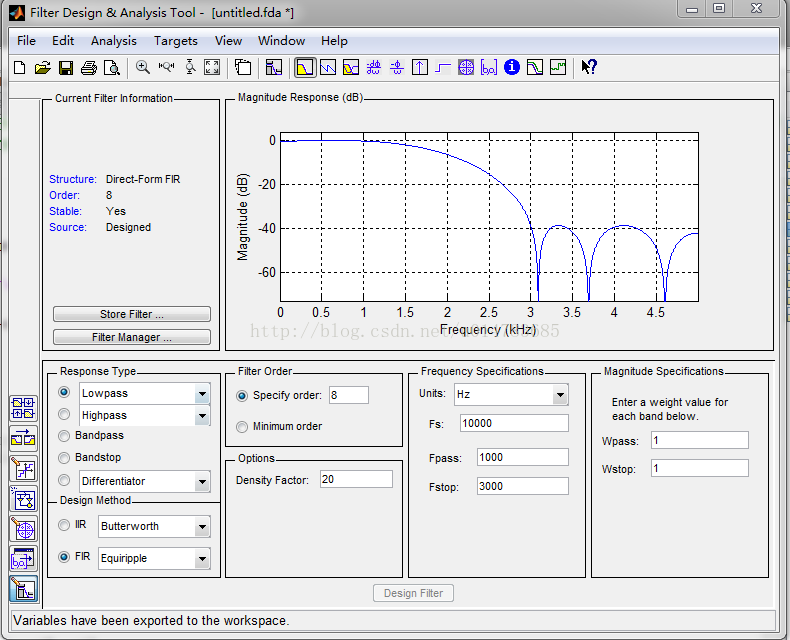

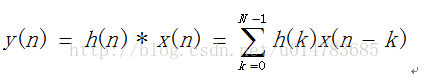

1、FIR滤波器总体设计 本设计是基于FPGA实现一个8阶的FIR数字低通滤波器。本次设计首先利用MATLAB中的FDAtool工具设计出一个采样频率为5KHZ、截止频率为1KHZ的FIR低通滤波器,通过FDAtool导出8点系数,然后将系数进行放大、取整,以便于在FPGA中使用,最后通过QuartusII进行Verilog语言编写滤波器算法,然后通过Modesim仿真结果和MATLAB仿真结果的比较来验证该滤波器的正确性。系统的总体设计框图如下: 首先由MATLAB生成一个由三个正弦波叠加的待滤波信号,三个正弦波的频率分别是1KHZ,3KHZ,4KHZ。然后将待滤波信号送入Modesim仿真,观察滤波后的波形,再利用MATLAB里面的conv函数将滤波器系数和待滤波信号卷积并观察滤波后的波形图,将Modesim的仿真结果和MATLAB的仿真结果比较并验证在FPGA中滤波器算法的正确性。 2、FIR滤波器原理 在学习数字信号处理时,滤波器是重点,数字滤波器有很多种,比如FIR、IIR、LMS等滤波算法,FIR (Finite Impulse Response)滤波器的特点是它的冲击响应是有限的,它跟过去的信号无关,所以在使用时容易实现,速度快。 要理解FIR滤波器,需要知道信号的频域跟时域的关系,信号的频谱就是信号在频域上的表现形式,如果一个信号由2个正弦波叠加(图1)而成,我们在时域是看不出什么规律的,将信号进行傅里叶变换到频域(图2),我们就可以 很清楚的看到该信号是由2个正弦波叠加而成的。 如果我们要对图1这个信号进行滤波,从频域上看,将信号的频谱乘以图4所示的矩形波,结果的频谱很显然就只剩下了低频段的这个正弦波,那么我们知道在频域和一个矩形波相乘就可以将高频滤出,在时域怎么做呢?我们学过信号与系统,知道频域卷积定理,这个定理的内容就是说:两个信号在频域相乘,那么在时域就相当于卷积,在时域相乘,在频域就相当于卷积。知道了这个定理,我们将图4的频域信号反变换到时域,变成图3所示的信号,我们将这个信号和图1的信号进行卷积,得到的结果就是图5所示的波形,这个波形的频谱如图6所示。这样我们便完成了对信号的滤波。MATLAB中的FDAtool就是用来根据需要的滤波器生成图3所示的滤波器系数。 3、MATLAB生成信号 3.1滤波器系数设计 在MATLAB中输入fdatool即可打开滤波器设计工具,如图7所示。里面可以设置滤波器的类型,采样频率,截止频率等。本设计设置的参数如图8所示。

图7

图8 然后将此滤波器系数导出,然后用以下命令将系数放大、取整: >> Num

Num =

-0.0325 -0.0384 0.0784 0.2874 0.3984 0.2874 0.0784 -0.0384 -0.0325

>> Num=round(Num*400)//将系数放大并取整

Num =

-13 -15 31 115 159 115 31 -15 -13

>> Num=Num+20//将系数符号变成正的,便于FPGA使用

Num =

7 5 51 135 179 135 51 5 7

最终生成的系数Num即可用于FPGA进行FIR滤波器实现。

3.2 待滤波信号的设计 本设计用于仿真的输入波形是三个正弦波叠加而成,分别是1KHZ、3KHZ、4KHZ。下面是用于生成待滤波信号的m文件内容:

%*********产生.data文件 用于FPGA仿真************%

Fs = 10000; %采样频率决定了两个正弦波点之间的间隔 N = 4096; %采样点数 N1 = 0 : 1/Fs : N/Fs-1/Fs;

s = sin(1000*2*pi*N1) + sin(3000*2*pi*N1) +sin(4000*2*pi*N1);//三种正弦波

fidc = fopen('D:\FPGA\FIR\mem.txt','wt'); //将结果写入mem.txt文件,便于modesim使用 for x = 1 : N fprintf(fidc,'%x\n',round((s(x)+2.12)*58)); end fclose(fidc); 4、FPGA实现FIR算法 实现FIR滤波器的过程其实就是实现卷积的过程,卷积的公式如下,从如下公式 中可以看出,x(n)是我们的待滤波信号,h(n)是滤波器系数,卷积的过程其实就是一个乘、累加的过程,所以用FPGA实现8阶FIR滤波器的主要分成三级流水线,第一级、将输入信号延时,这样才能将信号和滤波器系数相乘。第二级、将输入信号和系数相乘。第三级、将乘积进行累加得到结果。 第一级流水线的实现代码如下: reg[7:0] delay_pipeline1 ; reg[7:0] delay_pipeline2 ; reg[7:0] delay_pipeline3 ; reg[7:0] delay_pipeline4 ; reg[7:0] delay_pipeline5 ; reg[7:0] delay_pipeline6 ; reg[7:0] delay_pipeline7 ; reg[7:0] delay_pipeline8 ; reg[7:0] delay_pipeline9 ; always@(posedge CLK or negedge RSTn) if(!RSTn) begin delay_pipeline1 |

【本文地址】

今日新闻 |

推荐新闻 |