CMOS逻辑门电路的重要技术参数 |

您所在的位置:网站首页 › 模拟集成电路主要有哪些 › CMOS逻辑门电路的重要技术参数 |

CMOS逻辑门电路的重要技术参数

|

目录

1. 输入和输出的高、低电平2. 噪声容限3. 传输延迟时间4. 功耗5. 延时-功耗积6. 扇入与扇出数

1. 输入和输出的高、低电平

2. 噪声容限

表示门电路的抗干扰能力。 噪声容限越大,门电路的抗干扰能力越强; 噪声容限越小,门电路的杠杆人能力越差。

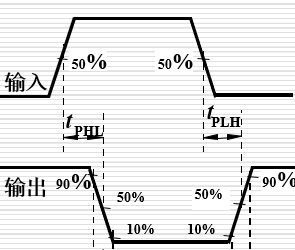

高电平的噪声容限为当驱动门输出高电平时,容许叠加在其上的负向噪声电压的最大值。一旦噪声电压大于这个值,负载将无法被驱动。 低电平的噪声容限: V N L = V I L ( m i n ) − V O L ( m i n ) V_{NL} = V_{IL(min)} - V_{OL(min)} VNL=VIL(min)−VOL(min) 低电平的噪声容限为当驱动门输出低电平时,容许叠加在其上的正向噪声电压的最大值。一旦噪声电压大于这个值,负载将仍保持被驱动状态,无法截止。 3. 传输延迟时间表示门电路的开关速度。 说明门电路在输入脉冲波形的作用下,其输出波形相对于输入波形延迟了多长时间。

平均传输延时时间: t p d = t p L H + t p H L 2 t_{pd} = \frac{t_{pLH}+t_{pHL}}{2} tpd=2tpLH+tpHL 4. 功耗 5. 延时-功耗积D P = t p d P D DP = t_{pd} P_{D} DP=tpdPD 6. 扇入与扇出数

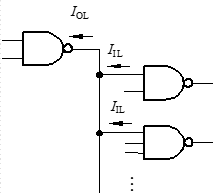

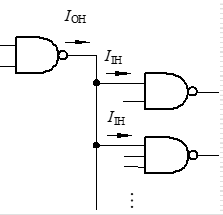

N O H = I O H ( 驱 动 门 ) I I H ( 负 载 门 ) N_{OH} = \frac{I_{OH}(驱动门)}{I_{IH}(负载门)} NOH=IIH(负载门)IOH(驱动门) 驱动门的输出端为低电平,当负载门的个数增加,IOL增大,输出低电平降低,但不得低于输出低电平的上限,所以带最多负载的个数: N O L = I O L ( 驱 动 门 ) I I L ( 负 载 门 ) N_{OL} = \frac{I_{OL}(驱动门)}{I_{IL}(负载门)} NOL=IIL(负载门)IOL(驱动门) 如果 N O L ≠ N O H N_{OL} ≠ N_{OH} NOL=NOH,取两者的最小值。 |

【本文地址】

今日新闻 |

推荐新闻 |

高电平的噪声容限:

V

N

H

=

V

O

H

(

m

i

n

)

−

V

I

N

(

m

i

n

)

V_{NH} = V_{OH(min)} - V_{IN(min)}

VNH=VOH(min)−VIN(min)

高电平的噪声容限:

V

N

H

=

V

O

H

(

m

i

n

)

−

V

I

N

(

m

i

n

)

V_{NH} = V_{OH(min)} - V_{IN(min)}

VNH=VOH(min)−VIN(min)

驱动门的输出端为高电平,当负载门的个数增加,IOH增大,输出高电平降低,但不得低于输出高电平的下限,所以带最多负载的个数:

驱动门的输出端为高电平,当负载门的个数增加,IOH增大,输出高电平降低,但不得低于输出高电平的下限,所以带最多负载的个数: