【数字集成电路】第六章 CMSOS组合逻辑门的设计 |

您所在的位置:网站首页 › 反相器的阈值电压定义为 › 【数字集成电路】第六章 CMSOS组合逻辑门的设计 |

【数字集成电路】第六章 CMSOS组合逻辑门的设计

|

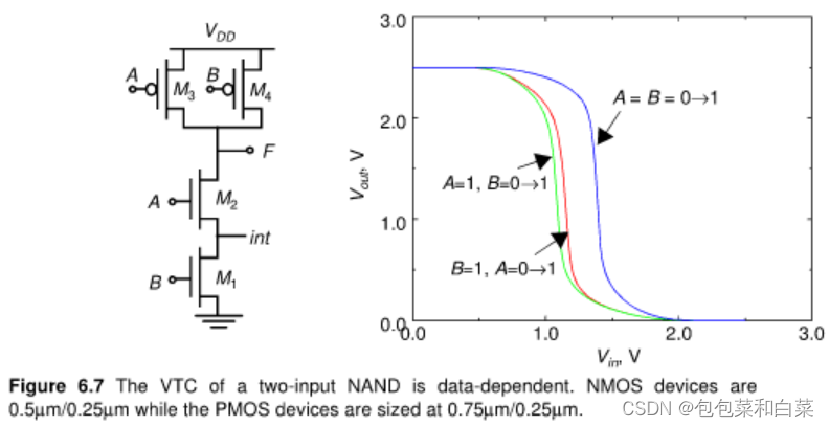

目录 6.1引言 6.2静态CMOS设计 6.2.1互补CMOS 6.2.1.1概念 6.2.1.2静态特性 6.2.1.3传播延时 6.2.1.4组合电路中的性能优化 6.2.1.5CMOS逻辑门中的功耗 6.2.2有比逻辑 6.2.3传输管逻辑 6.3动态CNMOS设计 6.3.1动态逻辑:基本定理 6.3.2动态逻辑的速度和功耗 6.3.3动态设计中的信号完整性问题 6.3.4串联动态门 6.4设计综述 6.4.1如何选择逻辑类型 6.4.2低电源电压的逻辑设计 6.5小结 6.6进一步探讨 6.1引言 6.2静态CMOS设计静态电路:每一个时刻,门的输出通过一条低阻通路连到VDD或是GND。 6.2.1互补CMOS 6.2.1.1概念1、PDN由NMOS器件构成,而PUN由PMOS管构成,这一选择的主要理由是NMOS管产生“强0”而PMOS器件产生“强1”。 2、NMOS器件串联相当于“与”(A∙B )功能。NMOS管的并联代表“或”(A+B)操作。PMOS网络的规则:如果两个输入都低,串联的两个PMOS都导通,这代表一个NOR操作, 而PMOS 管并联实现NAND操作。 3、这一互补门在本质上是反相的,只能实现如NAND、NOR及XNOR这样的功能,用单独一级来实现非反相的布尔函数(如AND、OR或XOR)是不可能的,因此要求增加额外一 级反相器。 4、实现一个具有N个输入的逻辑门所需要的晶体管数目为2N。 6.2.1.2静态特性一、VTC 互补CMOS组合逻辑门的DC电压传输特性和噪声容限(静态特性)的分析比反相器要复杂,因为这些参数取决于加在这个门上的数据输入模式。 有三种可能的输入组合可以使该门的输出从高切换至低: (a)A=B = 0→1 (b)A= 1,B=0→1 (c)B=1,A = 0→1

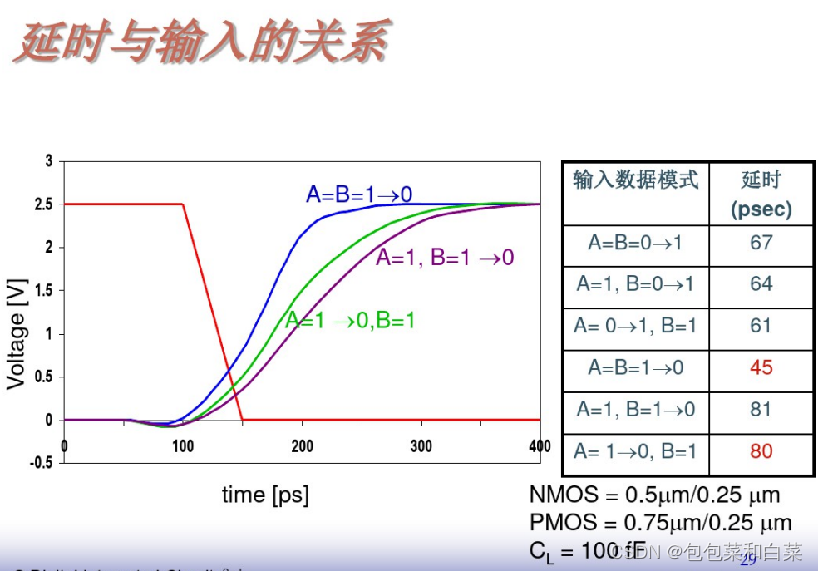

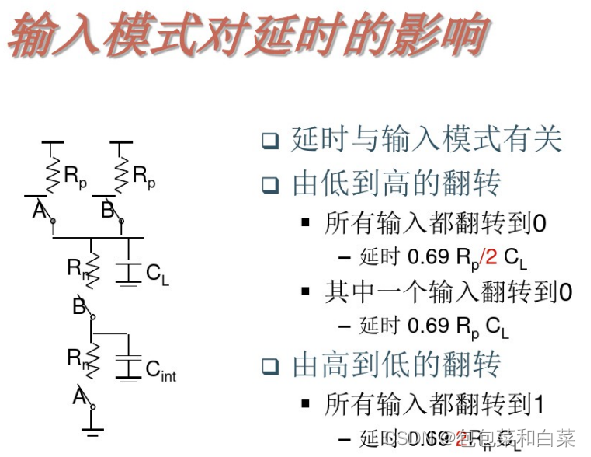

(a)处于上拉网络的两个晶体管由于而同时导通,这代表很强的上拉。 而(b)和(c)两个上拉器件中只有一个导通。因此PUN较弱的结果使VTC左移。(b)和(c)之间的差别主要来自于两个NMOS器件的阈值电压由于受到体电荷效应的影响不一样而产生的。(c有体电荷效应) 6.2.1.3传播延时一、延时与输入模式有关

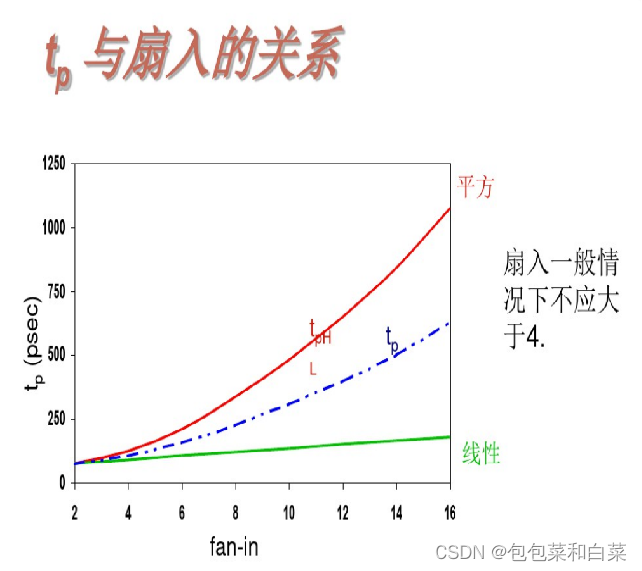

二、延时与扇入的关系

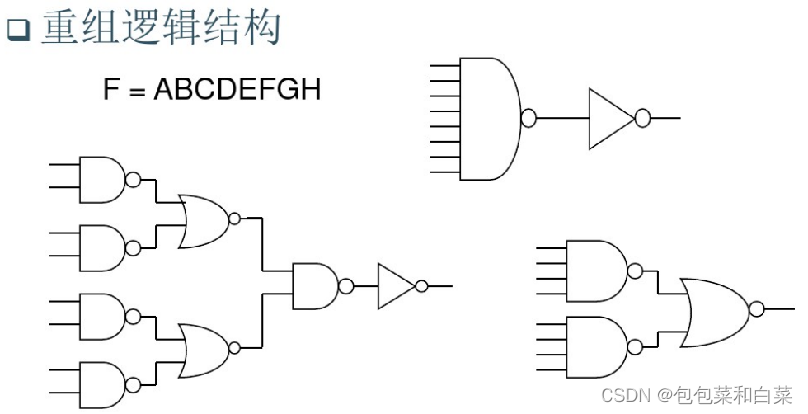

虽然互补CMOS是一种实现逻辑门的非常有效和简单的方法,但随着门复杂性(即扇入)的 增加,采用这一逻辑类型时会出现两个主要问题。 首先,实现一个有N个输入(扇入)的门需要 晶体管的数目为2N,这会明显加大它的实现面积。 第二,互补CMOS门的传播延时随扇入数迅速 增加。事实上,一个门的无负载本征延时在最坏情况下是扇入数的二次函数(平方关系,因为扇入增加,电阻和电容同时增加)。 或非门p管串联会延时更严重,因为p管尺寸同样条件下比n管大。 三、大扇入时的设计技术 (1)、加大晶体管的尺寸: 这能降低串联器件的电阻和减小时间常数,但是晶体管尺寸的增加会产生校大的寄生电容,这不仅会增加该门的传播延时,还会对前一级的门产生一个较大的负载。因此在采用这一技术时应当小心。如果负载电容主要是门自身的本征电容,则加宽器件只会增加“自载”效应,对传播延时将不产生影响。只有当负载以扇出为主时放大尺寸才起作用。 (2)、逐级加大晶体管尺寸: 能够将延时减少20%以上 (3)、重新安排输入: 在复杂组合逻辑块中有一些信号可能要比其他一些信号更重要。一个门的所有输入并不都在同一时间到达(例如,由于前级门的传播延时不同)。如果门的一个输入信号在所有输入中最后达到稳定值,那么这个输入信号就称为这个门的关键信号。决定这个结构最终速度的逻辑路径称为关键路径。把关键路径上的晶体管靠近门的输出端可以提高速度。 (4)、重组逻辑结构:

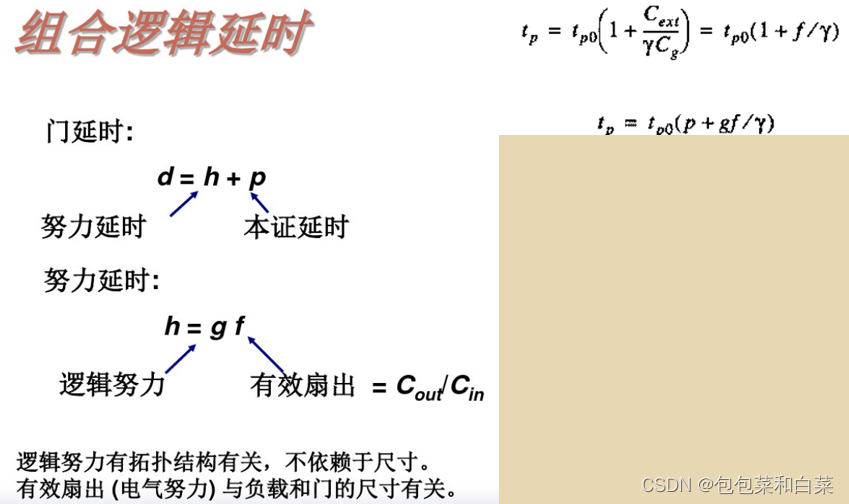

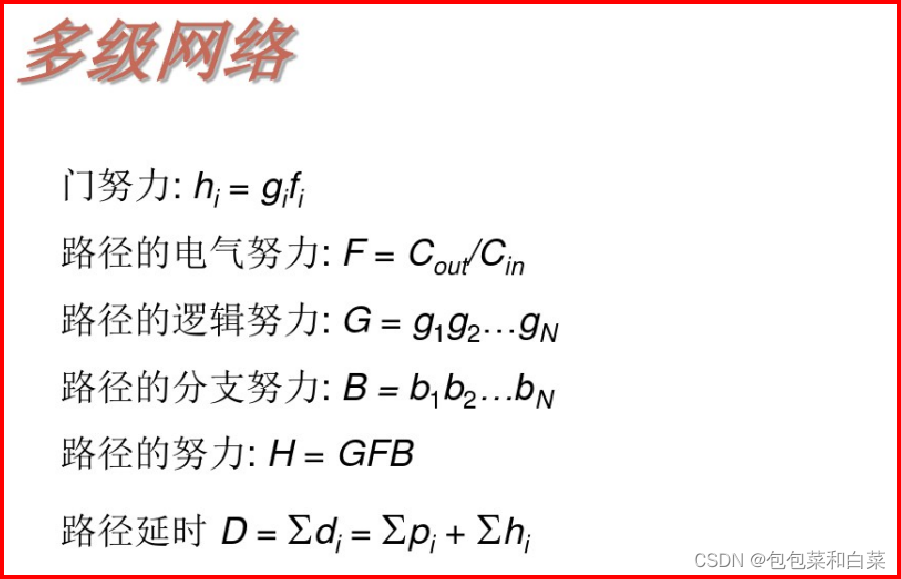

一、逻辑努力 这里指多个组合逻辑电路的级联。

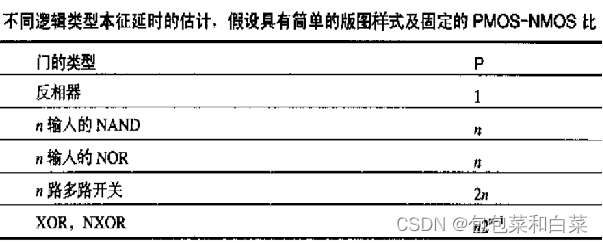

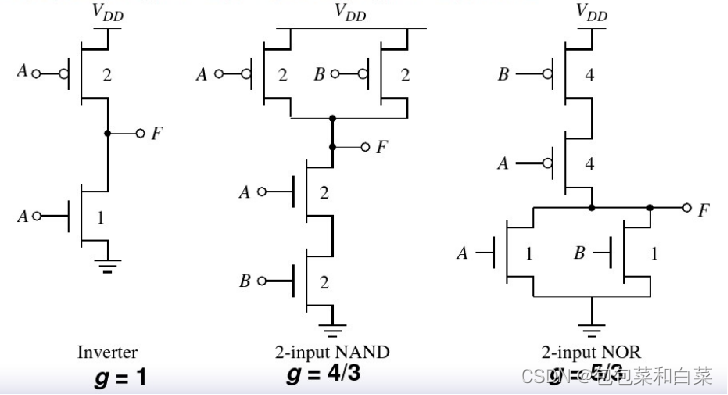

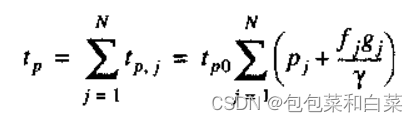

式中,tp0仍代表反相器的本征延时.f为等效扇岀,它定义为该门的外部负载和输入电容之间的比。这里f又称为电气努力(electrical effort ),p代表该复合门和简单反相器的本征(即无负载) 延时的比,它与门的拓扑结构以及版图样式有关。系数g称为逻辑努力(logical effort)。它代表了这样一个事实,即对于一给定负载,复合门必须比反相器更“努力”工作才能得到类似的响应。逻辑努力表示一个门与一个反相器提供相同的输出电流时它所表现出的输入电容是反相器多少倍。

二、 门努力:扇出和逻辑努力是以 类似的方式来影响延时的。我们称这两者的积h=f∙g称为门努力(gate effort)。 三、延时整体概述

四、一条组合逻辑路径各个参数(求级联链最小延时时应该怎样设计尺寸) (1)总延时

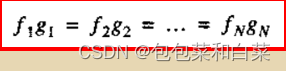

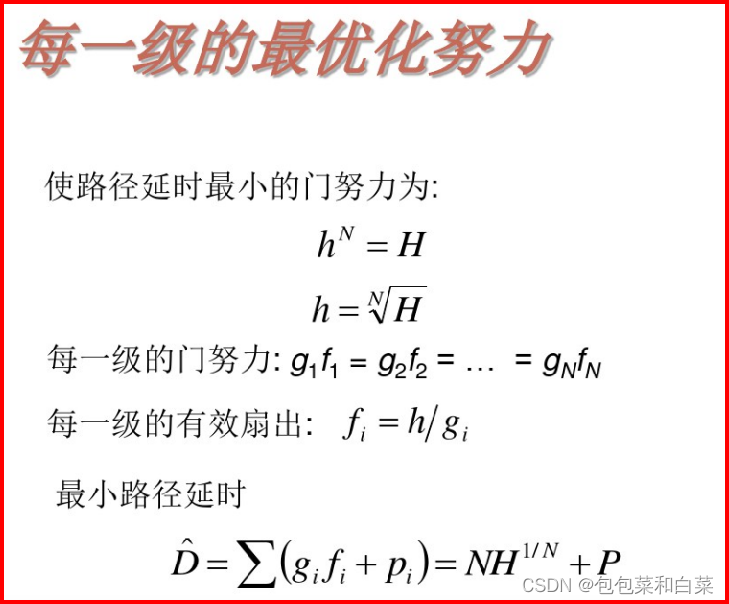

(2)类似于反相器链,总延时最小时,各个级的扇出(门努力)相同,即

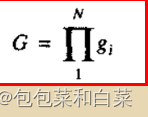

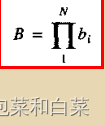

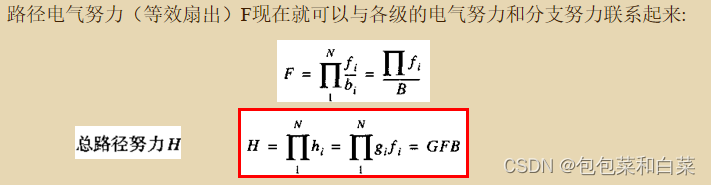

(3)路径总努力 (4)分支努力与路径分支努力

(5)总电气努力、分支努力、总努力

总的电气努力很大,但是有一些电气努力在分支路径上跑掉了,有效的为 (6)最小延时时,各个门的努力应该相等,

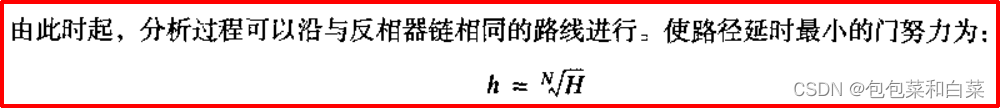

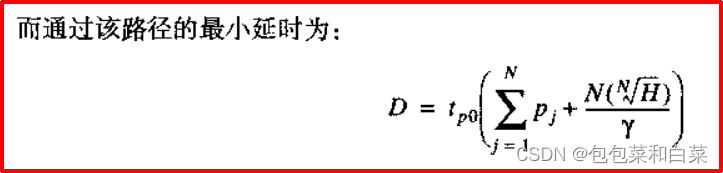

(7)最小延时

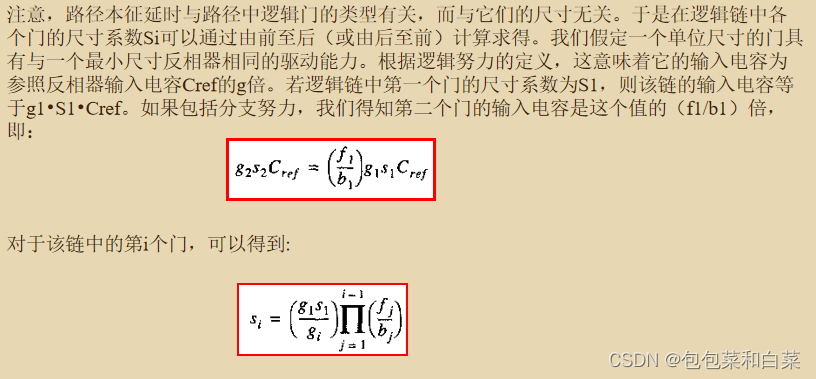

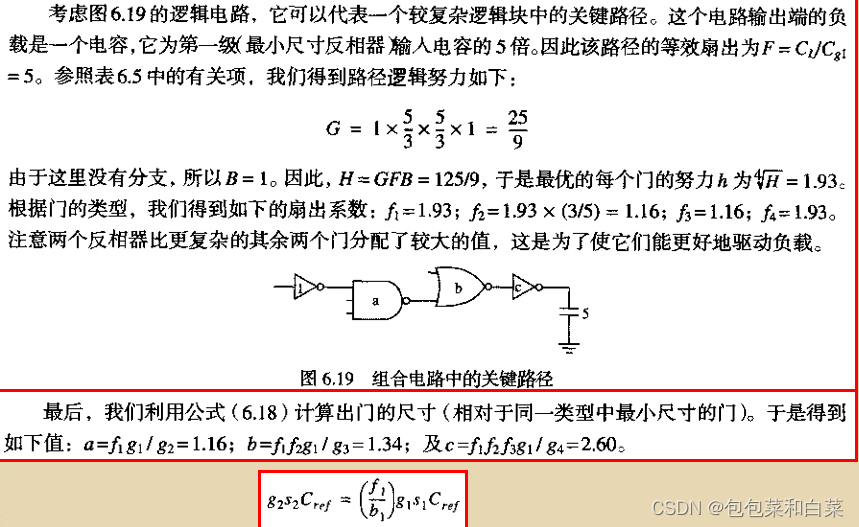

(8)根据门努力,门的逻辑努力(与尺寸无关)求门的电气努力(为电容比,与尺寸有关,还与前级有关),进而求尺寸系数

(9)小结

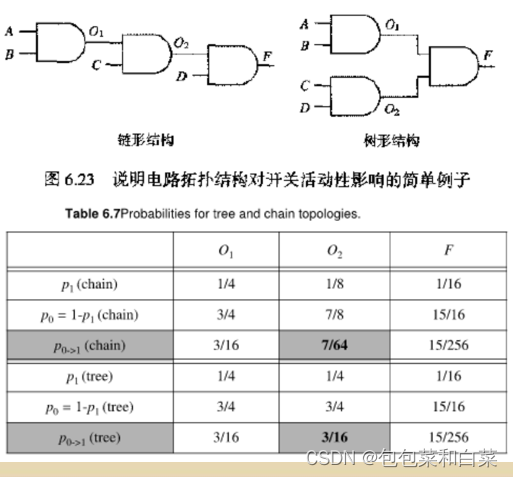

一、翻转活动性 前一级位0,后一级为1的概率, 降低翻转活动性的方法: (1)、逻辑重组 结果表明对于随机输入,链形实现比树形实现总体上具有较低的开关活动性。

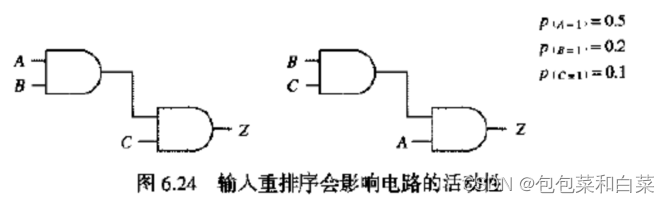

(2)输入排序 推迟输入具有较高翻转率的信号是有利的。

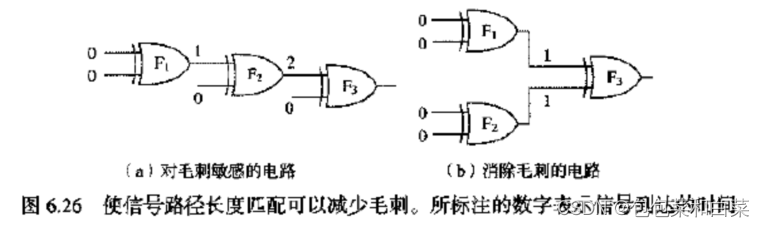

(3)分时复用资源 (4)通过均衡信号路径来减少毛剌 电路中产生毛剌主要是由于在电路中路径长度失配引起 的。如果一个门的所有输入信号同时改变,那么就不会发生毛刺。反之,如果各输入信号在不同的时刻变化,那么就有可能形成动态故障。信号时序上的这一失配一般都是由于相对于电路的原始输入信号路径的长度不同而引起的。

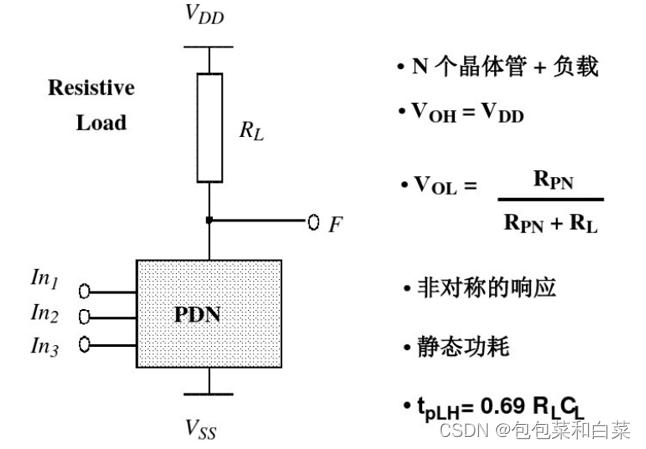

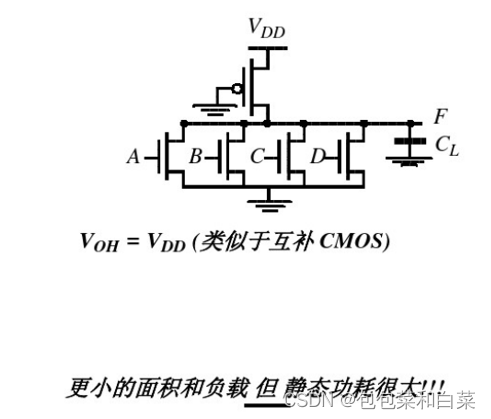

目标:减少实现一个给定逻辑功能所需要的晶体管数量,但它经常以降低稳定性和付出额外功耗为代价。 一、电阻负载有比逻辑

二、伪nmos有比逻辑

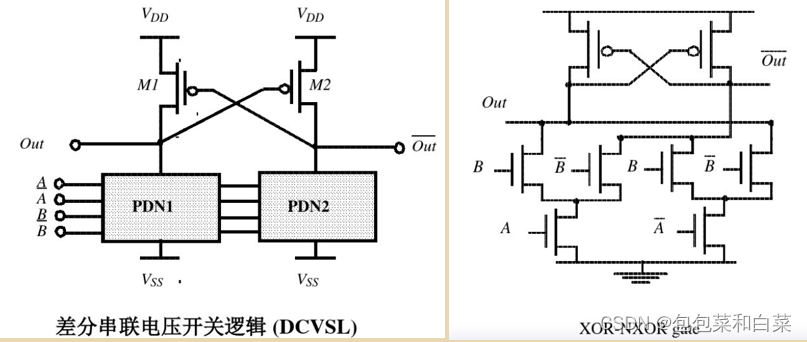

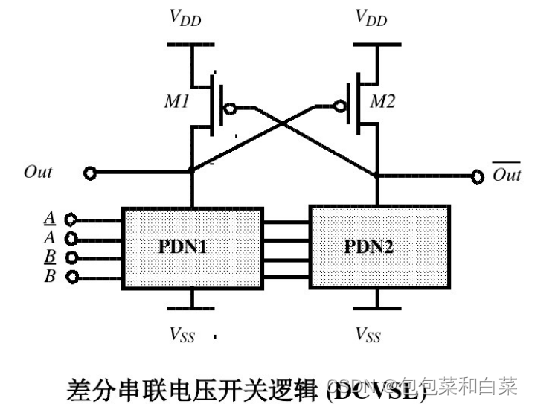

一个较大的上拉器件不仅提高了性能(减少了延时),同时也由于增加了VOL而使静态功耗增加和噪声容限减小。伪NMOS的静态功耗限制了它的应用。当然在面积是最重要因素时,与互补CMOS相比,它能减少晶体管的数目,这一点还是非常吸引人的。因此,仍然可以看到伪NMOS有时应用在大扇入电路中。 三、差分串联电压开关逻辑DCVSL 建立一个能够完全消除静态电流和提供从电源轨线至轨线电压摆幅的有比逻辑方式是可能的。 这样的一个门同时利用了两个槪念:差分逻辑和正反馈。一个差分门要求每一个输入都具有互补的形式,同时它也产生互补的输出。反馈机制保证了在不需要负载器件时将其关断.这样的 逻辑系列称为差分串联电压开关逻辑DCVSL。

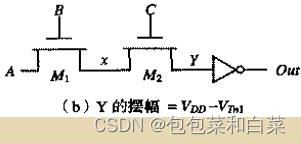

下拉网络PDNI和PDN2采用NMOS器件,并且两者是互相排斥的,也就是当PDN1导通时 PDN2关断;当PDN1关断时PDN2导通,这样同时实现了所需要的功能和与它相反的功能。现在假设对于给定的一组输入,使PDN1导通而PDN2不导通,而out和out'最初分别为高电平和低电平,PDN1导通则引起out下拉,虽然在M1和PDN1之间仍存在竞争。由于M2和PDN2关断,out'处于高阻抗状态,PDN1必须足够强使out以低于VDD-|Vtp|,此时也导通并开始对out'充电至Vdd,最终将M1关断.这又使out放电至GND。 这一电路类型还有因渡越电流所引起的功耗问题,在翻转期间 PMOS和PDN会同时导通一段时间,从而产生一条短路路径。 6.2.3传输管逻辑它通过允许原始输入驱动栅端和 源-漏端来减少实现逻辑所需要的晶体管数目。 一、 不能将一个传输管的输出连接到另一个传输管的输入来实现传输營门 的串联。

串联传输门的正确方法:

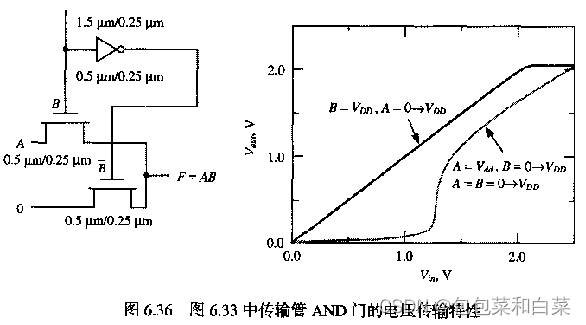

二、传输管AND门

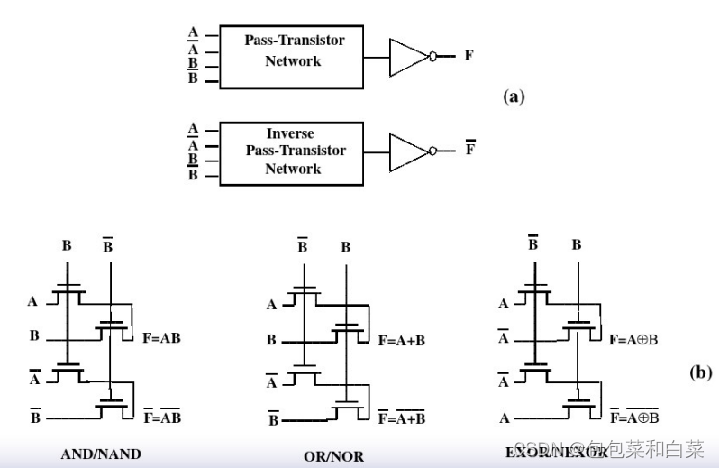

三、差分传输管逻辑CPL

特点:1.由于电路是差分方式,所以总是存在互补的数据输入和输出。尽管产生差分信号要求额外的电路,但差分方式的优点是某些复杂的门(如XOR和加法器)可以有效地用少量的晶体管来实现。而且由于每个信号的两种极性都存在,所以不像在静态CMOS或伪NMOS中的 情形那样经常需要额外的反相器。 2.CPL属于静态门类型,因为定义为输出的节点总是通过一个低阻路径连到VDD或GDN。 3.CPL的设计具有模块化的特点 ,它所有的门都采用完全相同的拓扑结构 只是输入的排列不同而已。这使得这类门单元库的设计非常简单,较复杂的门可以通过串联标准 的传输管模块来构成。 四、差分管CPL的应用

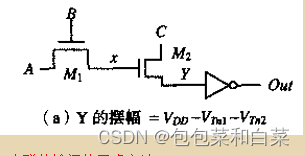

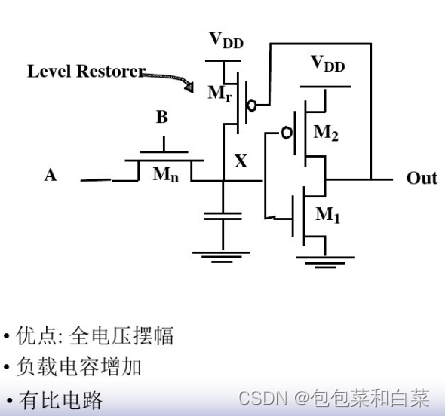

五,电平恢复器

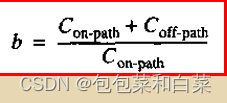

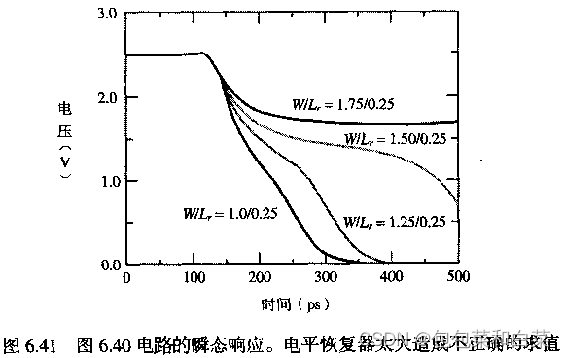

这个电路 的优点是所有电平不是处在GND就是处在VDD上,因此没有任何静态功耗。 它是有比电路.这 一问题发生在节点X由高至低的翻转期间,传输管电路试图下拉节点X,而电平恢复器却要把X上拉到VDD。因此,由Mn代表的下拉电路必须强于上拉器件Mr以切换节点X(以及输出)。为使这个电路正确工作:必须仔细确定晶体管的尺寸,假设分别用R1, R2,Rr表示晶体管 M1,M2,Mr的等效导通电阻。当Mr太小时就不能使节点X的电压低于反相器的开关阈值。因此反相器的输出永远不会切换到VDD。该门就锁定在了一个状态 。这一问题可以通过调整Mn和Mr管的尺寸来解决.使节点X的电压降到低于反相器的阈值VM,VM与R1和R2有关。 电平恢复器对器件切换速度的影响:增加恢复器器件就增加了内部节点X上的电容,从而减慢了这个门的速度。此外门的上升时间也受到负面影响。电平恢复晶体管Mr在被关断之前要阻止节点X处的电压下降。反之,电平恢复器将减少下降时间,因为PMOS管一旦导通, 就会加速上拉作用。 六、电平恢复器的尺寸有上限

Mn和Mr形成了一个类似伪NMOS 的结构,其中Mr为负载管,而Mn的作用是一个接地(GND)的下拉网络。 假设反相器的M1和M2 的尺寸确定为使其开关阈值为VDD/2(NM0S: 0.5 um/0.25um, PMOS: 1.5um/0.25um)。因此节点X必须被下拉至 VDD/2才能切换反相器并关断。 七、多种阈值晶体管

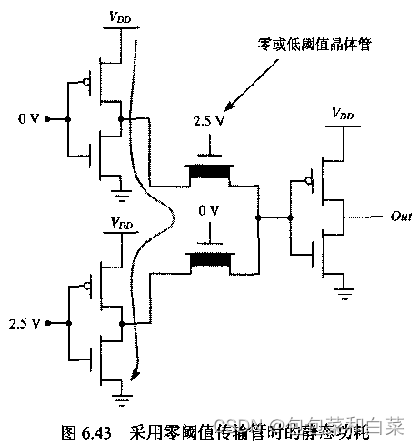

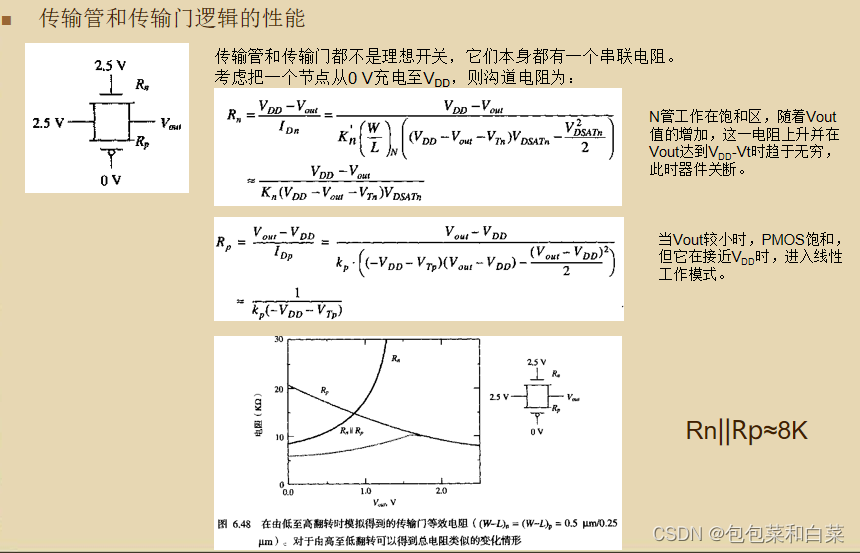

在工艺上解决传输管逻辑电压损失问题的一种方法是采用具有多种阈值的器件。使用零阈值器件的NMOS传输管可以消除大部分阈值损失,因面传送的信号接近VDD。 所有非传输管的器件(即反相器)都用标准的高阈值器件实现。采用多种阈值的晶体管已经 越来越普遍,只需对现有的工艺流程进行简单的改造.但要注意,即便非常小心地调整器件的注入以产生准确的零阈值,器件的体效应仍然会阻止全摆幅达到VDD。 采用零阈值晶体管对功耗有负面影响,这是由于即使Vgs低于Vt也仍然会有亚阈值电流流过传输管。 八、传输门 虽然传输门需要两个晶体管和较多的控制信号,但它能得到从电源至地的摆幅。 传输门可以用来非常有效地构成某些复杂的门。一个简单的反相两输入多路开关。 九、传输门——性能——延时 (1)等效电阻

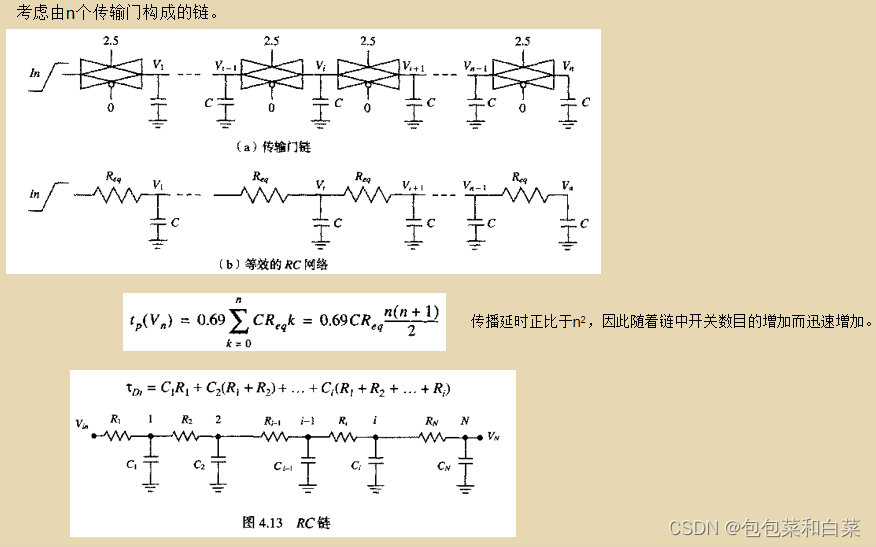

电阻变化量小,可认为基本不变。 (2)传输门链

传播延时正比于开关数目的平方。越往后的传输门等效的电阻越大(线性增大)。 十、解决传输门链延时的方法 解决由n个传输门构成的链长延时问题最常用的办法是每隔m个传输门开关切断串联链并插入一个缓冲器。 每两个传输门插入一个反相器时模拟得到的延时为154 ps;每三个传输门插入一个反相器时延时为154ps;而每四个传输门时为164ps。插入缓冲反相 器使延时缩短将近2倍。 6.3动态CNMOS设计 6.3.1动态逻辑:基本定理

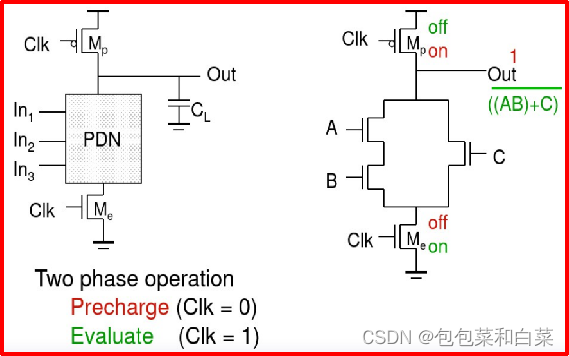

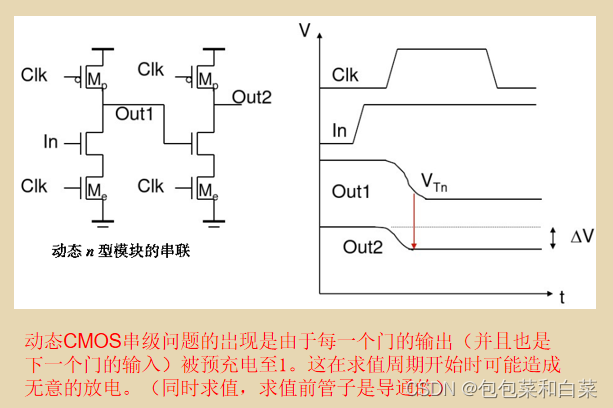

预充电 :当CLK = 0时输出节点Out被PMOS预充管Mp预充电至VDD。在此期间NMOS求值管Me关断,无静态功耗。 求值 :当CLK=1时预充电管Mp关断。求值管Me导通,输出根据输入值和下拉拓扑结构的情况有条件地放电求值。 CL是结电容,引线电容以及扇出门输入电容的组合 。 一个时钟周期包含一次预充电-放电过程,Out只能放电一次,下次放电只能在下一个周期预充电以后。因此门的输入在求值期间最多只能有一次変化。 特点: (1)逻辑功能由NMOS下拉网络实现,构成PDN的过程与静态CMOS完全一样。 (2)晶体管的数目(对于复杂门)明显少于静态情况:为N + 2而不是2N。 (3)是无比的逻辑门。PMOS预充电器件的尺寸对于实现门的正确功能并不重要。预充电器件的尺寸可以较大以改善低至高的翻转时间(当然,这是以由高至低的翻转时间为代价的)。 然而这里还有一个权衡功耗的问题,因为较大的预充电器件会直接增加时钟的功耗。 (4)动态逻辑门只有动态功耗。理想情况下在Vdd和GND之间从不存在任何静态电流路径。但是它的总功耗还是可以明显高于静态逻辑门。 (5)动态逻辑门具有较快的开关速度,主要有两个原因。第一个(明显的)原因是由于减少了 每个门晶体管的数目,并且每个扇入对前级只表现为一个负载晶体管,因而降低了负载电容,这相当于降低了逻辑努力。例如,一个两输入动态NOR门的逻辑努力是2/3,大大小于相应静态CMOS门的5/3。第二个原因是动态门没有短路电流,并且由下拉器件提供的 所有电流都用来对负载电容放电。 (6)利用对偶的方法可以实现P型动态逻辑。 6.3.2动态逻辑的速度和功耗动态逻辑的主要优点是提高了速度和减少了实现面积。用较少的器件来实现一个指定的逻辑 功能意味着总的负载电容要小得多。对这个门开关特性进行分析,发现它有一些有趣的特点。在预充电阶段之后,输岀为高电平。对于低电平输入信号,没有任何另外的切换发生。结果 TPLH=0,反之,由高至低的翻转要求通过下拉网络放电输出电容。因此,TPHL与CL以及下拉网结的放电电流能力成正比。求值管的存在多少会减慢门的速度,因为它相当于一个额外的串联电阻。去掉这个晶体管虽然对功能无妨碍,但可能会造成静态功耗及潜在的性能损失。 动态逻辑在功耗方面有明显的优势。 这主要有三个原因。 第一,它的实际电容较小,因为动态逻辑使用较少的晶体管来实现指定的功能。同时从每个扇出看到的负载是一个而不是两个晶体管。为什么?????????? 第二,由于动态门的结构使得每个时钟周期最多只能翻转一次。毛刺(或动态故障)在动态逻辑中并不发生。 最后,动态门不存在短路功耗,因为它在求值时上拉路径不导通。 6.3.3动态设计中的信号完整性问题一、电荷泄露 亚阈值电流和二极管反向饱和电流。

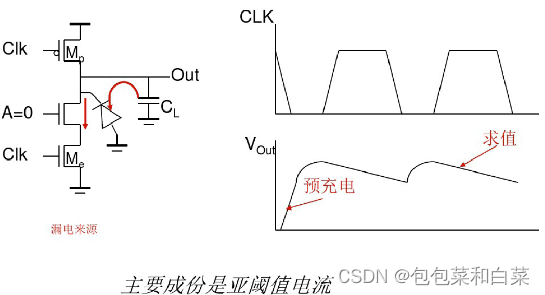

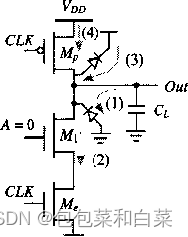

一个动态门的工作取决于输出值在电容上的动态存储。 漏电来源1和来源2分别为NMOS下拉器件M1的反偏二极管和亚阈值漏电。存储在CL上的电荷将通过这些漏电渠道慢慢泄漏掉,使高电平变差。因此动态电路要求一个最低的时钟频率,一般在几千赫兹左右。 注意,由于它的反偏二极管(漏电 来源3)和亚阈值导电(漏电来源4), PMOS预充电器件也引起一些漏电流。在某种程度上,PMOS 的漏电电流抵消了下拉路径的漏电。因此,输出电压将由下拉和上拉路径构成的电阻分压器来确定。 解决方法:

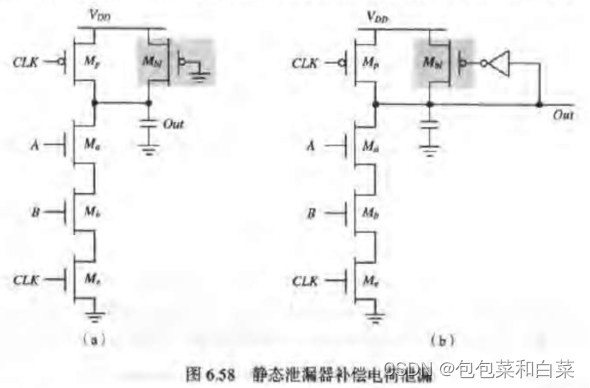

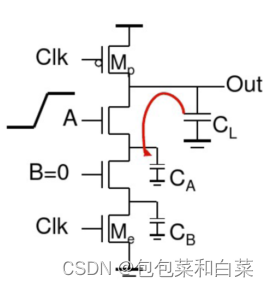

在求值期间.当下拉路径关断时由于输出节点处于高阻状态,因此引起了漏电。漏电问题可以通过降低求值期间输出节点上的输出阻抗来解决。通常是增加一个泄漏晶体管。如图6.58 (a) 所示,该泄漏器为一个伪NMOS型的上拉器件,用来补偿由于下拉漏电路径造成的电荷损失。为了避免出现与这类电路相关的尺寸比问题及相关的静态功耗。可以使泄漏器的电阻较高(换种说 法,就是使器件较小):这就使下拉器件能够下拉节点Out的电压,使它充分低于下一级门 的开关阀值, 通常泄漏器以反馈形式实现,以同时消除静态功耗。 二、电荷分享 轻则影响静态功耗,重则引起错误翻转。

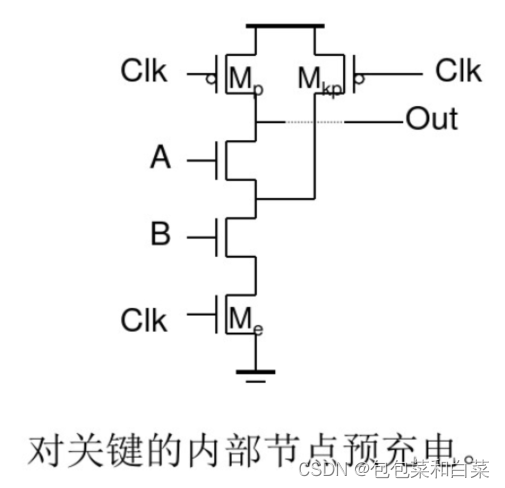

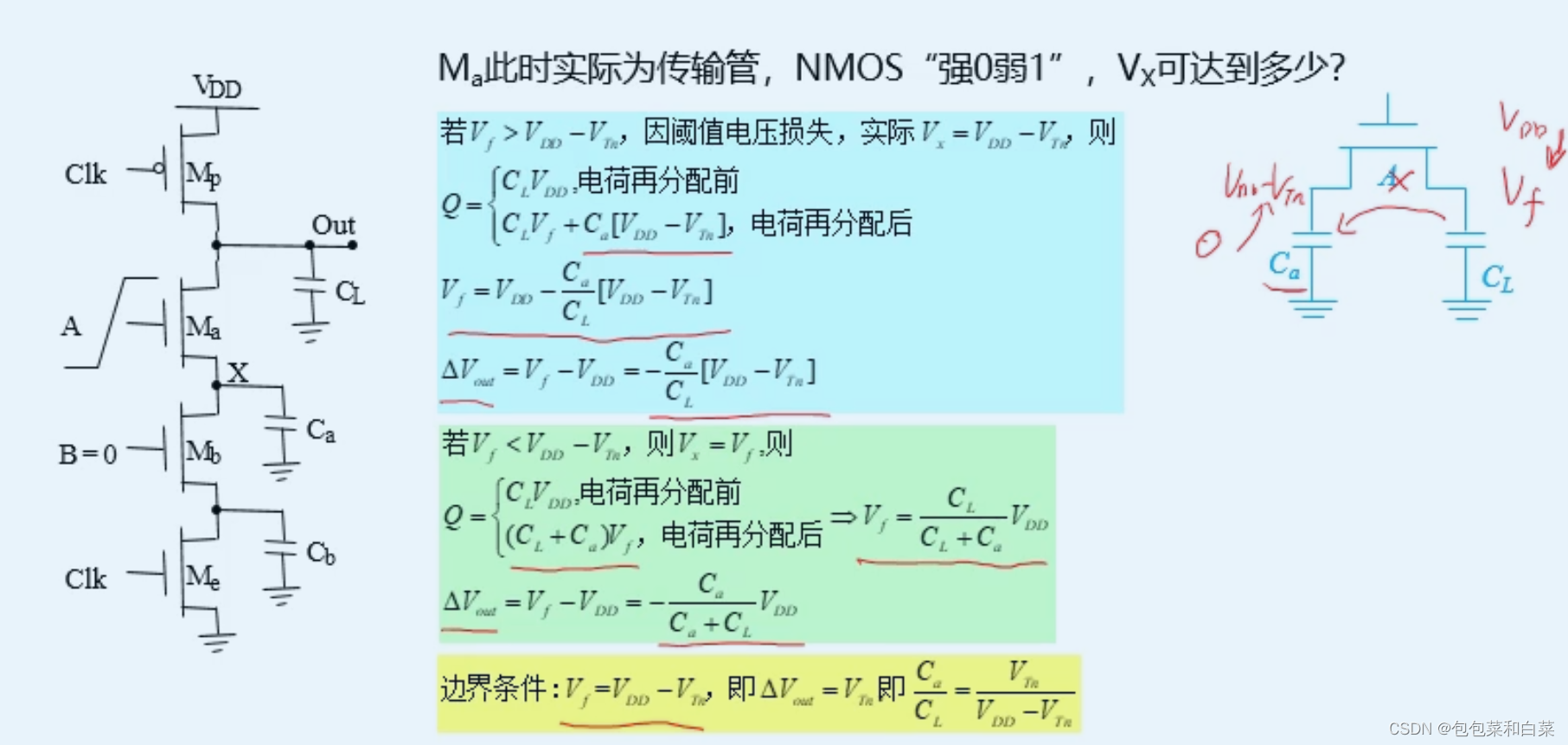

在动态逻辑中需要考虑的另一个重要问题是电荷分享的影响:在預充电阶段,输出节点被預充电至Vdd。假设在预充电期间,所有的输入被置为0。并且Ca已放电,同时还假设在求值期间输入B维持在0,而输入A由0→1翻转。使晶体管导通原本存储在电容CL上的电荷就在CL和Ca间重新分配,这就造成Out输出电压有所下降。由于电路的动态本质,这 一下降不能恢复 解决方法:

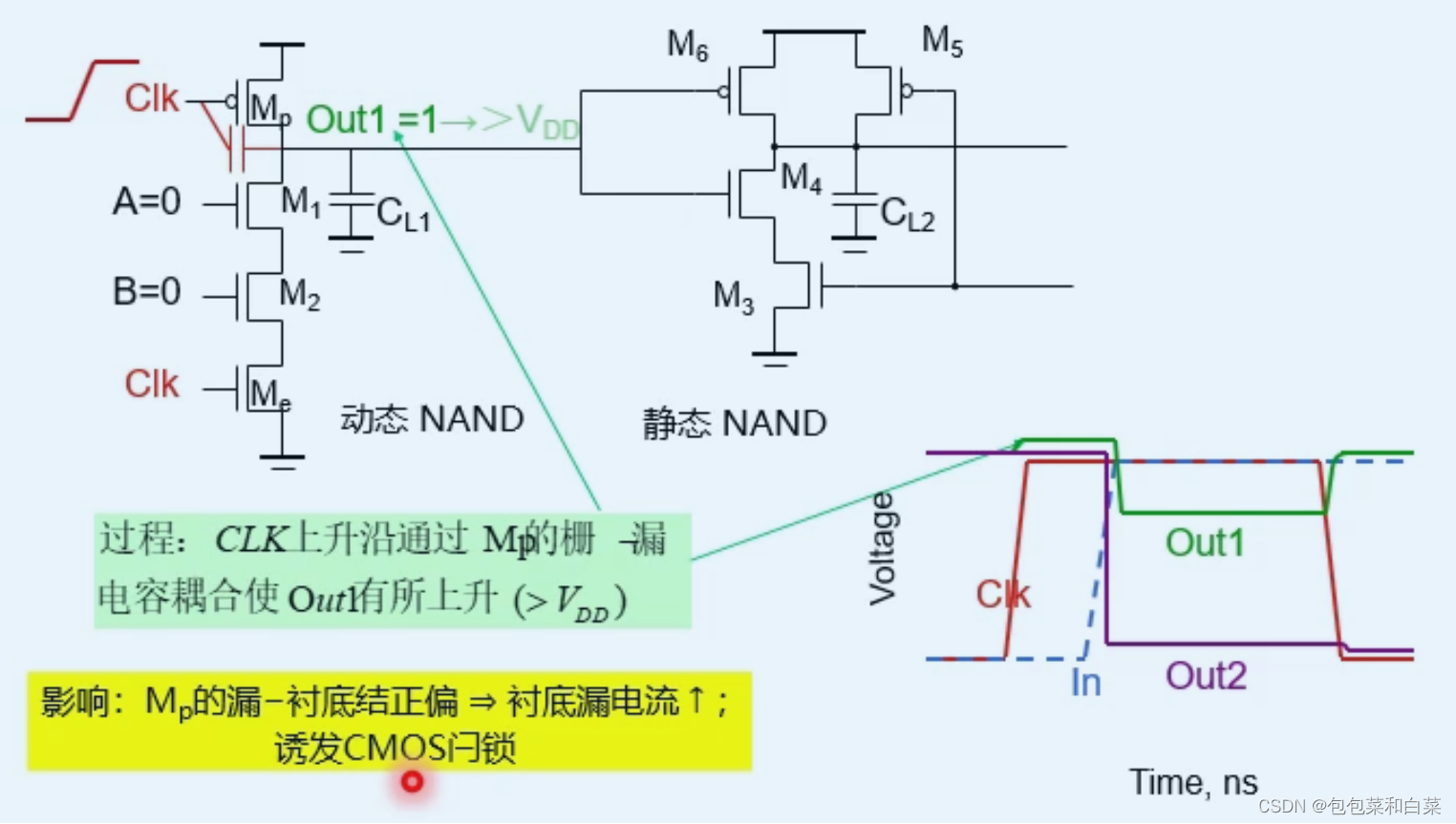

电荷分享后不一定X点的电压等于Out的电压,也可能再分享过程中Ma截止,电荷分享提前停止。 三、电容耦合

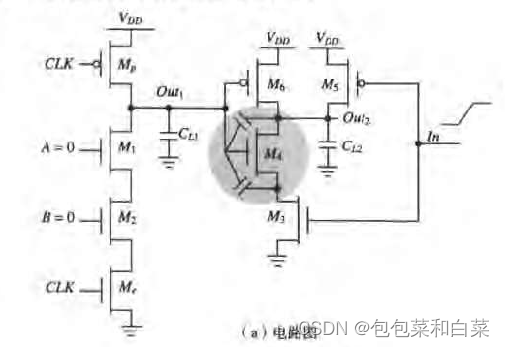

一个重要的电容耦合形式 是回栅(backgate ),即输出至输入耦合(Vout2影响Vout1)。 一个动态的两输入NAND门駆动一个静态NAND门,静态门输入In的翻转可能会造成该门的输出( Out2)变为低电平。这一 输出变化又会通过晶体管的栅-源和栅-漏电容耦合到这个门的另一个输入(动态节点Out1 )。 四、时钟馈通 电容耦合的一种形式,它是由在预充电器件的时钟输入和动态输出节点之间 的电容耦合引起的效应。耦合电容由预充电器件的栅-漏电容组成.当下拉网络不导通时.这一电容耦合会在时钟由低至高翻转时引起动态节点的输出上升到VDD以上。 时钟的上升引起Vout1的上升,Vout1可能大于VDD

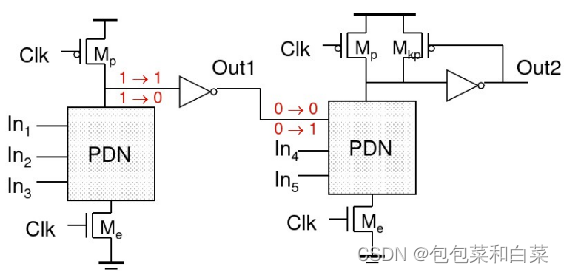

Out1变低是一个过程,这个过程中Out2无意放电; 多米诺逻辑

特点: 由于每个动态门都有一个静态反相器,因此它只能实现非反相逻辑。所以单纯的多米诺设计很少见(解决办法:采用差分结构)。 可以达到非常高的速度:只存在上升沿的延时,而TPHL等于零.可以调整反相器的尺寸使 之与扇岀匹配,这里扇出已比互补静态CMOS情形中小得多,因为每个扇出门只需要考虑一个栅电容。 6.4设计综述 6.4.1如何选择逻辑类型 6.4.2低电源电压的逻辑设计 6.5小结 6.6进一步探讨 |

【本文地址】

今日新闻 |

推荐新闻 |