计算机组成运算器实验:8位可控加减法电路、4位先行进位电路、4、16、32位快速加法器 |

您所在的位置:网站首页 › logisim标签 › 计算机组成运算器实验:8位可控加减法电路、4位先行进位电路、4、16、32位快速加法器 |

计算机组成运算器实验:8位可控加减法电路、4位先行进位电路、4、16、32位快速加法器

|

电路1— 8位可控加减法电路

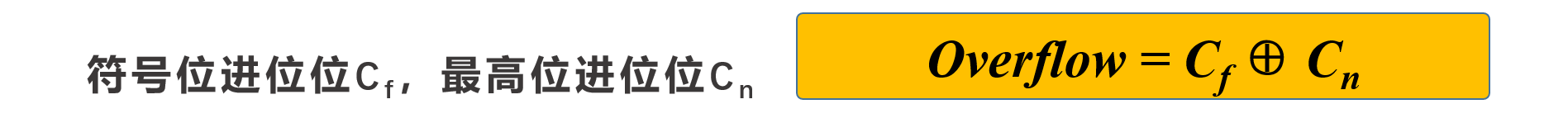

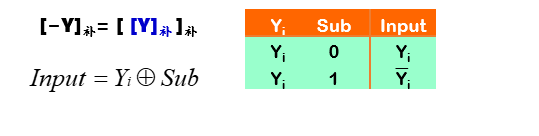

在 Logisim 模拟器中打开 alu.circ 文件,在对应子电路中利用已经封装好的全加器设计8位串行可控加减法电路,可以直接使用在电路中使用对应的隧道标签,其中 X,Y 为两输入数,Sub 为加减控制信号,S 为运算结果输出,Cout 为进位输出,OF 为有符号运算溢出位。 实验原理1.电路1 (1)overflow: (3)N位加法器: (4)运算控制器:Sub=0 时作加法,Sub=1 时作减法。[−Y]补= [ [Y]补 ]补,对 [Y]补逐位取反, 再在最低位加 1(体现在最右边的sub连接到最低位cin,此时sub=1,做减法)

各位逐位相加,进位从右至左传递。

在 Logisim 中打开 alu.circ 文件,按照图中定义的输入输出引脚,在对应子电路中实现可级联的4位先行进位电路。其中 Gi,Pi 为进位生成函数和传递函数,Cin 为进位输入,C1~C4 为进位输出,G,P 为成组进位生成函数和成组进位传递函数。 实验原理(1)并行加法器 进位输出仅与最低位进位输入C0有关(Cn=Gn+PnGn-1+PnPn-1Gn-2+PnPn-1Pn-2Gn-3 …+PnPn-1…P1C0),而不是依赖于低位进位(Cn= Gn + Pn Cn-1)。

利用前一步设计好的四位先行进位电路构造四位快速加法器,其中 X,Y 为四位相加数,Cin 为进位输入,S 为和数输出,Cout 为进位输出,G,P 为 4 位成组进位生成函数和成组进位传递函数。 实验原理(1) S4 = X4⊕Y4⊕C3 = P4⊕C3 S3 = X3⊕Y3⊕C2 = P3⊕C2 S2 = X2⊕Y2⊕C1 = P2⊕C1 S1 = X1⊕Y1⊕C0 = P1⊕C0 Gi = XiYi Pi=Xi⊕Yi (2)与门异或门电路(1 级门电路延迟)

十六位组间先行进位,组内先行进位快速加法器(即由4位扩展为16位)。 每4位的进位C1、C2、C3、C4是由CLA74128的上端接口连到4位快速加法器的进位输入端。

|

【本文地址】

今日新闻 |

推荐新闻 |

(2)1位加法逻辑电路:

(2)1位加法逻辑电路:  1位全加器:

1位全加器:

(5)可控加减法电路

(5)可控加减法电路

并行加法器进位链:(注意:Ci都是先行进位输出,是中间变量。而不是Si) C1 = X1Y1+(X1⊕Y1)C0=G1+P1C0 C2 = X2Y2+(X2⊕Y2)C1=G2+P2C1=G2+P2(G1+P1C0)=G2+P2G1+P2P1C0 C3 = X3Y3+(X3⊕Y3)C2=G3+P3G2+P3P2G1+P3P2P1C0 C4 = X4Y4+(X4⊕Y4)C3=G4+P4C3=G4+P4(G3+P3G2+P3P2G1+P3P2P1C0) = G4+P4G3+P4P3G2+P4P3P2G1+P4P3P2P1C0 G4 = G4+P4G3+P4P3G2+P4P3P2G1(成组进位生成函数) P4 = P4P3P2P1(成组进位传递函数) 所以C4 = G4+P4C0 (2)先行进位电路(2级门电路延迟)

并行加法器进位链:(注意:Ci都是先行进位输出,是中间变量。而不是Si) C1 = X1Y1+(X1⊕Y1)C0=G1+P1C0 C2 = X2Y2+(X2⊕Y2)C1=G2+P2C1=G2+P2(G1+P1C0)=G2+P2G1+P2P1C0 C3 = X3Y3+(X3⊕Y3)C2=G3+P3G2+P3P2G1+P3P2P1C0 C4 = X4Y4+(X4⊕Y4)C3=G4+P4C3=G4+P4(G3+P3G2+P3P2G1+P3P2P1C0) = G4+P4G3+P4P3G2+P4P3P2G1+P4P3P2P1C0 G4 = G4+P4G3+P4P3G2+P4P3P2G1(成组进位生成函数) P4 = P4P3P2P1(成组进位传递函数) 所以C4 = G4+P4C0 (2)先行进位电路(2级门电路延迟)  (3)两级先行进位电路(2级门电路延迟)

(3)两级先行进位电路(2级门电路延迟)  (4)总体电路:(2)和(3)结合; 总体封装电路(弄清哪些是输出,哪些是输入); 输入: P4G4 P3G3 P2G2 P1G1 C0 输出: 先行进位输出 C4 C3 C2 C1 成组进位传送输出P* 成组进位发生输出G*

(4)总体电路:(2)和(3)结合; 总体封装电路(弄清哪些是输出,哪些是输入); 输入: P4G4 P3G3 P2G2 P1G1 C0 输出: 先行进位输出 C4 C3 C2 C1 成组进位传送输出P* 成组进位发生输出G*

(3)四位快速加法器(4级门电路延迟)

(3)四位快速加法器(4级门电路延迟)