模拟集成电路设计 |

您所在的位置:网站首页 › cmos集成电路有哪些特点 › 模拟集成电路设计 |

模拟集成电路设计

|

学习目的

欠缺的学习路径: 固体物理,半导体器件物理,器件模型,电路设计。所有的半导体器件都看成一个黑盒子,只关注端电压电流。 最佳的学习路径:两手抓,因为有些二阶效应会影响到电路本身. 本章节学习MOS器件的建模,研究MOS晶体管的结构然后推导它的I/V特性。会讲一些二阶效应,比如体效应、沟道长度调制效应和亚阈值传导等二级效应。会讨论下MOS的寄生电容问题,然后推导MOS的小信号模型及SPICE模型。先验知识:掺杂、迁移率、pn结 基本概念 MOSFET开关先讨论简化的模型 G、S、D分别表示简化模型中MOS管的三个端口,G是栅极(Gate),S是源极(Source),D是漏级(Drain)。在不施加任何电压的情况下MOS管是对称的,所以谁是源极谁是漏极就是看外部所加的电压。图示是一个n型的mos管,当我们给G极加高电平时,晶体管的漏级和源极就接到了一起,当我们给G极加低电平时,晶体管的漏极和源极就是断开的。 上面那段描述不是很精确,比如说多大的电压算高电平?(skip-1)器件导通(断开)时电阻多大?(skip-2)源漏电阻和各端电压有关系吗?(skip-3)有关系的话关系是怎么样的?我能不能用线性电阻来替代源漏之间的通路?器件的速度怎么样?【question-1】 看,我们提出了这么多疑问,接下来就慢慢的解答! MOSFET 结构

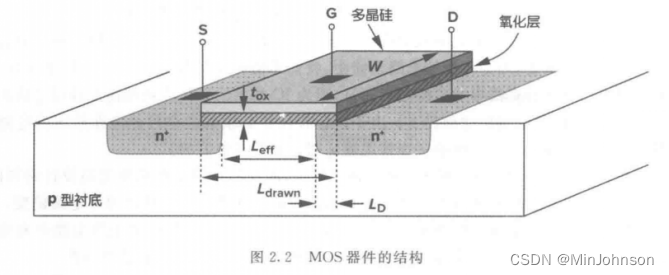

上图是NMOS的器件结构图,可以理解成用显微镜看到的结构。至于怎么做出来的NMOS,可以看这篇文章【question-2】。看到上面这张图,我们来学习一下MOS的一个大致结构。p型衬底我们一般称为bulk或者body,在衬底上掺入杂质形成两个重掺杂的n区(将来就是源极和漏极)。整个结构上面那个凸起,也就是重掺杂的多晶硅区(poly)是栅极,用一层 S i O 2 SiO_2 SiO2(栅氧层)将栅极和衬底隔离开来。整个器件起作用就起在栅氧层下面的衬底部分。 接下来我们看几个认为规定的物理量: 栅长L和栅宽W:可以看到栅极长得像一个立方体,俯视图就是一个长方形,沿着源漏方向的栅极长度我们称为栅长 L L L,与之垂直的方向的栅的长度我们称之为栅宽 W W W(在集成电路工艺中往往 W W W> L L L,但是在数学中我们常常把矩形的短边称为宽)。有效栅长 L e f f L_{eff} Leff :由于源和漏的扩散,导致实际的距离不会有 L L L L e f f = L d o w n − 2 L D L_{eff}=L_{down}-2L_{D} Leff=Ldown−2LD : L d r a w n L_{drawn} Ldrawn是总长度( L d r a w n L_{drawn} Ldrawn也是晶体管在画版图时的尺寸),而 L D L_{D} LD是横向扩散的长度。氧化层厚度 t o x t_{ox} tox:表示栅氧层的厚度 影响集成电路性能的关键参数: L e f f t o x L_{eff}\quad t_{ox} Lefftox我们会产生一个疑惑:既然MOS是一个对称的结构,那为什么要把两个

n

+

n^{+}

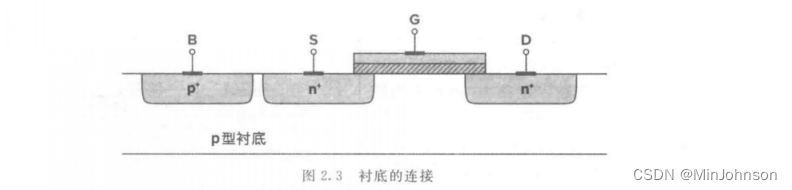

n+ 区域一个称为漏极,一个称为源极呢?(skip-4) 还有一个就是我们注意到MOS结构里面有衬底,我们还没有对衬底对整个器件的影响进行探讨。(skip-5) 实际上衬底的电位对器件的影响是很大的。我们不应该把MOS看成三端器件,而应该是四端的。常规的MOS工作状态我们需要保证源漏极和衬底组成的二极管处于反偏状态【question-2】,所以我们常常将NMOS的衬底接到系统最低电位。举个例子,整个电路工作在0~1.2V的话,

V

s

u

b

N

M

O

S

=

0

V_{subNMOS}=0

VsubNMOS=0。我们通常通过如下图方式来实现衬底电位的施加。通过在衬底上掺杂出一个

p

+

p^+

p+区域然后再加电压。我们把衬底加电压的这一个端口称为B(bulk)端口。 我们上面看到PMOS具有局部衬底这个特点,那我们其实可以仿照这种形式给NMOS也设计一个阱。下图这种形式就是深n阱工艺,这会导致面积开销。那优点呢?【question-4】

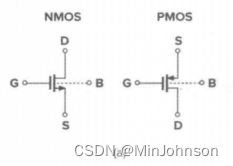

这是最常规的MOS符号,把MOS的每个端子都标识出来了,通常NMOS的N极我们放到下面,PMOS的S极我们放上面,因为通常NMOS的源极接低电压,PMOS的源极接高电压。 第二种画法

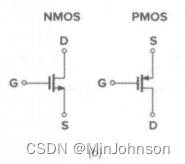

这种画法把B给删掉了,大多数电路中,NMOS的bulk接地,PMOS的bulk接VDD。 第三种画法

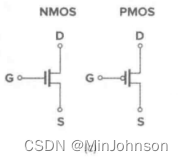

在数字电路中我们往往只把MOS当成一个开关来看,不太关注电流的流向,所以我们会发现MOS的箭头没了,区分NMOS和PMOS的方法就是看栅极有没有小圆圈。有小圆圈表示低电平导通,那就是PMOS,反之则是NMOS。 |

【本文地址】

今日新闻 |

推荐新闻 |

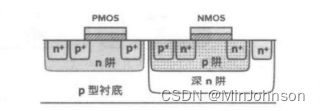

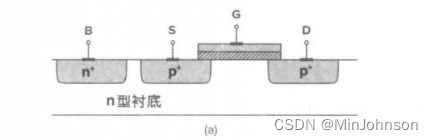

如今我们常用的一种技术是互补MOS技术 (CMOS-Complementary MOS),这种技术同时使用PMOS和NMOS。根据上面NMOS的结构图我们可以简单的把各个掺杂区域取反得到PMOS的结构图,如下

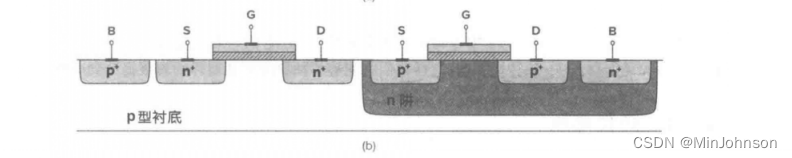

如今我们常用的一种技术是互补MOS技术 (CMOS-Complementary MOS),这种技术同时使用PMOS和NMOS。根据上面NMOS的结构图我们可以简单的把各个掺杂区域取反得到PMOS的结构图,如下  但是实际上我们做芯片都是做在一块晶片上,这就意味着所有MOS的衬底都相同。所以我们不可能让一块衬底具有两种极性的掺杂。这就要求我们需要把其中一种MOS做在局部衬底上,并且我们把这种局部衬底称为“阱”,英文名是"well"。通常,现代CMOS工艺中,PMOS器件做在n阱里,如下图所示。

但是实际上我们做芯片都是做在一块晶片上,这就意味着所有MOS的衬底都相同。所以我们不可能让一块衬底具有两种极性的掺杂。这就要求我们需要把其中一种MOS做在局部衬底上,并且我们把这种局部衬底称为“阱”,英文名是"well"。通常,现代CMOS工艺中,PMOS器件做在n阱里,如下图所示。  由于NMOS是做在一块大的p衬底上的,这就意味着我们给衬底加电压一般只有一个选择(要照顾到所有的NMOS),也就是说只能给NMOS的p衬底拉到系统最低电压。但是对于PMOS来说不一样,基本上是好几个PMOS做在一个阱中,那么我们可以给这几个PMOS的阱相同的电压,这个电压虽然说是高电压,但是没说一定要是系统最高电压,我可以让这个PMOS的B端电压等于S极电压,这都是NMOS所不具备的特点。这种特性有一定的应用。【question-3】

由于NMOS是做在一块大的p衬底上的,这就意味着我们给衬底加电压一般只有一个选择(要照顾到所有的NMOS),也就是说只能给NMOS的p衬底拉到系统最低电压。但是对于PMOS来说不一样,基本上是好几个PMOS做在一个阱中,那么我们可以给这几个PMOS的阱相同的电压,这个电压虽然说是高电压,但是没说一定要是系统最高电压,我可以让这个PMOS的B端电压等于S极电压,这都是NMOS所不具备的特点。这种特性有一定的应用。【question-3】