MEMS |

您所在的位置:网站首页 › cmos集成电路制造工艺介绍 › MEMS |

MEMS

|

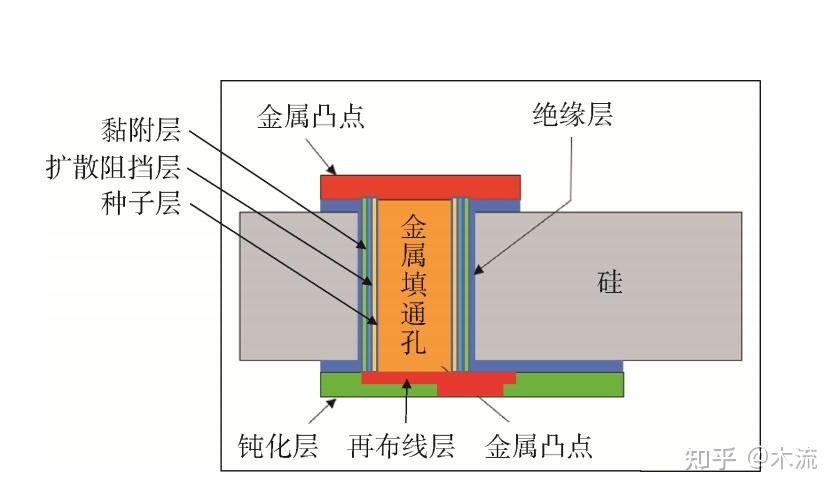

Q1: 为什么要进行异质集成,有什么优劣势? 1. Post-CMOS工艺将电子电路与传感器、执行器等多种不同类型的单元同时加工在芯片上以实现集成微系统是超 越摩尔定律技术所追求的目标, 实现电路与不同功能结构的完全集成可以提高系统的性能, 降低加工、 封装的成本. 理想的集成方式是把不同的器件在单芯片上完成, 即单片集成技术, 其集成度最高, 难度也最大. 当不同的器件由异质材料构成的时候, 所面临的挑战更大(具体的挑战主要有). 虽然通过单片集成将 IC 与 MEMS 加工在同一个芯片上, 可以减小芯片的总面积, 节省一次封装, 但这些所带来的成本优势却可能被增加的工艺复杂度和难度所抵消. 从加工成本和实用化考虑, 单片集成的 Post-CMOS 工艺, 即在 CMOS 电路加工完成之后再进 行其他功能结构的加工是最优的方案, 这样 CMOS 电路部分的加工可以在标准的集成电路代工厂完成, 最大限度地降低设计成本和提高成品率. 因此 Post-CMOS 技术一直是集成化研究的热点. CMOS -MEMS 工艺是由美国卡耐基梅隆大学开发的一种完全的 Post CMOS 集成工艺 。 它采用 CMOS 电路中的互连金属及金属间的介质作为机械结构, 所以 CMOS 电路加工完成后只需几步各向异性和各向同性的干法刻蚀就可以完成器件的加工. 这种工艺的一个特点是所有的工艺步骤都是单面加工, 所以可以很容易地移植到基于不同尺寸衬底的工艺线上. 这种工艺的主要缺点是机械结构的厚度有限, 而且有较大的残余应力. 近年来, 台湾地区的清华大学等研究机构, 依托台积电的 CMOS 工艺, 在 这方面开展了很多研究工作 . Li 等利用台积电的 0.18 µm 1P6M (1 层多晶硅 6 层金属) CMOS . 由于实现不同功能的微结构种类繁多, 可能会使用到与集成电路工艺不兼容的加工方法, Post-CMOS 工艺可以实现的集成微系统还是有限的. 作为目前的主要营收来源, 台积电为 InvenSense 加工 陀螺和 IMU 所采用的实际是一种混合集成工艺 : CMOS 电路和 MEMS 结构分别加工在一个晶圆上. MEMS 所在的晶圆同时起到封帽的作用, CMOS 在相应的区域刻蚀出一个腔体. 两个圆片通过金硅共熔合金的方式实现键合, 形成陀螺所需的真空腔体, 同时实现圆片级封装. 该工艺在减小寄生效应和封装尺寸的同时, 也减轻了前面说到的一些集成方面的缺点. 这种基于键合的混合集成技术成为 工业界的一种主流工艺. 这种方法不但可以实现硅基衬底上不同器件的集成, 也可以实现不同衬底的异质集成. . 但这种方式由于芯 片之间是垂直连接的, 复杂芯片之间的电学互联很难实现. 近些年新开发出来的硅通孔互联(TSV) 技术为芯片之间的垂直互联提供了有效的途径. 通过 TSV (Through Silicon Vias) 技术可以实现 CMOS, MEMS 以及光电子电路等多种系统的三维混合集成. 下面主要介绍基于基于 TSV 的相关异质集成技术. 2. TSV(硅通孔)3D集成技术Q2: TSV的技术是基于CMOS电路晶圆与MEMS晶圆对准的前提进行刻蚀通孔的操作?这里就涉及到了如何对准的普遍问题? 2.1 概念TSV 技术把芯片堆叠加起来, 使用硅通孔在垂直方向为各个芯片提供电路连接. 与引线键合相比, 硅通孔缩短了垂直方向电路的连接, 因此大大减小了信号的 RC 延迟和互连上的功率损耗. 三维集成电路和 TSV 技术极大地提高了集成 度, 推动工业界向 “延续摩尔定律” 和 “超越摩尔定律” 发展, 在学术界和工业界掀起研究热潮. 通过 TSV 技术实现 CMOS、射频电路、传感器、微流控以及光电子等多种系统的三维混合集成也是近年 来值得关注的热点: 采用 TSV 技术将不同的系统和元件组合在一起, 形成复杂的微系统 .TSV 主要用于实现垂直方向上的信号连接,其中Cu-TSV 的应用最为广泛. 典型的 Cu-TSV 制造工艺包括以下关键步骤:深孔刻蚀、形成绝缘层 / 粘附阻挡层/种子层、电镀 Cu 填充、去除多余 Cu 及背面的 TSV-Cu外露[1][2]。目前用于三维异质集成的 TSV 直径约为 10 μm,深宽比约为 10∶1。与半导体领域的其他技术发展方向类似,TSV 的直径、间距和深度等关键尺寸亟需缩小。TSV 直径的减小,不但能够减少其占用面积、提高互连密度,还可以显著减少 Cu-TSV 附近的应力,避免影响器件性能。根据 TSV 的直径及深宽比的路线图,未来先进 TSV 工艺的直径有望减小到 1 μm,深宽 比达到 20∶1[3]. 国际上重要的半导体科研机构和领先企业已经开始研究亚微米直径的 TSV 技术。细小直径、高深宽比的 TSV 加工的主要难点包括如何形成连续均匀的绝缘层 / 粘附阻挡层 / 种子层和无缺陷的超共形电镀 Cu 填充等。由于物理气相沉积 (PVD)、化学气相沉积(CVD)在微米尺度深孔内覆盖率低,通过 PVD、CVD 沉积绝缘层、粘附阻挡层和种子层不利于 TSV 尺寸的进一步缩小. 原子层沉积(ALD)可制备小直径、高深宽比的共形薄层,成为突破 PVD 工艺瓶颈的关键技术. ALD 具有的优势包括:较低的工艺温度,比现有 CVD 及 PVD 工艺更好的深孔覆盖能力,介质沉积前无需表面处理,更薄的介质层减少了 TSV 的抛光处理时间。2015 年,IMEC 报道了直径为 3 μm、深度为 50 μm 的 TSV 制造工艺,采用ALD 沉积氧化绝缘层、WN 扩散阻挡层,利用化学镀NiB 作为电镀种子层,快速深孔电镀工艺实现 TSV 填充. 学者研究了直径为 2 μm、深度为30 μm 的TSV 结构,在 ALD-Ru、ALD-W 上化学镀沉积铜,然后完成 TSV 电镀铜填充,化学镀铜和 ALD-Ru 之间的结合强度大于 100 MPa[4]。然而,当前工艺探索和研究还缺乏系统性,深孔电镀 / 化学镀填充、ALD 沉积形 成多界面材料和结构的电学特性、可靠性以及失效机理都还需要深入研究。  图1.TSV技术原理图 图1.TSV技术原理图TSV技术典型的特点是直上直下,但实际集成过程中需要线路是可以调整的,这就是涉及到了类似PCB中的布线技术,即RDL技术。 3. RDL技术RDL 是实现芯片水平方向互连的关键技术,可将芯片上原来设计的 I/O 焊盘位置通过晶圆级金属布线工艺变换位置和排列,形成新的互连结构。借鉴 PCB 铜布线工艺,RDL 可通过加成法、半加成法等方法加 工。 典型的 RDL 半加成工艺包括[5]:(1)形成钝化绝缘层并开口;(2)沉积粘附层和种子层;(3)光刻显影形成线路图案并电镀填充;(4)去除光刻胶并刻蚀粘附层和 种子层;(5)重复上述步骤进行下一层的 RDL 布线。高 密度的 RDL 布线可借鉴半导体铜互连的大马士革工艺进行加工,引入化学机械抛光进行平坦化,并去除 多余的铜及粘附层/种子层。 目前,高密度互连有机 RDL 线宽/线间距(L/S)约 为 6 μm,微孔直径为 20 μm、间距为 50 μm,可实现每平方毫米每层约 40 个 I/O 的密度[6]。然而,为了进一 步提高 I/O 密度,需要具有 1 μm 线宽/线间距以及 1~ 2 μm 直径微孔的 RDL。RDL 技术的进步对于实现高 密度、高带宽(每平方毫米每层超过 500 个 I/O、带宽 大于 500 Gbit/s)的芯片互连具有极为重要的意义。高密度 RDL 有 4 个关键问题:(1)细线条光刻 L/S 为 1 μm;(2) 微孔加工是限制 RDL 实现高 I/O 密度和精细 I/O 间距的最主要的障碍;(3)低介电常数和低耗损因子的介电材料;(4) 半加成法是实现高密度 RDL 的 普遍工艺。 4. 基于 TSV 及 RDL 的异质集成方案用 TSV 简单互连代替引线键合,实现硅背面与正面有源区或金属布线之间的电气导通,是 TSV 在批量生产中的首次使用。其典型应用包括图像、指纹、滤波器、加速度计在内的传感器的封装,基于 TSV 的 MEMS 传感器封装结构如图 2 所示[7]。使用 TSV 可减小传感器模块的封装尺寸,利于进行晶圆级封装,提高生产效率并降低成本。近年来发展出的基于后通孔 TSV 的埋入硅基三维异质集成技术,提供了 1 种低成 本、高性能的异质集成方案。2016 年,华天科技有限公 司开发出硅基埋入扇出(eSiFO)技术,使用硅片作为载体,将芯片置于在 12 英寸硅晶圆上制作的高精度凹槽内,重构出 1 个晶圆;然后采用可光刻聚合物材料填 充芯片和晶圆之间的间隙,在芯片和硅片表面形成扇出的钝化平面;再通过光刻打开钝化层开口,并采用晶圆级工艺进行布线和互连封装。硅基埋入封装具有超小的封装尺寸、工艺简单、易于进行系统封装和高密度三维集成等优点[8]。同时,可通过制备背面 RDL和 Via-last TSV,实现异质集成多芯片的三维堆叠封装。其基本工艺流程包括:将测试正常的芯片嵌入单个 eSiFO 封装体,然后分别在 eSiFO 封装体的正面和背面形成 RDL,再通过微凸点和 Via-last TSV 实现多个独立的 eSiFO 封装体与嵌入式芯片之间的电信号互连。eSiFO 技术可以将由不同设计公司、晶圆厂设计制造的各种晶圆尺寸和特征尺寸的不同系统或不同功能的芯片集成到 1 个芯片中,从而实现真正的不同封装体之间的三维异质集成封装。  图2 TSV技术与RDL技术5. 总结 图2 TSV技术与RDL技术5. 总结 三维异质集成的最终目标是实现模拟、数字、存储器、射频、ASIC、MEMS 等各类芯片的异质多功能集成。 在我的文章中主要是与MEMS-CMOS技术有关的异质集成技术,因为3D异质集成的分类十分繁多,文章只是挑了比较常见的出来就行描述。实际工作过程中,很可能会限制于工艺产线的技术,或者是经费限制,或者公司战略考虑,需要按照自身工作环境选择最优的解决方案。 别忘了,技术最终是为了解决问题。不要被技术手段所束缚,只要能解决问题,一切皆可。 参考^HUYLENBROECK S V, LI Y, HEYLEN N, et al. Advanced metallization scheme for 3 ×50 μm via middle TSV and beyond[C]//2015 IEEE 65th Electronic Components and Technology Conference(ECTC), San Diego, CA, USA, IEEE, 2015: 66-72.^ SUGAWARA Y, HASHIGUCHI H, TANIKAWA S, et al. Impact of deep-via plasma etching process on transistor performance in 3D-IC with via-last backside TSV [C]// 2015 IEEE 65th Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, IEEE, 2015: 822-827.^https : //www . semiconductors . org/resources/2015-international-technology-roadmap-for-semiconductors-itrs[Z].^SUGAWARA Y, HASHIGUCHI H, TANIKAWA S, et al. Impact of deep-via plasma etching process on transistor performance in 3D-IC with via-last backside TSV [C]// 2015 IEEE 65th Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, IEEE, 2015: 822-827.^LAU J H. Fan-out wafer-level packaging [M]. Singa pore: Springer, 2018.^ LIU F, CHANDRASEKHARAN N, ATSUSHI K, et al. Organic damascene process for 1.5-μm panel-scale redistribution layer technology using 5-μm-thick dry film photosensitive dielectrics [J]. IEEE Transactions on Components, Packaging and Manufacturing Technology, 2018, 8(5): 792-801.^ SEKHAR V N, TOH J S, JIN C, et al. Wafer level packaging of RF MEMS devices using TSV interposer technology [C ]//2012 IEEE 14th Electronics Packaging Technology Conference (EPTC), Singapore, IEEE, 2012: 231-235.^ HONG X, YU D Q, HUANG Z R, et al. Embedded Si fan out: A low cost wafer level packaging technology without molding and de-bonding processes[C]// Proceedings of the 2017 IEEE 67th Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, IEEE, 2017: 28-34 |

【本文地址】

今日新闻 |

推荐新闻 |