logisim实验MIPS运算器(ALU)设计(内含4位先行进位74182、四位快速加法器、32位快速加法器) |

您所在的位置:网站首页 › 4位先行进位74182设计原理 › logisim实验MIPS运算器(ALU)设计(内含4位先行进位74182、四位快速加法器、32位快速加法器) |

logisim实验MIPS运算器(ALU)设计(内含4位先行进位74182、四位快速加法器、32位快速加法器)

|

系列实验目录

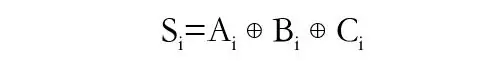

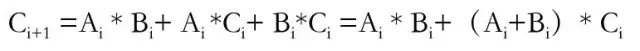

传送门 实验一 - logisim实验8位可控加减法电路-Educoder 实验二 - logisim实验原码一位乘法器-Educoder 实验三 - logism实验MIPS运算器(ALU)设计(内含4位先行进位74182、四位快速加法器、32位快速加法器)-Educoder 实验四 - logisim实验汉字字库存储芯片扩展-Educoder 实验五 - logisim实验寄存器文件设计-Educoder 实验六 - logisim实验MIPS RAM设计-Educoder 实验七 - logisim实验4路组相连cache设计-Educoder 实验八 - logisim实验单周期MIPS CPU设计-Educoder 实验九 - logisim实验微程序地址转移逻辑设计-Educoer 实验十 - logisim实验MIPS微程序CPU设计-Educoder 实验十一 - logisim实验硬布线控制器状态机设计-Educoder 实验十二 - logism实验多周期MIPS硬布线控制器CPU设计(排序程序)-Educoder 目录 系列实验目录 一、4位先行进位74182设计 二、4位快速加法器设计 三、16位快速加法器设计 四、32位快速加法器设计 五、算逻单元ALU 1、电路框架 2、电路引脚 3、操作数与对应所要实现功能 ①逻辑左移、运算右移、逻辑右移 ②32位乘法器、32位除法器 ③加法器、减法器 ④按位与、按位或、按位异或、按位异或非 ⑤有符号比较、无符号比较 ⑥数据选择器控制电路 一、4位先行进位74182设计一位二进制全加器原理: 设二进制加法器第i位为Ai,Bi,输出为Si,进位输入为Ci ,进位输出为Ci+1,则: |

【本文地址】

今日新闻 |

推荐新闻 |

设 G i = A i ∗ B i {G_i} = {A_i}*{B_i} Gi=A

设 G i = A i ∗ B i {G_i} = {A_i}*{B_i} Gi=A