CPU、Cache以及DDR之间访问关系 |

您所在的位置:网站首页 › 跳过cpu访问有什么用 › CPU、Cache以及DDR之间访问关系 |

CPU、Cache以及DDR之间访问关系

|

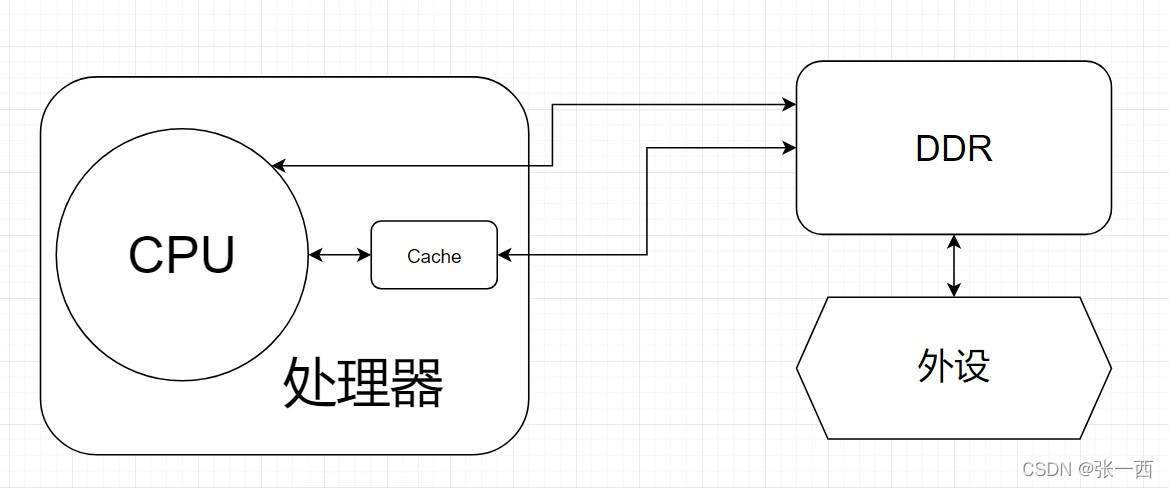

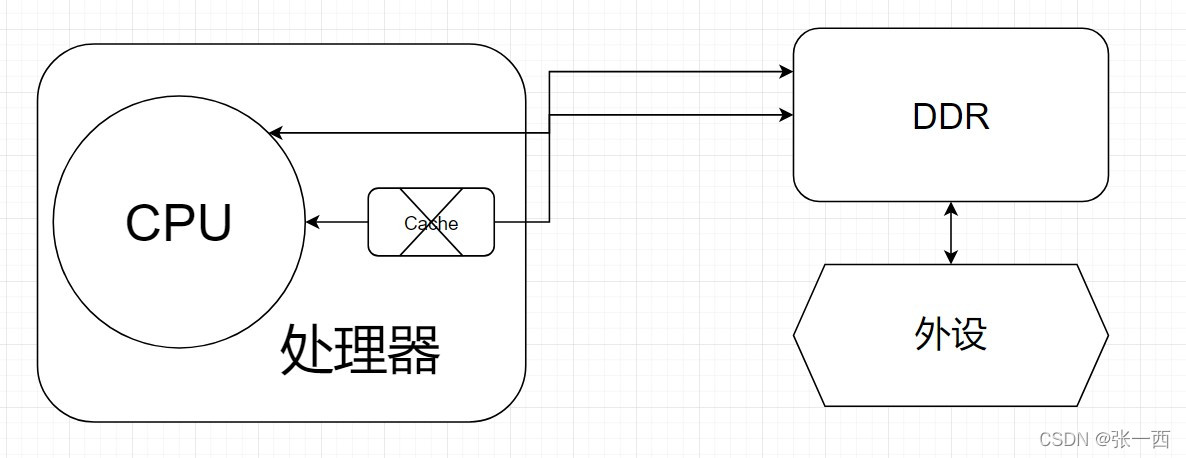

Cache是一个介于CPU以及DDR(DRAM)之间的一个高速缓存(一般好像是SRAM),在处理器内部,读写速度较DDR高,但是低于CPU的速度。假如没有Cache,直接访问DDR,CPU的速度远远高于DDR,那么CPU就需要等待DDR的数据到来,才能做其他事情,就会造成CPU使用效率较低。 使用Cache之后,提前将DDR的数据缓存到Cache中,如果恰好CPU访问DDR的数据在Cache中有,那么CPU拿到数据的时间将更短,处理效率将大大增加。如何提高Cache的命中率那是另外一回事,不在本文的讨论中。 但是同时也会造成一致性问题,即CPU的访问的数据(Cache)与DDR的数据没有同步,造成执行错误。 假设一种真实情况,CPU要访问DDR中的一块数据,那么这块数据会放在Cache中,之后DMA控制器直接将外设的数据放在DDR中,更新了刚刚的那一块CPU要访问的数据,此时CPU要获取数据进行处理,还是拿着Cache中未更新的数据,就会造成一致性问题。 如何避免这种问题呢?将Cache中的数据清空,或者将DDR与Cache的数据同步,即可解决一致性问题,所以在使用外设的时候,假如有Cache的话,一定要注意这个问题。 通过这两张图,我们来认识一下cache与volatile。 volatile 能保证数据从内存中读取,不使用寄存器当中的数据,其次,虽然从内存中读取,但是不能用于线程同步,需要用互斥量或者mutex去同步。(比如同时增加两次,中间被其他线程穿插一次,那么异常了)cpu 如果从内存中读数据,cache如果命中,则从cache中读取,不去内存中读取。总之,如果内存是cache able,意思是这块内存被映射到cache中了,数据可能会被命中。如果是uncach eable的,则没有cache会映射到这里,volatile修饰时,则会从内存中读取,同时也会防止优化,是有作用的。 |

【本文地址】

今日新闻 |

推荐新闻 |