4.实验三:组合逻辑电路的分析与设计 |

您所在的位置:网站首页 › 译码器的功能测试及应用实验结果分析 › 4.实验三:组合逻辑电路的分析与设计 |

4.实验三:组合逻辑电路的分析与设计

|

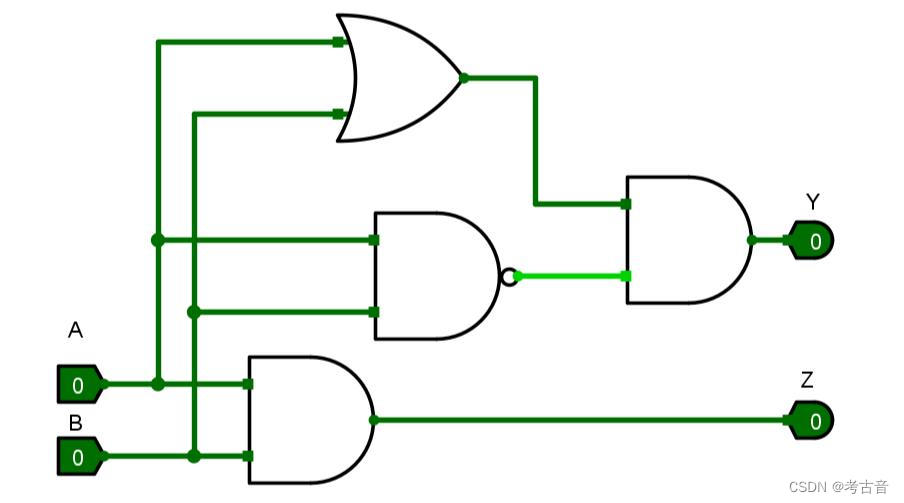

一、概括

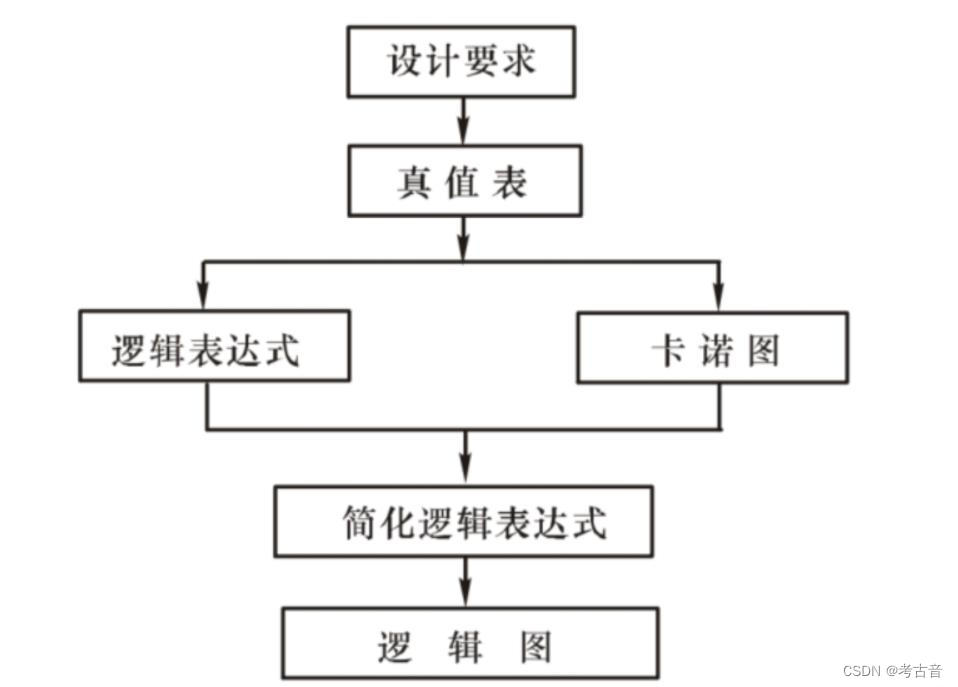

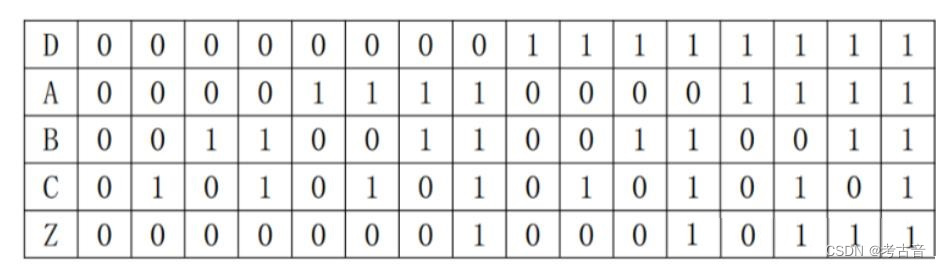

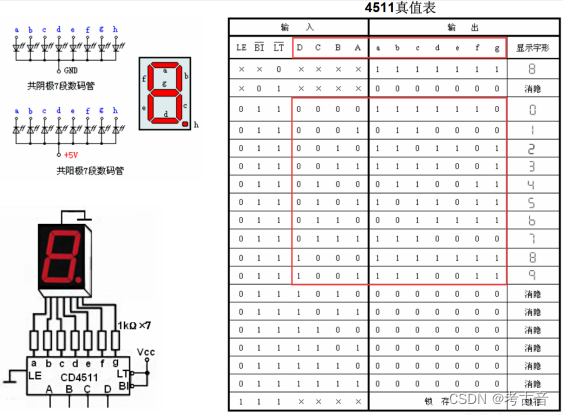

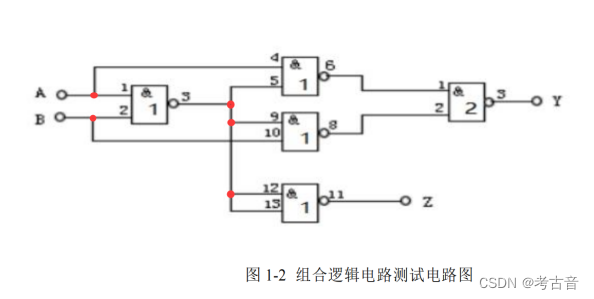

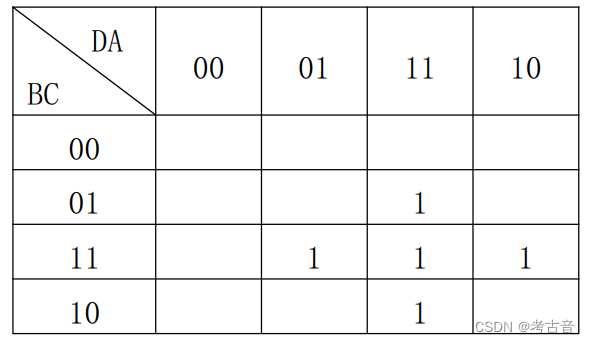

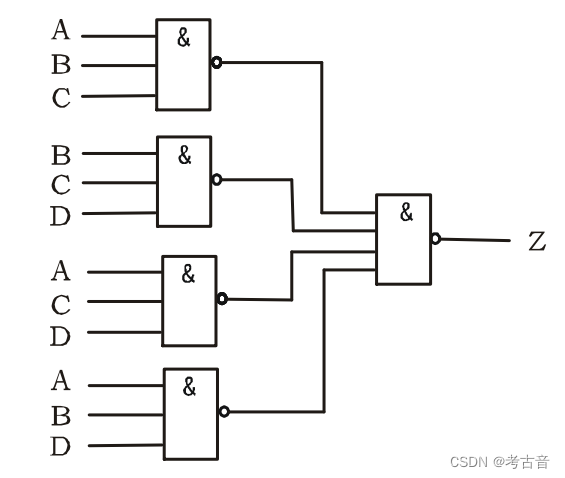

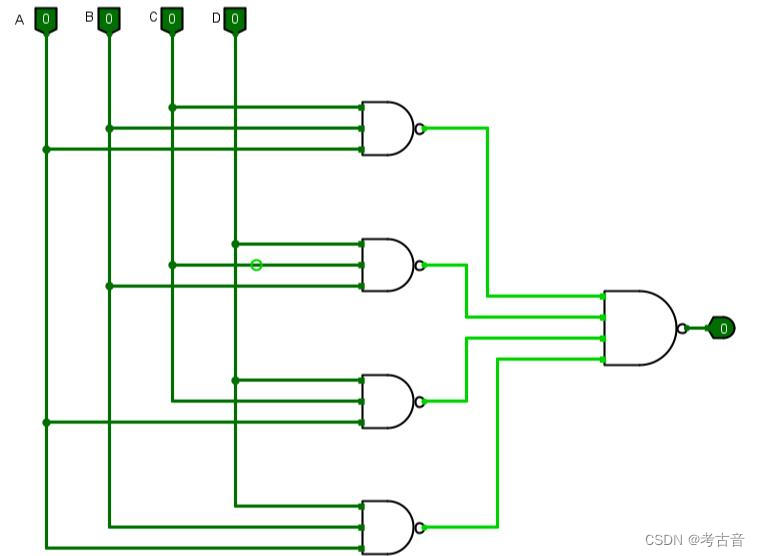

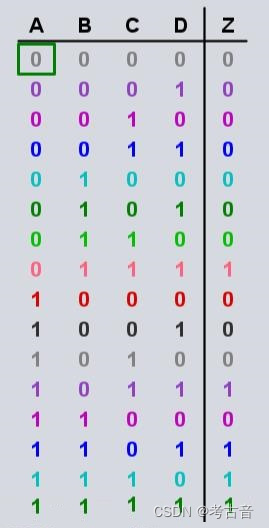

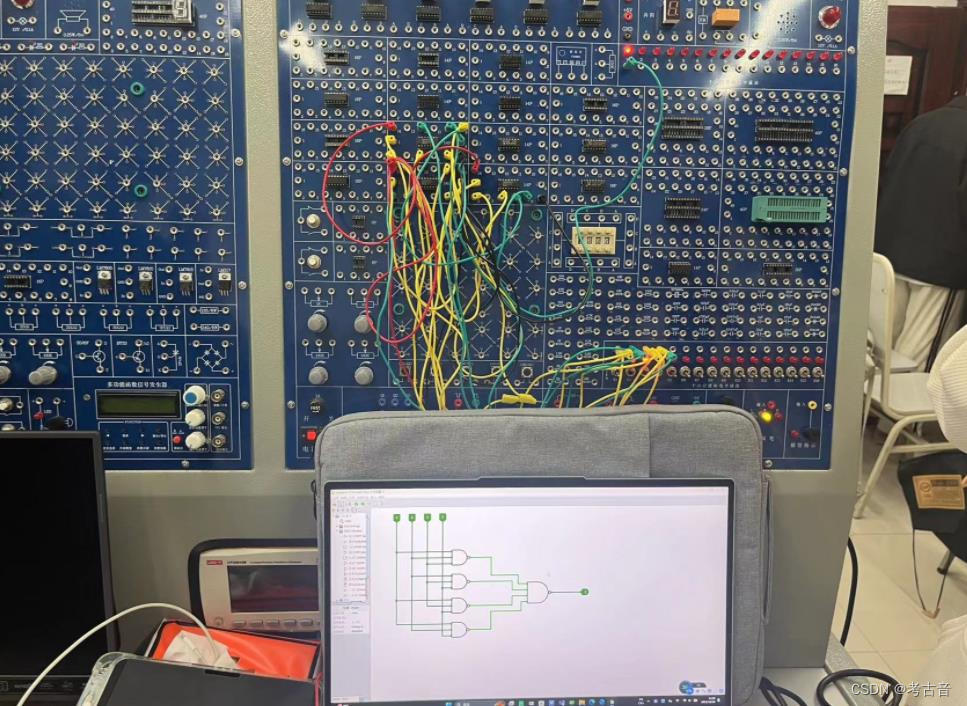

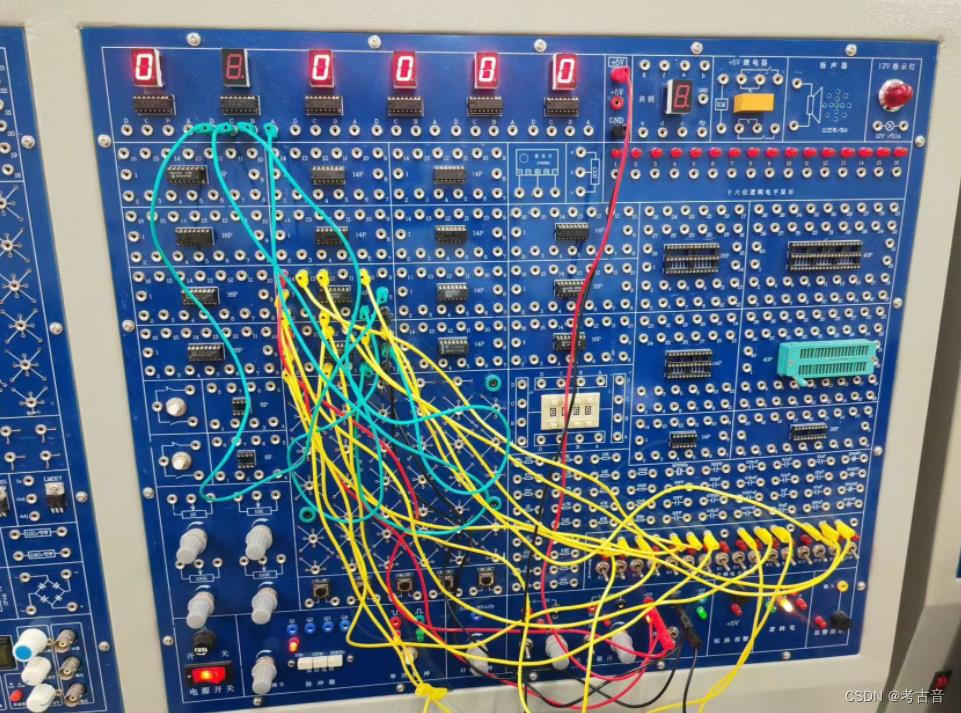

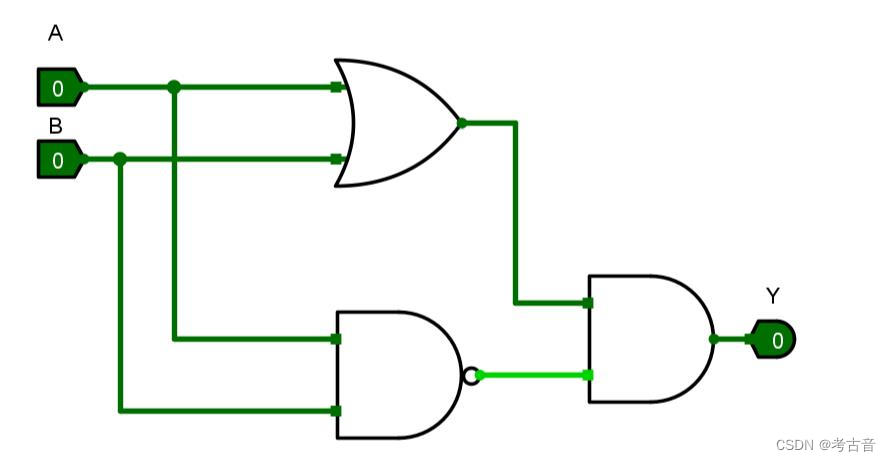

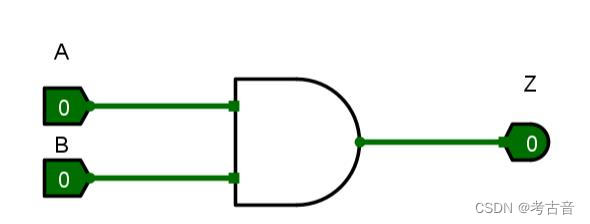

在前面的学习里,我们掌握了基本门电路的定义及其运算法则。本篇目的为掌握组合逻辑电路的分析与设计,掌握真值表,逻辑函数表达式、卡诺图化简基本概念和方法。 二、设计组合电路的基本步骤使用中规模和小规模集成电路来设计组合电路是最常见的逻辑电路。其基本步骤如下图所示: 根据设计任务的要求建立输入变量和输出变量并且列出其真值表。 然后采取逻辑表达式或者卡诺图的方式求出简化的逻辑表达式。 按实际选用逻辑门的类型修改逻辑表达式,并根据化简后的逻辑表达式画出逻辑图。 在电路实验箱上用标准器件构成逻辑电路,通过实验来验证设计的正确性。 三、实验内容 (一)组合逻辑电路--四路表决器 设计要求:用“与非”门设计一个表决电路,具体情况如下:当四个输入端A、B、C、D中有三个或四个为“1”时,输出端才为“1”。 真值表如下图所示: 本化简式运用了1.德摩根定理  由卡诺图画卡诺圈得出逻辑表达式为: 由卡诺图画卡诺圈得出逻辑表达式为: 根据化简得到的含“与非门”逻辑表达式画出逻辑电路图如下图所示: 根据化简得到的含“与非门”逻辑表达式画出逻辑电路图如下图所示: 在logsim中建立的逻辑图如下图所示: 在logsim中建立的逻辑图如下图所示: logsim中得出逻辑图理论真值表如下图所示:(与计算得到的真值表情况相同) logsim中得出逻辑图理论真值表如下图所示:(与计算得到的真值表情况相同) 电路实验箱实物连接:在实验装置适当位置选定三个14P 插座,按照集成块定位标记插好集成块74LS20。按化简得到的逻辑图接线,输入端 A、B、C、D 接至逻辑开关输出插口,输出端 Z 接逻辑电平显示输入插口,按真值表(自拟)要求,逐次改变输入变量,测量相应的输出值,验证逻辑功能,与计算得到的真值表进行比较,验证所设计的逻辑电路是否符合要求。 电路实验箱实物连接:在实验装置适当位置选定三个14P 插座,按照集成块定位标记插好集成块74LS20。按化简得到的逻辑图接线,输入端 A、B、C、D 接至逻辑开关输出插口,输出端 Z 接逻辑电平显示输入插口,按真值表(自拟)要求,逐次改变输入变量,测量相应的输出值,验证逻辑功能,与计算得到的真值表进行比较,验证所设计的逻辑电路是否符合要求。 (二)LED显示电路 1.电路实验箱上的LED原理: 7段数码显示管(LED)是由7个单独LED二极管组合而成(忽略小数点),经常用来显示0-9 这些数字。它可以用 4个输入项A-B-C-D和7个输出项a~g的逻辑关系真值表来表达。CD4511芯片能够完成这种对应关系的转换。 各引脚及其对应控制的发光二极管对照图如下所示: CD4511芯片原理图及其真值表: 四个输入端A、B、C、D利用与非门在电路实验箱上用12个输入表达三个为一组表示A、B、C、D。即只有每组三个输入端全为1时对应的CD4511芯片的某个输入才为1。 电路实验箱接法如下: 在做此实验时出现的问题: LED显示实验若想在第一个表决器实验的基础上做延伸,就不能使用原本的电路箱4输入端,因为端口之间会出现重合排斥,无法读出真值表上的数值(消隐),则在此实验上采用了12输入端表示CD4511芯片上的4输入端的方法就不会重叠。 (三)组合逻辑电路化简 在上篇《基本逻辑门电路硬件验证与仿真分析》文章中有一个逻辑图,如下图所示。  Z的简化电路为: Z的简化电路为: 即原电路化简为: 即原电路化简为:

|

【本文地址】