计算机组成原理课后答案(唐朔飞第三版) 第三章 |

您所在的位置:网站首页 › 计算机组成原理与接口技术第二版课后答案 › 计算机组成原理课后答案(唐朔飞第三版) 第三章 |

计算机组成原理课后答案(唐朔飞第三版) 第三章

|

计算机组成原理课后答案(唐朔飞第3版)

第3章 系统总线

教材课后思考题与习题:

3.1 什么是总线?总线传输有何特点?为了减轻总线负载,总线上的部件应具备什么特点?

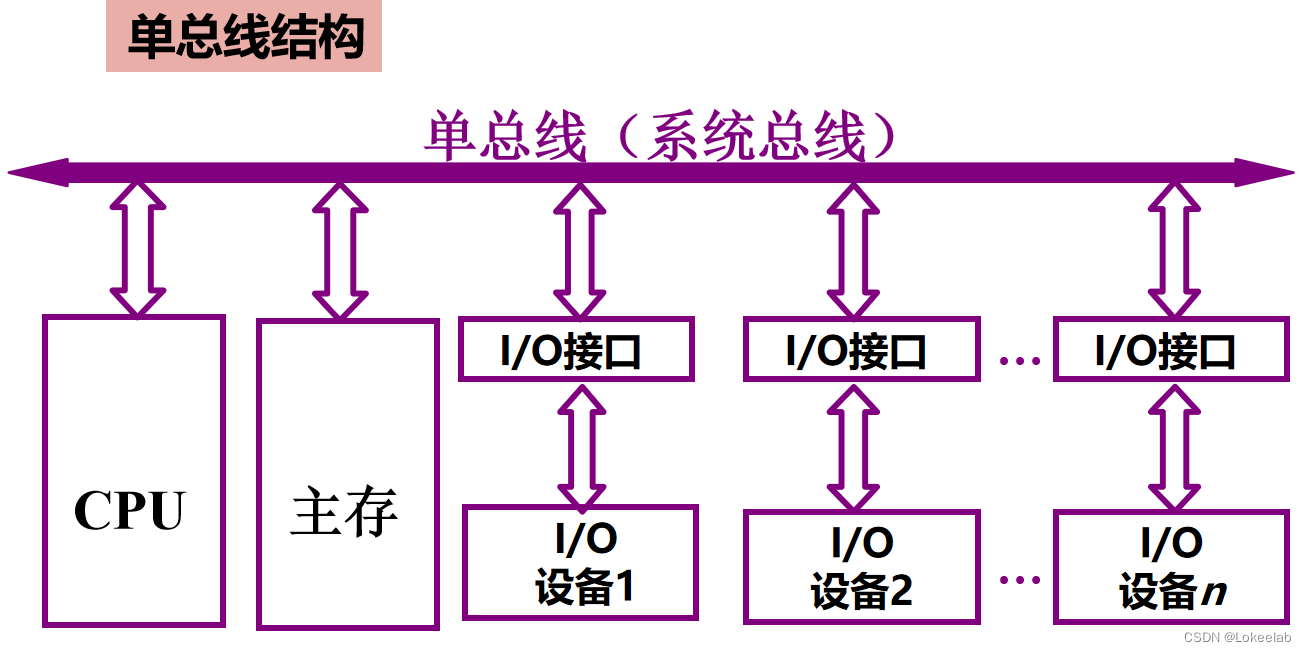

总线:连接多个部件(模块)的信息传输线,是各部件共享的传输介质。 总线传输特点:某一时刻,只允许有一个部件向总线发送信息,而多个部件可以同时从总线上接收相同的信息。 为了减轻总线上的负载,各种 I/O 设备要通过 I/O 接口接在总线上,而且还要通过三态门挂在总线上,没有数据交换时置成高阻态。 3.2 总线如何分类?什么是系统总线?系统总线又分为几类,它们各有何作用,是单向的,还是双向的,它们与机器字长、存储字长、存储单元有何关系?总线分类: 按数据的传输方式: 分为并行传输总线和串行传输总线按使用范围: 分为计算机总线、测控总线、网络通信总线按连接部件: 片内总线、系统总线、通信总线系统总线: 指CPU、主存、I/O设备(通过I/O接口)各大部件之间的信息传输线。按照系统总线传输信息的不同,又可分为三类:数据总线、地址总线和控制总线: 数据总线: 用来传输各功能部件之间的数据信息,它是双向传输总线,其位数与机器字长、存储字长有关,一般为8位、16位或32位。 地址总线: 用来指出数据总线上的源数据或目的数据在主存单元的地址或 I/O设备的地址。单向传输,其位数与存储单元的个数有关(几次幂的关系)。 控制总线: 用来发出各种控制信号的,对任意控制线而言,是单向的。与机器字长、存储字长、存储单元无关。 3.3 常用的总线结构有几种?不同的总线结构对计算机的性能有什么影响?举例说明。 单总线结构:

将CPU、主存、I/O设备(通过I/O接口)都挂到一组总线上,允许I/O设备之间、I/O设备与CPU之间或I/O设备与主存之间直接交换信息。 特点: 结构简单,便于扩充,但所有的传送都通过这组共享总线,因此极易形成计算机系统的瓶颈。它也不允许两个以上的部件在同一时刻向总线传输信息,这就必然会影响系统工作效率的提高。 双总线结构:

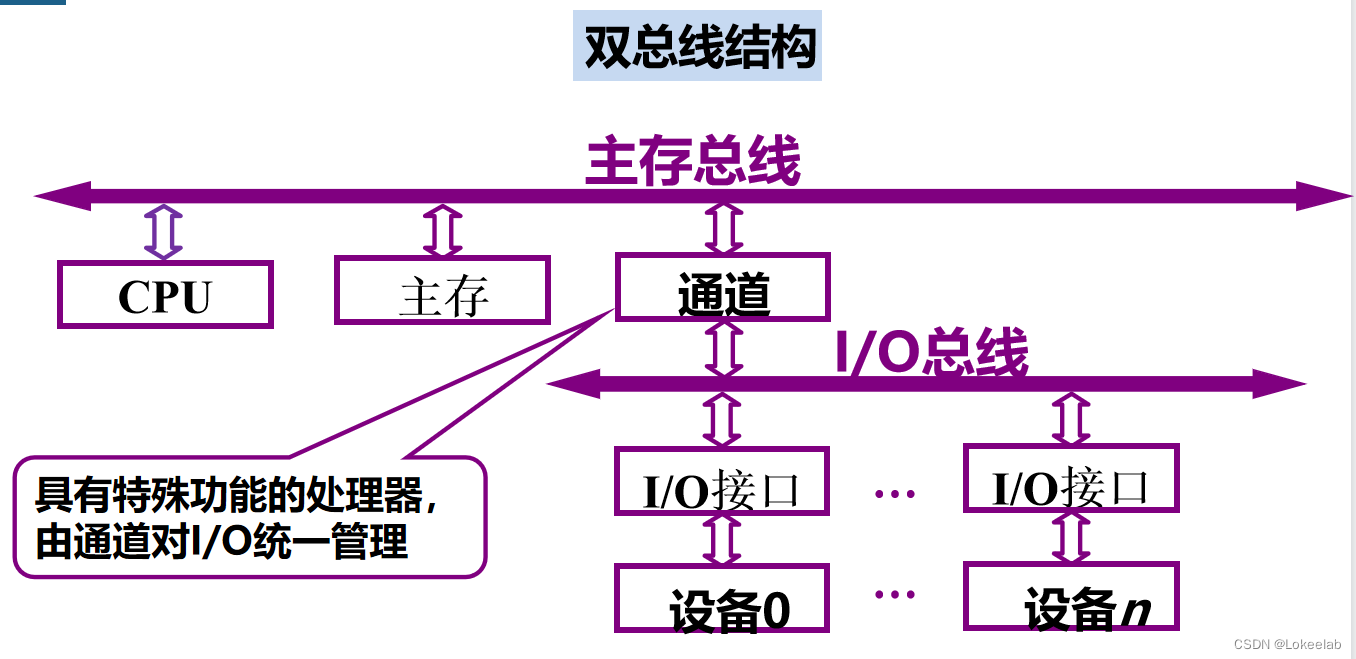

将速度较低的 I/O设备从单总线上分离出来,形成主存总线与I/O总线分开的结构。图中通道是一个具有特殊功能的处理器,CPU将一部分功能下放给通道,使其对I/O设备具有统一管理的功能,以完成外部设备与主存储器之间的数据传送,其系统的吞吐能力可以相当大。此结构多用于大、中型计算机系统。 如果将速率不用的I/O设备进行分类,然后将它们连接在不同的通道上,那么计算机系统的工作效率将会更高,由此发展成多总线结构。 三总线结构1:

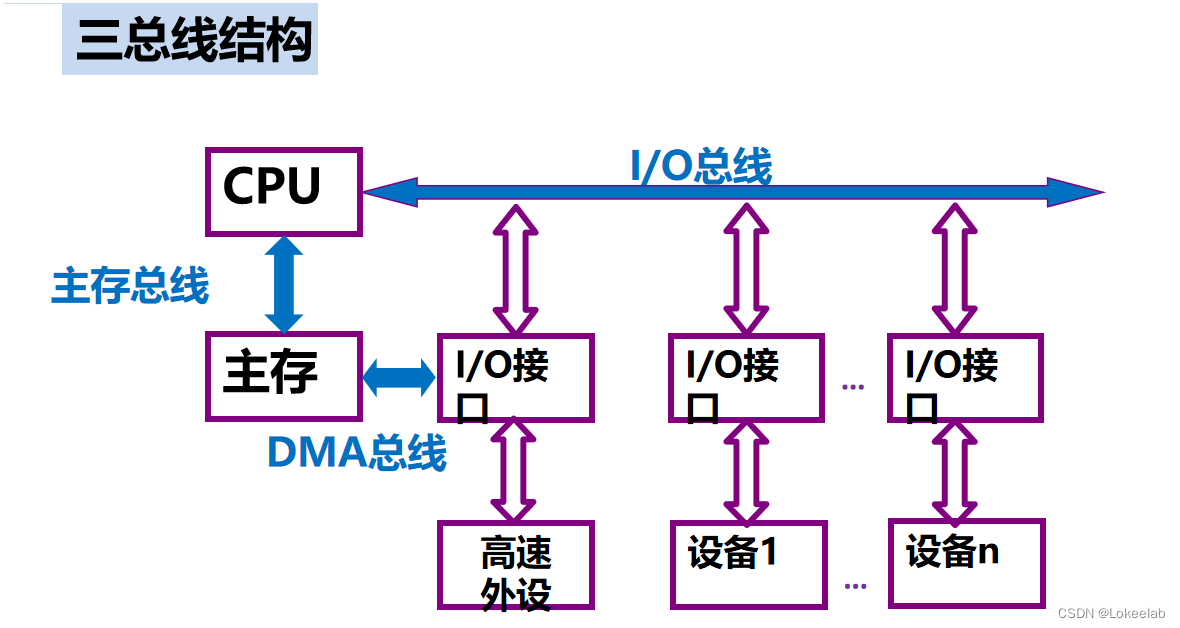

主存总线用于CPU与主存之间的传输;I/O总线供CPU与各类I/O设备之间的传递信息;DMA总线用于高速I/O设备(磁盘、磁带等)与主存之间直接交换信息。 在三总线结构中,任一时刻只能使用一种总线。主存总线与DMA总线不能同时对主存进行存取,I/O总线只有在CPU执行I/O指令时才能用到。 三总线结构2:

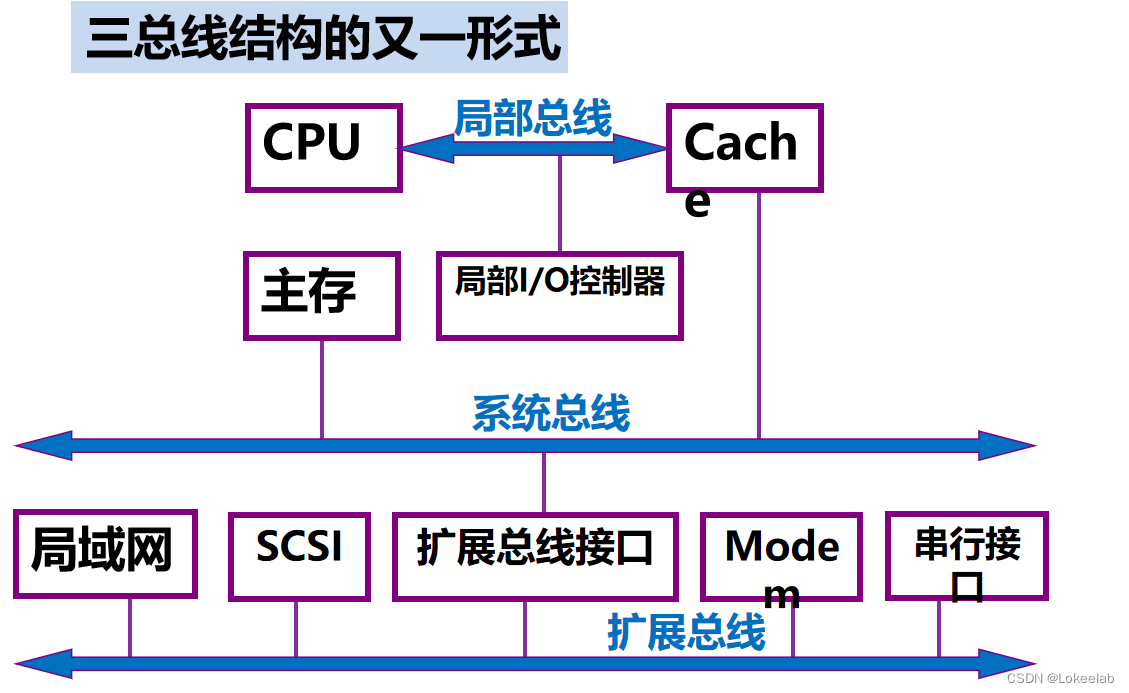

处理器与Cache之间有一条局部总线,它将CPU与Cache或与更多的局部设备连接。 Cache的控制机构不仅将Cache连到局部总线上,而且还直接连接到系统总线上,这样Cache就可以通过系统总线与主存传输信息,而且I/O设备与主存之间的传输也不必通过CPU。 还有一条扩展总线,它将局域网、小型计算机接口(SCSI)、调制解调器(Modem)以及串行接口等都连接起来,并且通过这些接口又可与各类I/O设备相连,因此它可以支持相当多的I/O设备。与此同时,扩展总线又通过扩展总线接口与系统总线相连,由此便可实现这两种总线之间的信息传递,可见其系统的工作效率明显提高。 四总线结构:

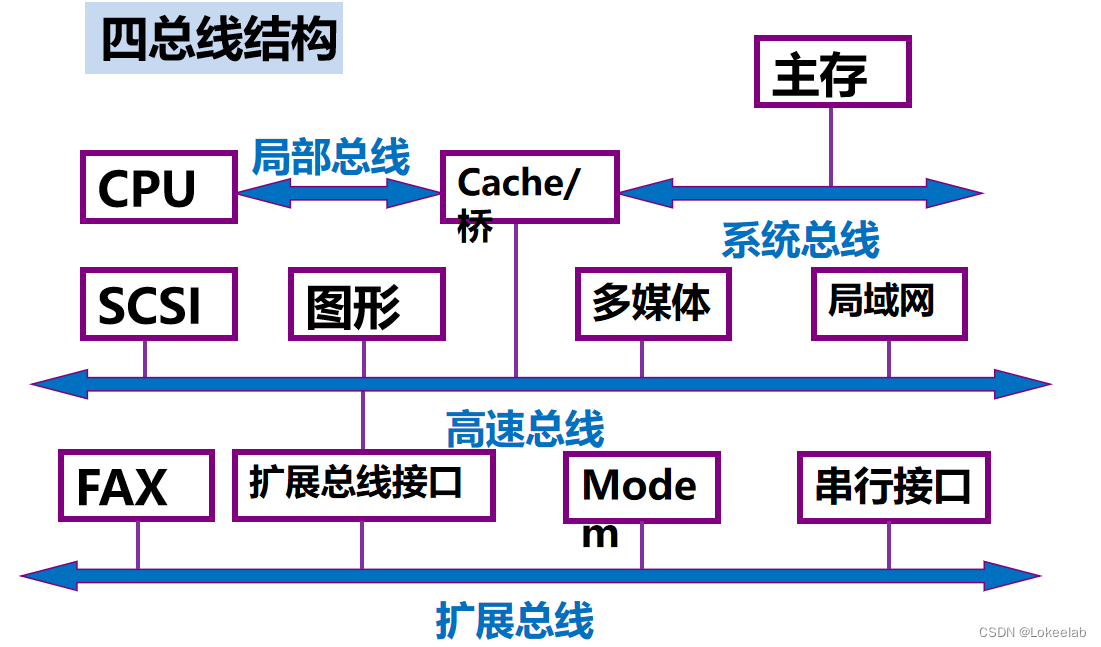

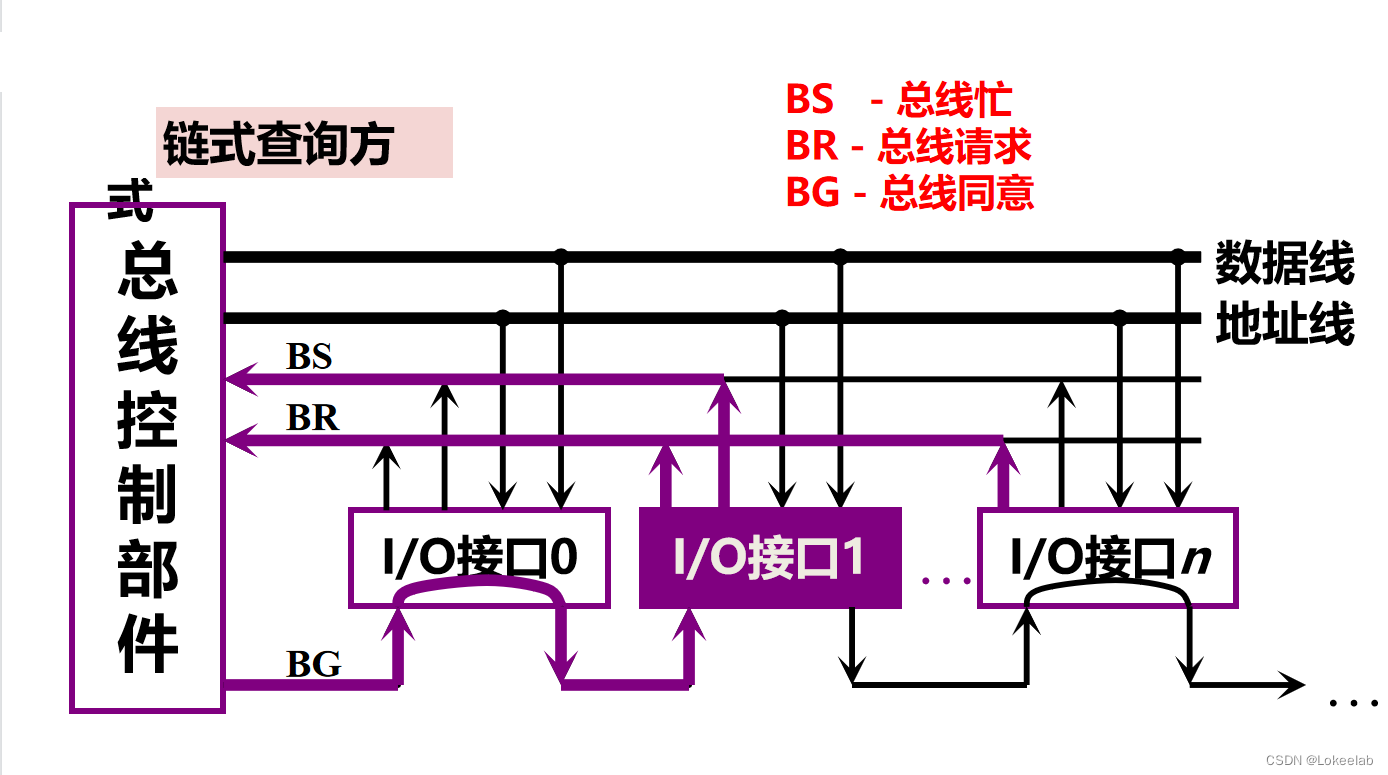

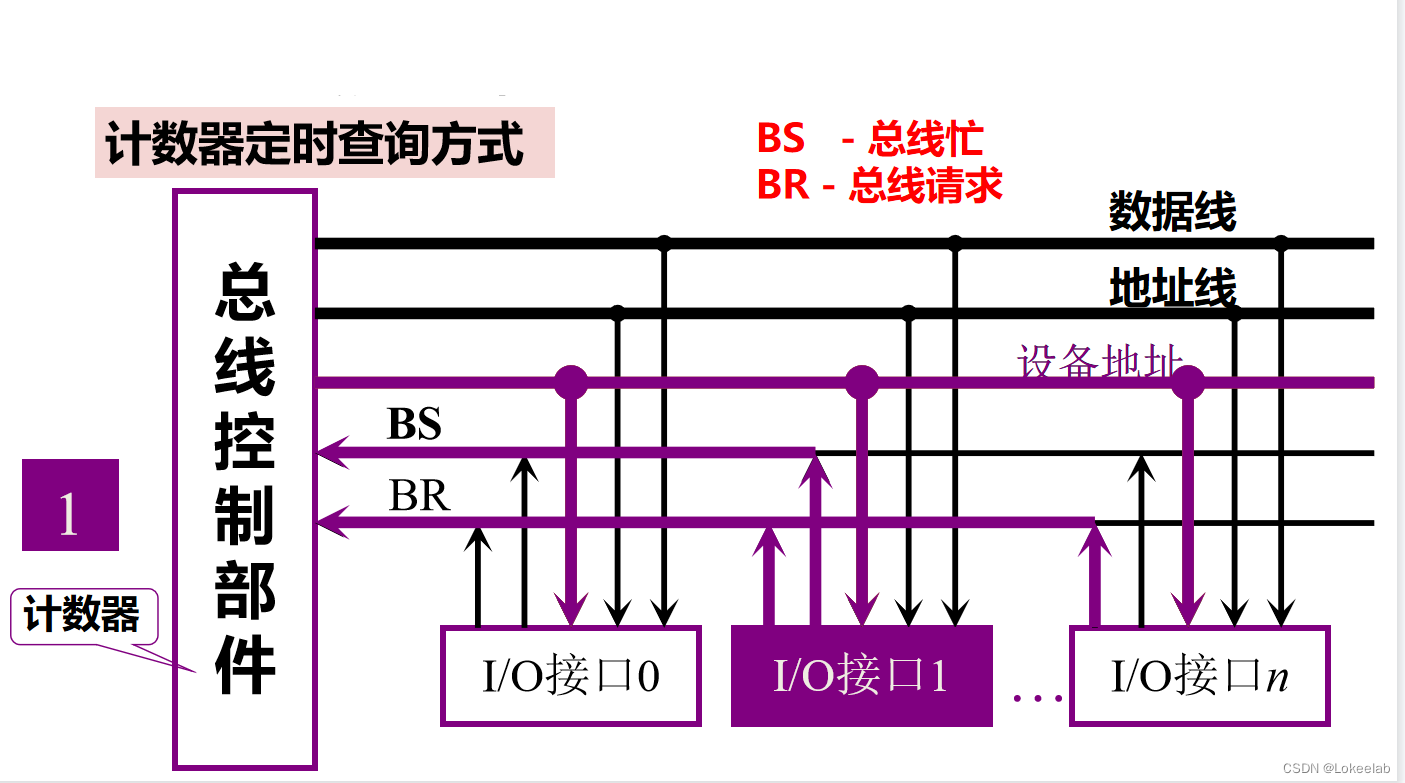

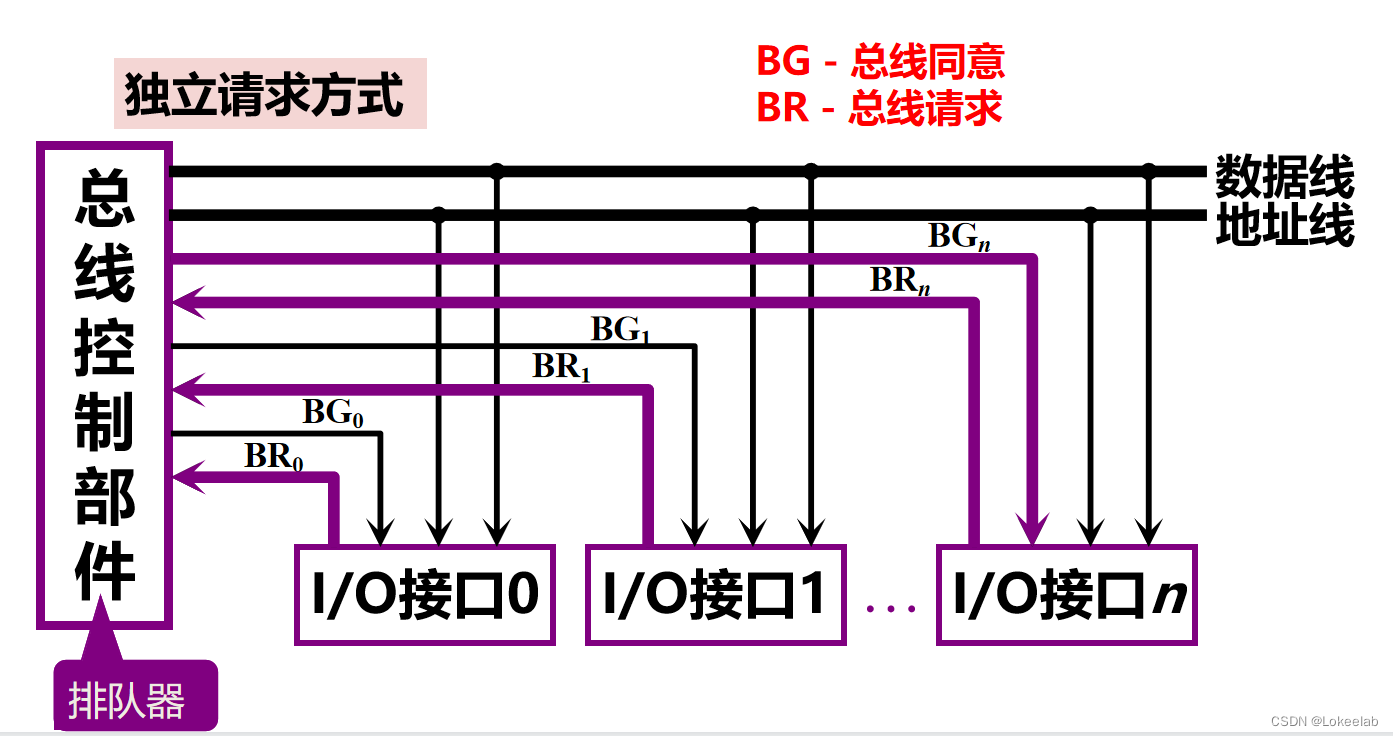

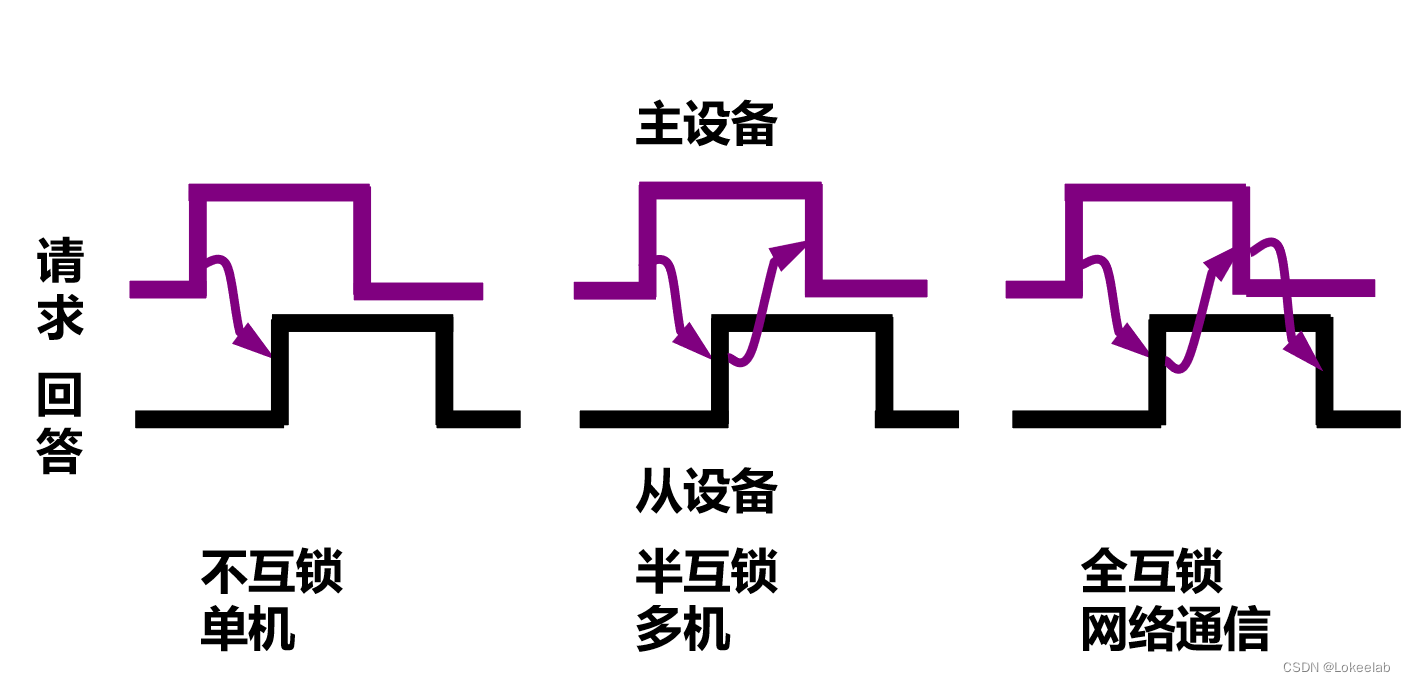

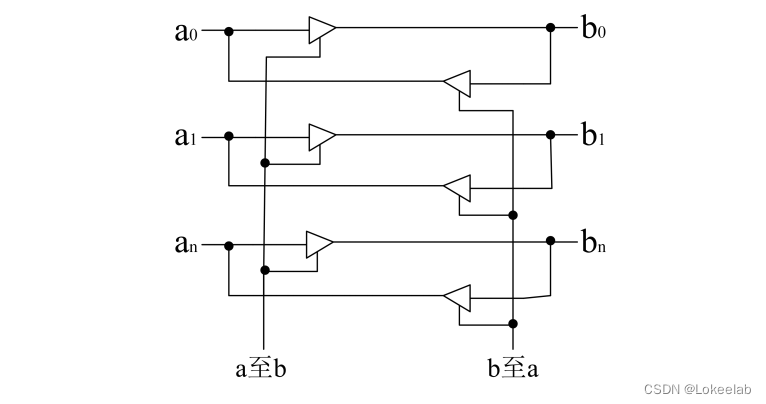

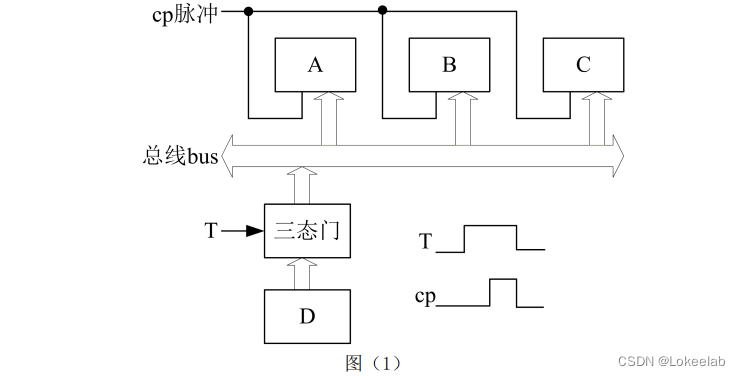

在三总线结构的基础之上,又增加了一条与计算机系统紧密相连的高速总线。在高速总线上挂接了一些高速I/O设备,如高速局域网、图形工作站、多媒体、SCSI等。它们通过Cache控制机构中的高速总线桥或告诉缓冲器与系统总线和局部总线相连,使得这些高速设备与CPU更紧密。 而一些较低速设备如图文传真FAX、调制解调器及串行接口仍挂在扩展总线上,并由扩展总线接口与高速总线相连。 这种结构对高速设备而言,其自身的工作可以很少依赖CPU,同时它们又比扩展总线上的设备更贴近CPU,可见对于高性能设备与CPU来说,各自的效率将获得更大的提高。 3.4 为什么要设置总线判优控制?常见的集中式总线控制有几种?各有何特点?哪种方式响应时间最快?哪种方式对电路故障最敏感?为什么要设置总线判优控制? 因为总线传输的特点就是在某一时刻,只允许一个部件向总线发送信息,如果有两个以上的部件同时向总线发送信息,势必导致信号冲突传输无效,故需要判优解决。 常见的集中式总线控制: 1)链式查询: 链式查询中,用了3根线来实现总线判优控制:BS(Bus State)、BR(Bus Request)、BG(Bus Grant)。而BG线是串行的连接了多个I/O接口,这也是”链式查询“名称的由来。 该判优控制过程: 比如I/O接口1 和I/O接口n,都通过BR线向总线控制部件提出申请占用总线,总线控制部件收到总线占用的请求,这时还并不知道是哪一个接口发出的总线占用请求,得通过BG线去链式查找(按接口排列顺序一个个的往下查找)。如查找到第一个发送占用请求的I/O接口1时,就再继续往下查找,I/O接口1通过BS线发送总线忙的信号,表示I/O接口1占用了总线。 特点: 只需要很少的几根线就能按一定的优先次序实现总线控制,并且很容易扩充设备,但对电路故障很敏感,且优先级别低的设备可能很难获得请求。 2)计数器定时查询: 计数器定时查询中,实现总线判优控制的主要是3根线:BS(Bus State)、BR(Bus Request)、设备地址线。而设备地址线也是该名称”计数器定时查询“名称的由来。 该判优控制过程: 如上图,I/O接口1和I/O接口n,通过BR线向总线控制部件发出占用总线的请求,总线控制部件内部有一个计数器,该计数器用来标识下面要去查找的是哪一个I/O接口。比如计数器为”0“,总线控制部件就通过设备地址线去查找I/O接口0,然而发现I/O接口0并没有发出占用请求,那么计数器累加得”1“,总线控制部件又通过设备地址线去查找I/O接口1,发现I/O接口1发出过总线占用请求,因此I/O接口1获得总线使用权,终止计数查询。所以:仅当计数值 = 发占用请求的设备地址时,该设备便获得总线使用权。 特点: 计数可以从”0“开始,此时一旦设备的优先次序被固定,设备的优先级就按0,1,…,n的顺序排列,而且固定不变;计数也可以从上一次计数的终止点开始,即是一种循环方法,此时设备使用总线的优先级相等;计数器的初始值还可以由程序设置,故优先次序可以改变。这种方式对电路故障不如链表查询方式敏感,但增加了控制线(设备地址)数,控制也较复杂。 3)独立请求方式: 独立请求方式中: 每个I/O设备都有一对总线请求线BR和总线同意线BG。 该判优控制过程:当某几个设备要求使用总线时,便通过各自独立的总线请求线BR发出该设备的请求信号。总线控制部件内部有一个排队器电路,可根据优先次序确定响应那一台设备发出的请求。 特点: 影响速度快,优先次序控制灵活(通过程序改变),但控制线数量多,总线控制更复杂。 3.5 解释下列概念:总线宽度、总线带宽、总线复用、总线的主设备(或主模块)、总线的从设备(或从模块)、总线的传输周期和总线的通信控制。总线宽度: 通常是指数据总线的根数,用bit(位)表示,如8位、16位、32位、64位(即8根、16根、32根、64根) 总线带宽: 总线的数据传输速率,即单位时间内总线上传输数据的位数,通常用每秒传输信息的字节数来衡量,即MBps。 总线复用: 地址线 与 数据线 复用 总线的主设备(或主模块): 对总线有控制权连接设备 总线的从设备(或从模块): 只能响应从主设备发来的总线命令,对总线没有控制权 总线的传输周期: 连接在总线上的两个部件完成一次完整且可靠的信息传输时间 总线的通信控制: 解决通信双方如何获知传输开始和传输结束,以及通信双方如何协调如何配合 3.6 试比较同步通信和异步通信。同步通信和异步通信的主要区别是: 前者 有公共时钟,总线上的所有设备按统一的时序、统一的传输周期进行信息传输,通信双方按约定好的时序联络; 后者 没有公共时钟,没有固定的传输周期,采用应答方式通信,具体的联络方式有不互锁、半互锁和全互锁三种。 不互锁方式通信双方没有相互制约关系;半互锁方式通信双方有简单的制约关系;全互锁方式通信双方有完全的制约关系。其中全互锁通信可靠性最高。 3.7 画图说明异步通信中请求与回答有哪几种互锁关系?

1)不互锁方式: 主模块发出请求请求信号后,不必等待从模块的回答信号,而是经过一段时间,确认从模块已收到请求信号后,便撤销其请求信号;从模块接收请求信号后,在条件允许时发出回答信号,并且经过一段时间(这段时间的设置对不同设备而言是不同的)确认主模块已收到回答信号后,自动撤销回答信号。 2)半互锁方式: 主模块发出请求信号,必须待接到从模块的回答信号后再撤销其请求信号,有互锁关系;而从模块在接到请求信号后发出回答信号,但不必等待获知主模块的请求信号已经撤销,而是隔一段时间后自动撤销其回答信号,无互锁关系。由于一方存在互锁关系,一方不存在互锁关系,故称为半互锁方式。 3)全互锁方式: 主模块发出请求信号后,必须待从模块回答后再撤销其请求信号;从模块发出回答信号后,必须待获知主模块请求信号已撤销后,再撤回其回答信号。双方存在互锁关系,故称为全互锁方式。 3.8 为什么说半同步通信同时保留了同步通信和异步通信的特点?保留同步信息特点: 发送方用系统时钟前沿发信号,接收方用系统时钟后沿判断、识别 保留异步通信特点: 允许不同速度的模块和谐工作,增加一条”等待“响应信号(WAIT) 3.9 分离式通讯有何特点,主要用于什么系统?特点: 各模块欲占用总线使用权都必须提出申请; 在得到总线使用权后,主模块在先定的时间内向对方传送信息,采用同步方式传送,不再等待对方的回答信号; 各模块在准备数据的过程中都不占用总线,使总线可接受其它模块的请求; 总线被占用时都在做有效工作,或者通过它发送命令,或者通过它传送数据,不存在空闲等待时间,充分利用了总线的占用,从而实现了总线在多个主、从模块间进行信息交叉重叠并行传送。 分离式通讯主要用于大型计算机系统。 3.10 为什么要设置总线标准?你知道目前流行的总线标准有哪些?什么叫plug and play?哪些总线有这一特点?制定总线标准使系统设计简化,便于模块化生产批量化,确保其性能稳定,质量可靠,实现可移化,便于维护等,较好地解决了系统、模块、设备与总线之间不适应、不通用及不匹配的问题。 目前流行的总线标准有:ISA、EISA、PCI等。 plug and play:即插即用,EISA、PCI等具有此功能。 3.11 画一个具有双向传输功能的总线逻辑图。答:在总线的两端分别配置三态门,就可以使总线具有双向传输功能。 (1) 设计一个电路,在同一时间实现D→A、D→B和D→C寄存器间的传送; (2) 设计一个电路,实现下列操作: T0时刻完成D→总线; T1时刻完成总线→A; T2时刻完成A→总线; T3时刻完成总线→B。 解: (1)由 T 打开三态门将 D 寄存器中的内容送至总线 bus,由 cp 脉冲同时将总线上的数据打 入到 A、B、C 寄存器中。 T 和 cp 的时间关系如图(1)所示。 总线数据传输率即总线带宽,指单位时间内总线上传输数据的位数,通常用每秒传输信息的字节数来衡量。 它与总线宽度和总线频率有关,总线宽度越宽,频率越快,数据传输率越高。 例如: 总线工作频率为33MHz,总线宽度为32位(4 Byte),则总线的宽度为33 x 4 = 132MBps。 3.14 设总线的时钟频率为8MHZ,一个总线周期等于一个时钟周期。如果一个总线周期中并行传送16位数据,试问总线的带宽是多少?由于:f=8MHz,T=1/f=1/8M秒,一个总线周期等于一个时钟周期 所以:总线带宽=16/(1/8M) = 128Mbps 2.15 在一个32位的总线系统中,总线的时钟频率为66MHZ,假设总线最短传输周期为4个时钟周期,试计算总线的最大数据传输率。若想提高数据传输率,可采取什么措施?总线传输周期=4*1/66M秒 总线的最大数据传输率=32/(4/66M)=528Mbps 若想提高数据传输率,可以提高总线时钟频率、增大总线宽度或者减少总线传输周期包含的时钟周期个数。 3.16 在异步串行传送系统中,字符格式为:1个起始位、8个数据位、1个校验位、2个终止位。若要求每秒传送120个字符,试求传送的波特率和比特率。一帧包含: 1+8+1+2=12位 波特率: 单位时间内传送二进制数据的位数,单位用bps(位/秒),故波特率为:(1+8+1+2)120=1440bps 比特率: 单位时间内传送二进制有效数据的位数,单位用bps表示,故比特率为:8120=960bps |

【本文地址】

今日新闻 |

推荐新闻 |

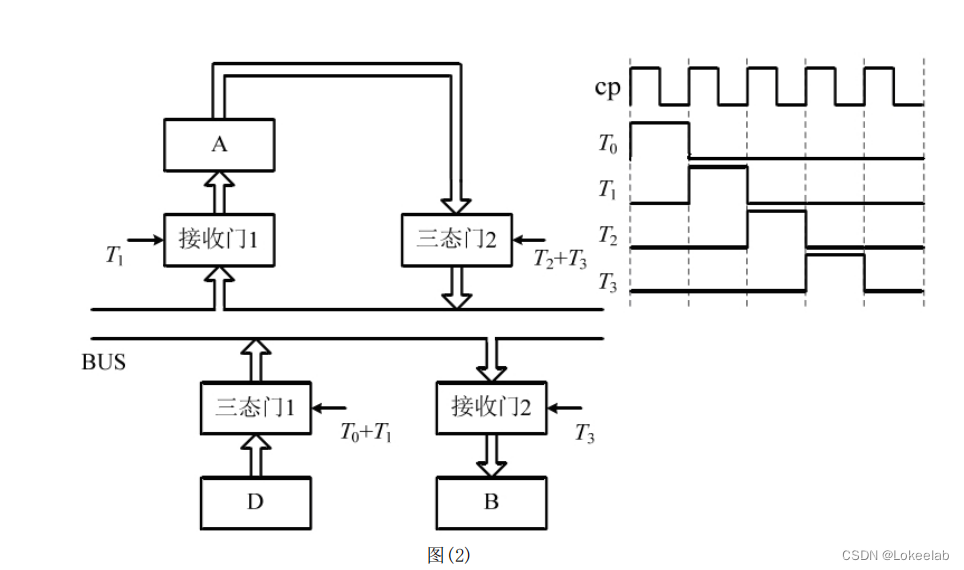

(2)三态门 1 受 T0+T1 控制,以确保 T0 时刻 D→总线,以及 T1 时刻总线→接收门 1→A。 三态门 2 受 T2+T3 控制,以确保 T2 时刻 A→总线,以及 T3 时刻总线→接收门 2→B。T0、T1、 T2、T3 波形图如图(2)所示。

(2)三态门 1 受 T0+T1 控制,以确保 T0 时刻 D→总线,以及 T1 时刻总线→接收门 1→A。 三态门 2 受 T2+T3 控制,以确保 T2 时刻 A→总线,以及 T3 时刻总线→接收门 2→B。T0、T1、 T2、T3 波形图如图(2)所示。