RTL开发笔记 |

您所在的位置:网站首页 › 计算机基础知识教案中职下册 › RTL开发笔记 |

RTL开发笔记

|

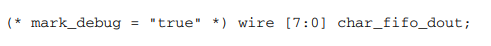

在进行code review的时候经常能得到来自资深工程师的建议,就在这里汇总一下。自己也在努力尝试定期分享知识,这些日常工作正好也成为了很好的源泉。自己见识有限,干货不多,也是趁此希望逐步建立知识体系。 Flag立完,进入正题。上次的code review的时候,就有大佬让我把verilog源码里的逻辑有关mark debug的true属性全部移除。例如这个:

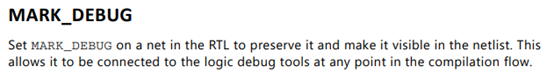

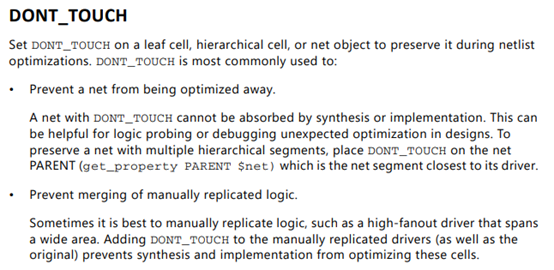

原因就是这些属性会限制工具对这些逻辑进行的优化,这就会给后续的place&route和时序收敛带来困难。以前的一个项目就因为太多的逻辑被这个mark_debug=true 限制住而导致不容易收敛时序。 而用上mark_debug=true 则是因为需要将信号连接到ILA来进行分析调试,Xilinx 对这个属性的描述如下(UG903):

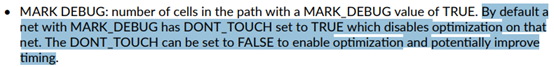

意思很明显,就是专门为调试服务的,那调试结束去掉也就理所应当。我个人对这个属性最大的印象就是加上之后,信号的名字可以直接在logic analyzer上面显示,不会被其他奇怪的中间带net的名字代替。但是上面的描述仅仅提到可视化的问题,没有太多有关优化上面的解释。 这个在另一个文档(ug835)有了线索:

这里就明显提到了优化。原来mark_debug=true自带了一个dont_touch=true,看来一下dont_touch的描述就了然了。

大家记得调试完逻辑后把mark_debug这些清除掉哈。

参考文献: Xilinx UG903,UG908, UG835. |

【本文地址】

今日新闻 |

推荐新闻 |