FPGA 矩阵转置 |

您所在的位置:网站首页 › 矩阵转置的代码是什么 › FPGA 矩阵转置 |

FPGA 矩阵转置

|

这里写目录标题

1 功能2 开发环境3 框架4 转置公式5 Simulation第一部分第二部分第三部分

6 Matlab代码产生FIFO数据产生转置矩阵

7 HDL仿真文件顶层文件FIFO顶层文件FIFO读FIFO写RAM顶层文件

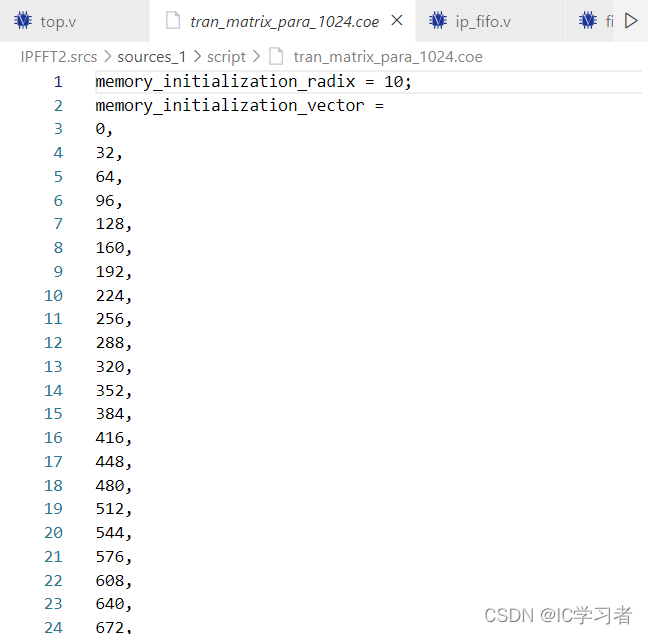

8 IP配置FIFORAMROM

9 Reference

1 功能

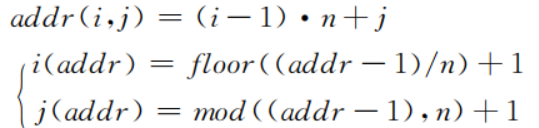

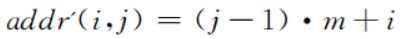

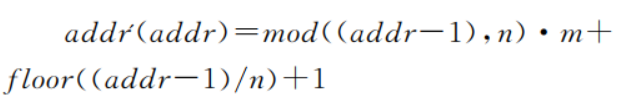

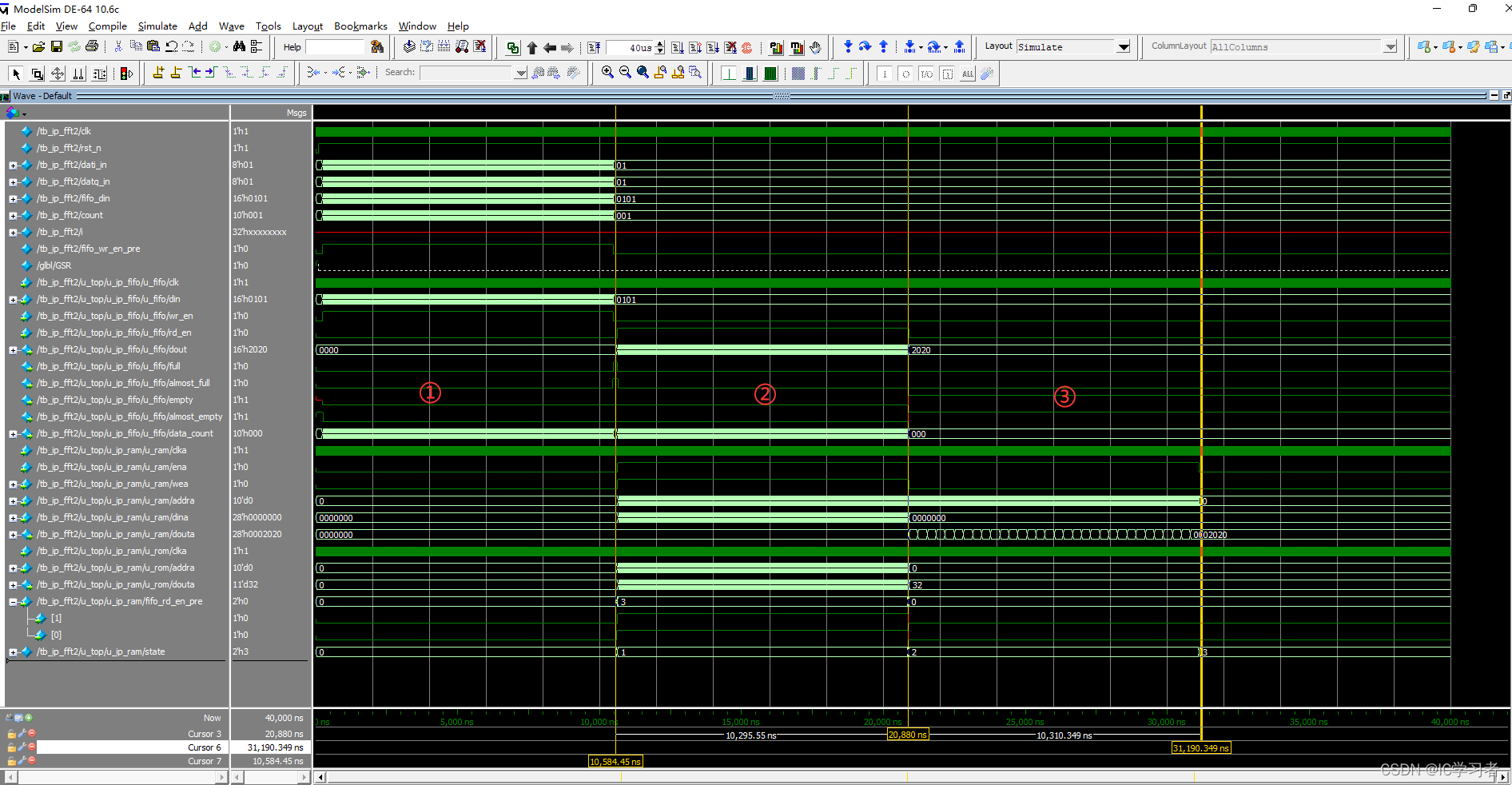

通过tb读取本地数据保存到FIFO,通过coe文件将转置后的地址数据保存在ROM中,读取FIFO的文件作为输入,读取ROM作为地址。通过地址变换,对矩阵进行转置,最终将转置后的矩阵保存在RAM中。 2 开发环境Vivado 3 框架

来源见 Reference

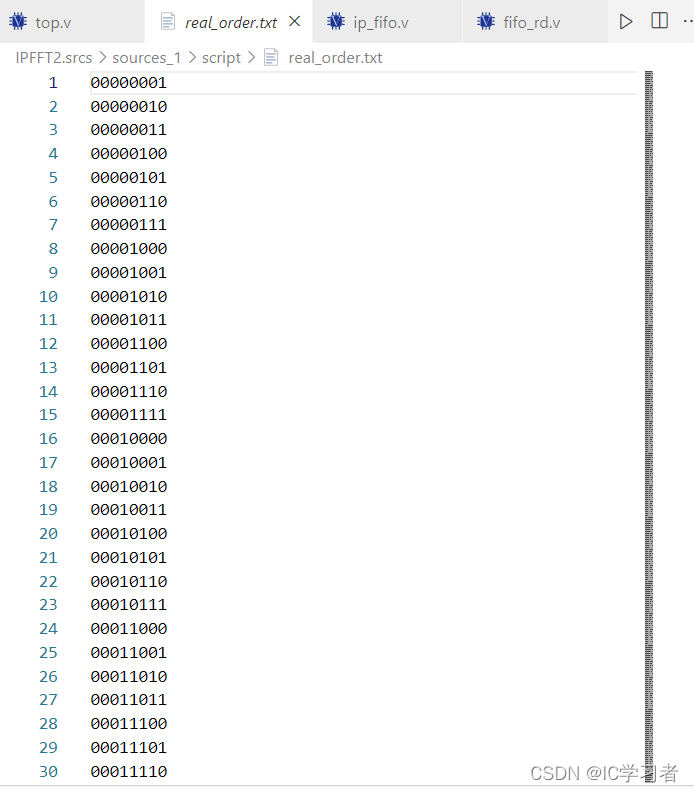

通过tb将数据写到FIFO中,此部分数据为两路(1:32)*32。 这里的数据也就是转置前的数据,每行从1增长到32,总共32行。 第二部分从FIFO中读取数据。 从ROM中读取地址,此地址为转置后的地址。 将FIFO中的数据按ROM中的地址写入到RAM中。 第三部分读取RAM,可以从波形上看到转置的效果。 本来每行是1到32逐渐增加,现在每行为1到32中的一个数。 转置成功! 6 Matlab代码 产生FIFO数据 %% export to bin file % specifying a signed, fixed-point data type, rounding towards negative infinity, and saturate on overflow. struct.mode = 'fixed'; struct.roundmode = 'floor'; struct.overflowmode = 'saturate'; struct.format = [8 0]; % 8位二进制数,0位小数,默认1位符号位 q=quantizer(struct); miu1_real = zeros(32,32); for i = 1:32 miu1_real(:,i) = i; end miu1_imag = miu1_real; % 量化值与实际值的误差 q_miu1_real = quantize(q,miu1_real); q_miu1_imag = quantize(q,miu1_imag); disp("最大量化误差"); disp(max(max([abs(miu1_real-q_miu1_real),abs(miu1_imag-q_miu1_imag)]))); % 按行转为列向量 real_o = num2bin(q, reshape(miu1_real', [], 1)); imag_o = num2bin(q, reshape(miu1_imag', [], 1)); % 按列转为列向量 % real_o = num2bin(q,miu1_real(:)); % imag_o = num2bin(q,miu1_imag(:)); %% 将数据写入TXT fid1=fopen('F:\MyTest\FPGA\IPFFT2\IPFFT2.srcs\sources_1\script/real_order.txt','wt'); fid2=fopen('F:\MyTest\FPGA\IPFFT2\IPFFT2.srcs\sources_1\script/imag_order.txt','wt'); for i=1:32*32 fwrite(fid1,real_o(i,:)); fprintf(fid1,'\n'); fwrite(fid2,imag_o(i,:)); fprintf(fid2,'\n'); end fclose(fid1); fclose(fid2);数据 数据 |

【本文地址】

包含IP:FIFO、RAM和ROM

包含IP:FIFO、RAM和ROM

imag_order内容一致

imag_order内容一致