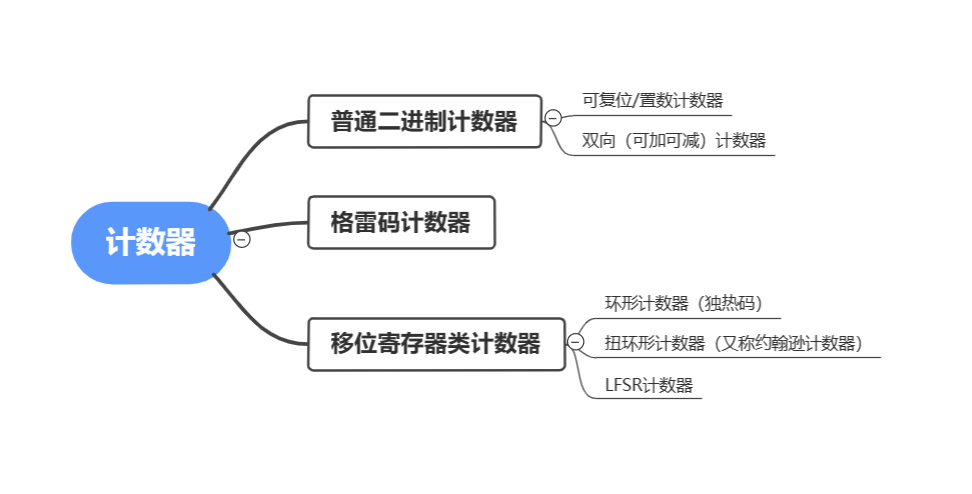

七种常见计数器总结(格雷码计数器、环形计数器、约翰逊计数器、FLSR、简易时分秒数字秒表等 |

您所在的位置:网站首页 › 环形图的特点是什么 › 七种常见计数器总结(格雷码计数器、环形计数器、约翰逊计数器、FLSR、简易时分秒数字秒表等 |

七种常见计数器总结(格雷码计数器、环形计数器、约翰逊计数器、FLSR、简易时分秒数字秒表等

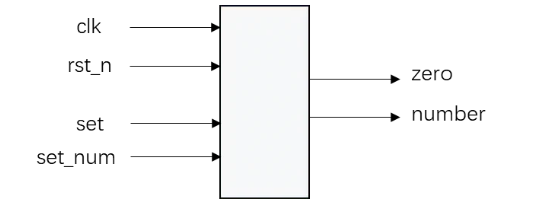

数字IC经典电路设计 经典电路设计是数字IC设计里基础中的基础,盖大房子的第一部是打造结实可靠的地基,每一篇笔者都会分门别类给出设计原理、设计方法、verilog代码、Testbench、仿真波形。然而实际的数字IC设计过程中考虑的问题远多于此,通过本系列希望大家对数字IC中一些经典电路的设计有初步入门了解。能力有限,纰漏难免,欢迎大家交流指正。快速导航链接如下: 个人主页链接 1.数字分频器设计 2.序列检测器设计 3.序列发生器设计 4.序列模三检测器设计 5.奇偶校验器设计 6.自然二进制数与格雷码转换 7.线性反馈移位寄存器LFSR 8.四类九种移位寄存器总结 9.串并转换 一、可复位/置数计数器1.1 可复位/置数计数器根据要求可以知道有四个输入和两个输出,主要包括累加计数、置位、指示信号,此题较简单,分开设计即可。 模块的接口信号图如下:  1.2 Verilog代码 1.2 Verilog代码要求:设计一个位宽为4的带复位端和置位端的计数器,并且计数器输出信号递增每次到达0,指示信号zero拔高至“1”,当置位信号set 有效时,将当前输出置为输入的数值set_num。 代码语言:c复制//可复位可置位的简易计数器 module count_bin01( input clk, input rst_n, input set, input [3:0] set_num, output reg [3:0]number, output reg zero ); reg [3:0] cnt; always@(posedge clk or negedge rst_n)begin if(!rst_n) begin cnt > 1) ^ cnt_bin_r; //时序逻辑打一拍子输出 always@(posedge clk or negedge rst_n) begin if(!rst_n) begin cnt_gray |

【本文地址】

今日新闻 |

推荐新闻 |