芯片生产封装过程简介及概念 |

您所在的位置:网站首页 › 本征半导体的定义 › 芯片生产封装过程简介及概念 |

芯片生产封装过程简介及概念

|

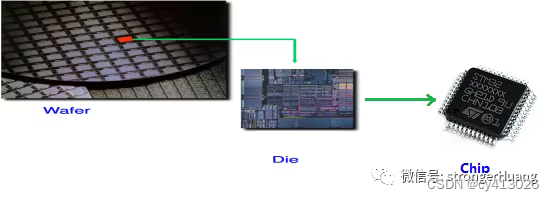

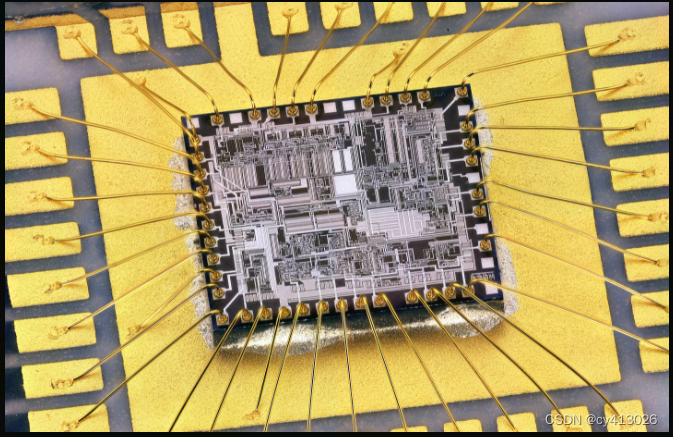

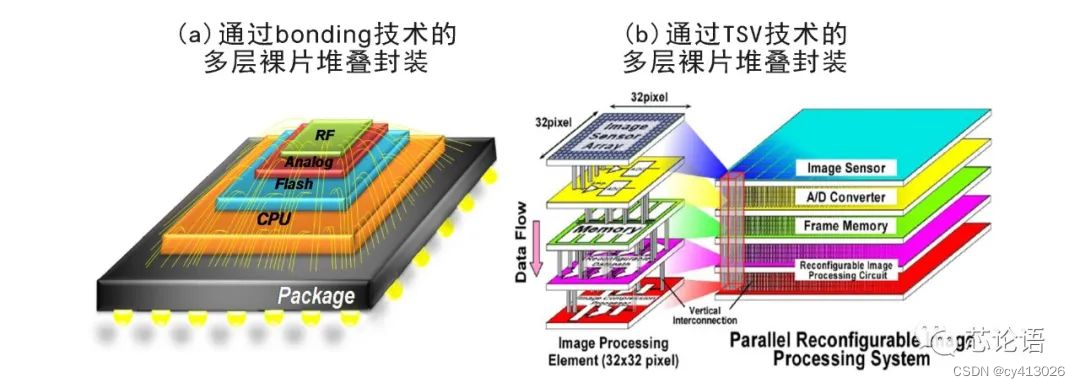

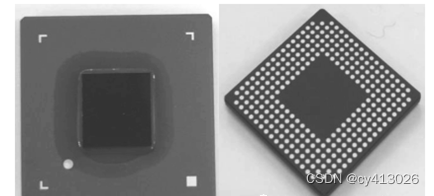

1.wafer,die,chip,cell的概念 wafer(晶圆):高纯度的多晶硅溶解后掺入硅晶体晶种,然后慢慢拉出,形成圆柱形的单晶硅。硅晶棒在经过研磨,抛光,切片后,形成硅晶圆片,也就是晶圆。 晶圆----维基百科 半导体---维基百科 半导体的制作材料主要是半导体材料Si(硅)【还有其他一些半导体材料】,纯硅是来自主要成分为SiO2的砂子,但是纯硅的导电性太弱,不能满足芯片制造的需求,这时就要做本征半导体的掺杂。向本征型材料或天然材料中添加杂质的过程称为掺杂,而杂质则称为掺杂剂。掺杂后,本征型材料变成了非本征型材料。实际上,只有在进行掺杂之后,这些材料才会变得可用。 根据掺杂的杂质类型分为了N型【杂质原子带多电子】和P型【杂质原子少带电子hole】。 die(晶粒,裸片/裸芯片):die是硅片中一个很小的单位,包括了设计完整的单个芯片以及芯片邻近水平和垂直方向上的部分划片槽区域。可以理解为die是没有封装也没有引脚的芯片【这里不包括一个封装里面多个die的情况】。可能一个基带做成了一个die,也可能是一个视频编解码die,gpu die,一颗低算力的adas芯片做成一个die。大芯片很可能要做成多个die,然后封装在一起或者分开封装。 chip:常见的意义应该是封装好了,包含引脚的芯片 cell:是更小的集合,一个门器件可以称呼为cell,一个乘法器也可以称为一个cell。 说到这里chip和cell比较好理解,die和wafer又是什么关系呢? 芯片制造的过程,是大规模的,不是一颗颗制造的,所以首先一片wafer上有很多die,然后一次又有很多wafer。 一般情况下,一次制造过程都是同一种芯片,所有wafer上的所有die都是一种芯片,这样才能大规模,低成本的量产。当然一片wafer上可以是不同功能的die,想象一下,不同的die就要有不同电路和不同的处理程序。 一片wafer上的所有die同时进行测试,满足要求的会被切割下来进行封装,不满足要求的就是废片。wafer通常的尺寸有6英寸、8英寸、12英寸规格不等。 生产的过程是先将wafer划成一小格一小格的die,然后在所有小格子上同时完成 氧化 - 光刻 -刻蚀 - 薄膜沉积- 互连 - 测试 - 封装。再进一步描述一般基本步骤是: 先将晶圆适当清洗,再在其表面进行氧化及化学气相沉积,再进行涂膜、曝光、显影、蚀刻、离子植入、金属溅镀等反复步骤,最终在晶圆上完成数层电路及元件加工与制作。 对于单层电路层的芯片,这些元器件都是平铺在wafer上的-----称之为2D芯片。【2D芯片和版图layout是多层不是同一个概念,即使是2D芯片加工过程也是按照layout分多层加工的,单层电路也是立体的,可以形象的理解单层电路是1层的平房,3D的堆叠是多层楼房】 3D芯片有两类,一类是将多个die通过bonding或TSV封装在一起,形成多die的堆叠;另一类是像flash mem制造商那样在一个die上完成多层电路的加工与制作。下文会简单介绍芯片中“层”的概念。分别叫做: 堆叠封装 堆叠制造 wafer、die、cell是什么,它们的关系和区别?-电子工程专辑 多层堆叠电路层与层之间有绝缘膜,SiO2层。这种保护晶圆表面的氧化工艺也是一项专门的计数,这里不做详细讨论。可参考: 半导体晶圆氧化工艺介绍 - 艾邦半导体网 2.芯片制造过程 这里不展开来讲,请参考下面文章 芯片制造过程_富芯微电子有限公司,防护器件,可控硅,二极管,三极管,MOSFET 探秘半导体制造全流程:从晶圆加工到封装测试_cy413026的博客-CSDN博客 需要简单说明几个术语: fabless:没有芯片制造的IC设计公司 fab:Semiconductor fabrication plant 半导体制造厂 有时我们用fab只是表明 fabrication【制造】这一过程,而不是代表制造厂,说制造厂时更多用的的foundry。 比如说我们对来自Foundry的fab芯片进行测试和封装,就是对来自foundry制造的裸片【电路加工过程】进行封装测试 foundry:“代工厂”,它是一种只负责芯片制造、封装或测试的其中一个环节,不负责芯片设计环节的一种产业运作模式 IDM:Integrated Device Manufacture集成设备制造 它是一种集芯片设计、制造、封装、测试和销售等多产业链环节于一体的一条龙产业运作模式。典型企业有三星,intel,TI等 fab和Packaging and testing 这两个过程经常是由不同的厂家完成的,但是也有很多fab和封测一体的公司。fab比较著名的公司有TSMC,三星,SIMC。封测的第一位是日月光。但实际上先进的fab公司基本都掌握或者推动先进封装工艺。比如TSMC就是集先进fab和Packaging与一体,它有自己最先进的coWos封装技术,CoWos-S5. CoWoS: (Chip-on-Wafer-on-Substrate). 3.芯片制造中的层 闪存,正式进入232层时代! - 知乎 你真的懂3D NAND闪存? | 半导体行业观察 - 知乎 科普:芯片中的“层”,“层层”全解析_cy413026的博客-CSDN博客 简单的来说层有三个概念: 一个平面电路层-2D是由一层层光刻才完成的 一个多层堆叠封装-伪3D:是将多个单层电路的die堆叠封装在一起 多层单层电路堆叠制造-3D:直接在一个die上完成多层电路的制造,目前常用在flash mem的fab。 flash mem之所以可以达到最新的300+层,也和mem本身层与层之间连接比较规则和简单,适合做很多层堆叠。 当然其他芯片比如cpu/gpu也可以堆叠制造,但肯定上不了这么夸张的300+层,TSMC的CoWOS就可以堆叠cpu/gpu。 4.先进封装技术2D-->2.5D-->3D封装 浅谈先进封装技术_cy413026的博客-CSDN博客 简单的封装知识 RDL,TSV, Bump,Wafer_rdl封装技术-CSDN博客 当芯片大小超过2500mm2,单die/2.5D封装/CoWos最大尺寸-cy413026-CSDN 4.1wire BondingWire bonding【引线键合法】 封装,是传统的封装技术。下图是wire bonding的芯片实物图。

wire bonding可以用来进行多die堆叠,如上左图,对比右图,bonding模式,连线长而且多,没有TSV的成本低。TSV的功耗和电气特性都要比bonding好。 4.2 BumpBump是先进封装的基础 一文详解晶圆BUMP加工工艺和原理---cy413026-CSDN 【半导光电】什么是凸块制造(Bumping)技术_cy413026的博客-CSDN博客

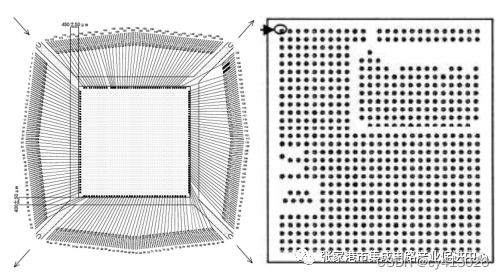

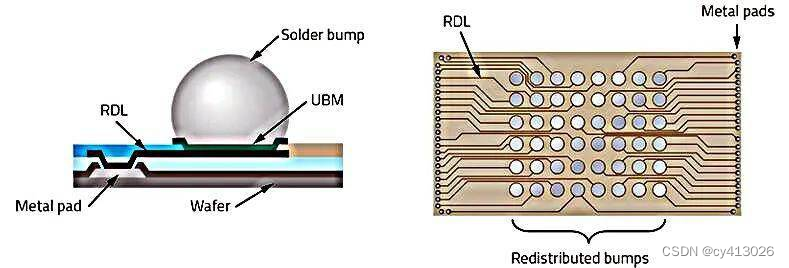

上图左边是传统的Wire bonding【引线键合法】 封装,引出端为四周引出方式; 右边是倒装焊封装:它的引出端为bump的内部二维矩阵排布 下图为Bump的芯片实例

可参考FlipChip给出的参考文章 4.2.1 Bump pitchbump pitch:凸点间距,一般是用以形容芯片的数据I/O的,芯片需要更多的数据通讯“点”才能实现更高的传输效率。那么这些“点”之间的间距、密集程度,自然成为衡量数据通讯效率的关键。而先进封装就某个层面来看,也是bump pitch在缩小的过程。 所以先进封装的先进程度可以一定程度上用bump pitch来衡量。 近年来,随着芯片集成度的提高,细节距(Fine Pitch)和极细节距(Ultra Fine Pitch)芯片的出现,促使凸块制造技术朝向高密度、微间距方向不断发展。 4.2.2 UBMUBM:Under Bump Metallization 沉积凸点下金属层。主要作用有: a.作为互联的键合层;b. 阻挡ball材料原子扩散至下层金属材料;c. 粘接下层介电材料和金属层,并阻挡污染物沿介电层水平方向迁移至下层金属。 4.3FlipChip芯片倒装焊封装的工作过程解析-cy413026-CSDN博客 4.4 2.5D封装:RDL&中介层(interposer)2.5D封装有两个重要的技术,分别是RDL和interposer 4.4.1 RDL下图是RDL(ReDistribution Layer)重布线层示意图,下图右边的含义是将电路层制造过程中分布在边界的pads通过引线接到了比较空旷的地方然后再bump。 再分布的过程,实际上是在原本的晶圆上又加了一层或几层。首先淀积的是一层电介质用于隔离,接着我们会使原本的触点裸露,再淀积新的金属层来实现重新布局布线。UBM在这里会被用到,作用是支撑焊锡球或者其他材料的接触球。

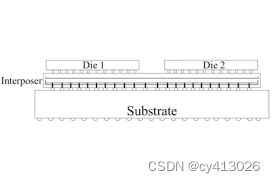

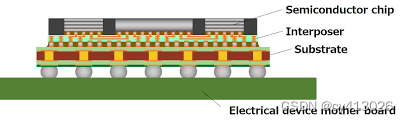

中介层(interposer):可以理解为在基板与Die之间的导电层【焊锡球和晶粒(Die)之间导电层】它的作用是扩大连接面,使一个连接改线到我们想要的地方。Bump和RDL会占用芯片接合到基板上的平面面积,有了中介层就可以扩大连接面。中阶层上可以平铺多个die。

上面这一段摘自转载文章: 浅谈先进封装技术_bumping ubm厚度-CSDN博客 另一篇转载文章对interposer介绍更清晰一点: 傻白入门芯片设计,Substrate/RDL/Interposer/EMIB/TSV(三)-CSDN博客 4.4 3D封装:TSV,PoP和MEMS浅谈先进封装技术_cy413026的博客-CSDN博客 |

【本文地址】

今日新闻 |

推荐新闻 |