[009] [ARM |

您所在的位置:网站首页 › 有符号数和无符号数的范围怎么求 › [009] [ARM |

[009] [ARM

|

ARM

Contents

基本概念

进位与借位

溢出

ARM汇编测试·

总结

1 基本概念

1.1 进位与借位

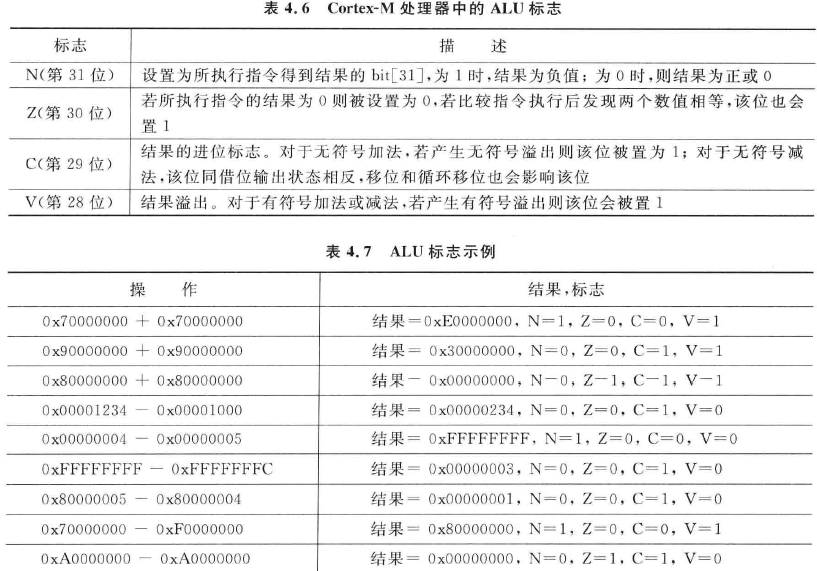

进位与借位是无符号数而言的。 进位:无符号数相加时,最高有效位向更高位进位,表示无符号数运算发生上溢出。借位:无符号数相减时,最高有效位向更高位借值,表示无符号数运算发生下溢出。ARM状态寄存器CPSR的C位表示进位或非借位标志(Carry/borrow flag) 加法指令中(包括比较指令CMN,根据两数相加结果进行比较),当结果产生了进位,则C = 1 ,其他情况C = 0;(进位标志,发生进位时C=1)在减法指令中(包括比较指令CMP,根据两数相减结果进行比较),当结果发生错位,则C = 0 ,其他情况C = 1;(非借位标志,发生借位时C=0)对于包含移位操作的非加/减法运算指令,C为最后一次被溢出的位的数值。对于8位无符号数(0~255): 58+124=182,范围内,无进位170+124=294,范围外,有进位 1.2 溢出溢出是有符号数而言的,即运算结果超出最大范围。只有当两个相同符号数相加,而运算结果的符号与原数据符号相反时(MSB为符号位),产生溢出。(两个正数相加或正数减负数、两个负数相加或负数减正数;对于一正一负相加则不可能出现溢出) CPSR的V位表示溢出标志(oVerflow flag): 在加/减法运算指令中,当操作数与运算结果为二进制的补码表示的带符号数时,V = 1表示符号位溢出。如:两个正数执行ADDS指令后,和运算结果的MSB为1(视为负数),则发生溢出。 对于8位有符号数(-128~127): -86+124=28 ,范围内,无溢出58+124=182 ,范围外,有溢出注意:C和V标志位的利用由程序员来决定,即若认为操作数为无符号数,则关心C标志;若认为操作数为有符号数,则关心V标志。 2 ARM汇编测试

加法指令: 整数状态标志位cmn r0, r1 adds r2, r0, r1 ldr r0, =0x80000000 ldr r1, =0x70000000 adds r2, r0, r1 ;最大值为0xffffffff未发生进位, c = 0, 但MSB为1, 则n = 1表负数 ldr r0, =0x80000000 ldr r1, =0x80000000 adds r2, r0, r1 ; 结果为[0]表示进位 c = 1 ldr r0, =-3 ;补码0xfffffffd ldr r1, =-2 ;补码0xfffffffe adds r2, r0, r1 ;负数补码相加, 结果为0xfffffffb,显然发生了进位, C = 1减法指令: 整数状态标志位cmp r0, r1 subs r2, r0, r1 ldr r0, =123 ldr r1, =100 subs r2, r1 ,r0 ;结果为-0x17,其补码为0xffffffe9, 发生借位 C=0 subs r2, r0 ,r1 ;结果为0x17, 未发生借位 C=1 将操作数视为有符号数,测试V标志 ; 正数 + 正数 (MSB = 0) ldr r0, =0x70000000 ldr r1, =0x70000000 adds r2, r1 ,r0 ; 高位MSB=1,溢出, v = 1 ; 正数 - 负数 (正数 + 正数 ) ldr r0, =0x80000000 ldr r1, =0x70000000 subs r2, r1 ,r0 ;溢出 v = 1 ; 负数 - 正数 (负数 + 负数) subs r2, r0 ,r1 ;溢出 v = 1 ; 负数 + 负数 (MSB = 1) ldr r0, =0x80000000 ldr r1, =0x80000000 adds r2, r0 ,r1 ; 结果为0, 即MSB=0, 溢出 v = 1 3 总结 无符号数在相加时才会发生进位,相减发生借位;有符号数只有在两正数或负数相加时(减正数可视作加负数,减负数视作加正数)才会发生溢出,其他情况不会溢出;由于汇编不能真正区别有符号与无符号数,一般由程序员主观决定,对于无符号数关心C位,有符号数则关心V位。数字在计算机中是以其补码进行存储的,正数的补码为其本身,负数的补码为原码按位取反+1。END |

【本文地址】

今日新闻 |

推荐新闻 |