【PCIE体系结构十四】电气物理层之发送端FFE |

您所在的位置:网站首页 › 智能计算机有什么功能 › 【PCIE体系结构十四】电气物理层之发送端FFE |

【PCIE体系结构十四】电气物理层之发送端FFE

|

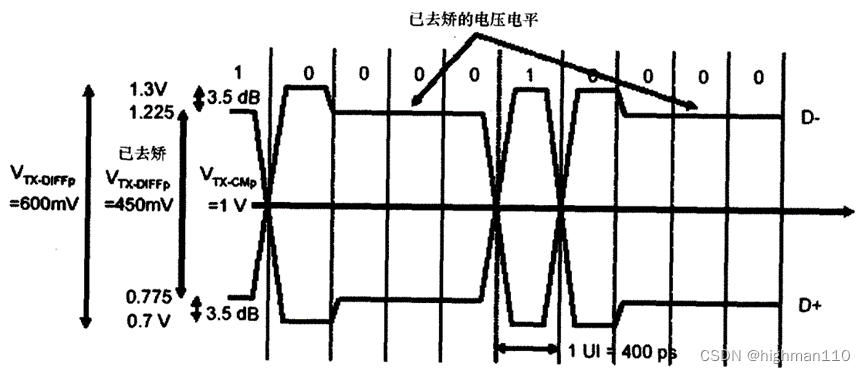

👉个人主页:highman110 👉作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容 参考书籍:《PCI.EXPRESS系统体系结构标准教材 Mindshare》 参考文章:https://www.eetop.cn/measurement/6948203.html 电气物理层前面章节讲的是物理层的逻辑层面,本章节开始将物理层的电气层面。电气层面主要包括时钟、电平、眼图、阻抗、损耗、功耗、均衡等电气特性或技术,这里主要讲一下均衡技术,其他内容大家自行查阅规范。 发送端均衡发送端均衡采用前向反馈均衡器(Feed forward Equalizer,FFE),分为预加重和去加重。这两个加重的概念大家应该不陌生了,这里不赘述,当前serdes发送端一般都采用去加重而不是预加重,我认为有以下几个考量: 1、预加重是有意增强信号跳变沿的信号幅度,增高高频分量,去加重是降低跳变沿之外的信号幅度,削弱低频分量,很显然预加重的功耗会大一点。 2、在经过连续相同电平的码元传输后,电容被持续充电,当下一个码元要翻转到相反电平时,这个翻转就可能无法达到目标电平,造成接收端错误。当然这种连续相同电平码元传输的情况已经通过编码、加扰等手段大概率避免了。 3、预加重增高高频分量,其对外辐射的能量更大,更容易引起串扰。 4、将信号放大的成本高于将信号减小的成本。 PCIE2.0及1.0的去加重规则是,信号发生跳变后,第一比特不做去加重,若当前比特与前一比特相同,进行去加重,如下图所示:

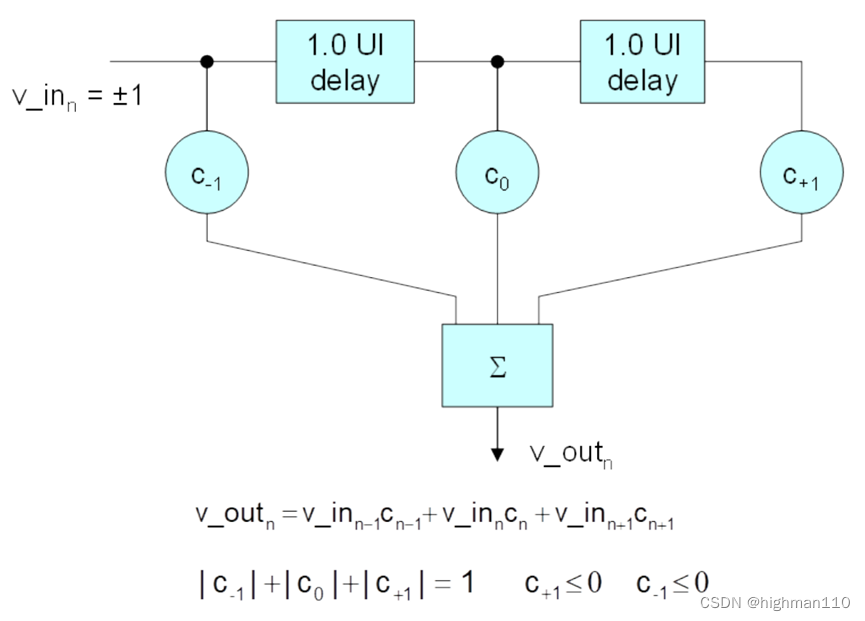

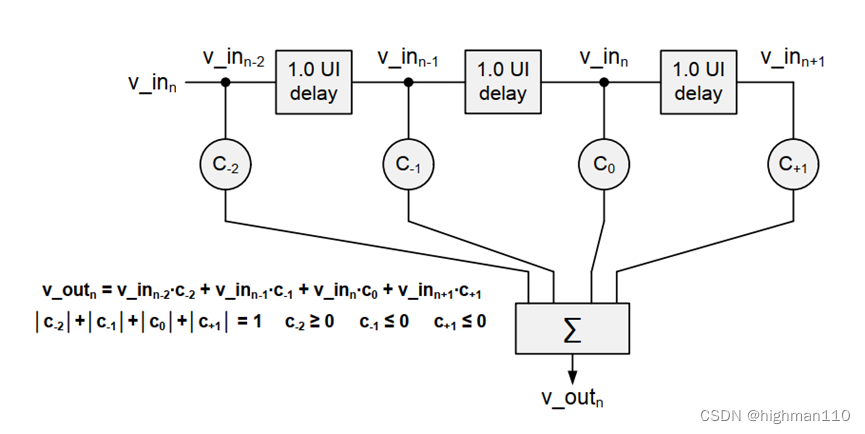

PCIE 1.0是-3.5dB去加重,PCIE 2.0有-3.5dB和-6dB两种可选,为什么2.0多了一个去加重更多的-6dB的选择呢,很好理解,输出速率提升了嘛,高频衰减更严重了,所以要把高频分量的比例提的更高点。在到PCIE 3.0之后,速率更高了,需要采用更加复杂的去加重技术,一般理解为,即除了跳变bit增⼤(这个增大指的是相对后面的相同电平比特而言)幅度发送(De-emphasis)以外,在跳变bit的前1个bit也要增大幅度发送,这个增⼤大的幅度通常叫做Preshoot,很好理解,增加preshoot的目的是为了进一步增加信号跳变时的高频分量。 PCIE 3.0到5.0的发送端预加重,使用的是一个三抽头FIR滤波器,6.0的用的是四抽头的,这里我们把原理图都贴出来,只分析三抽头的,四抽头大家自行查阅5.0规范,在8.3.3.2章节。

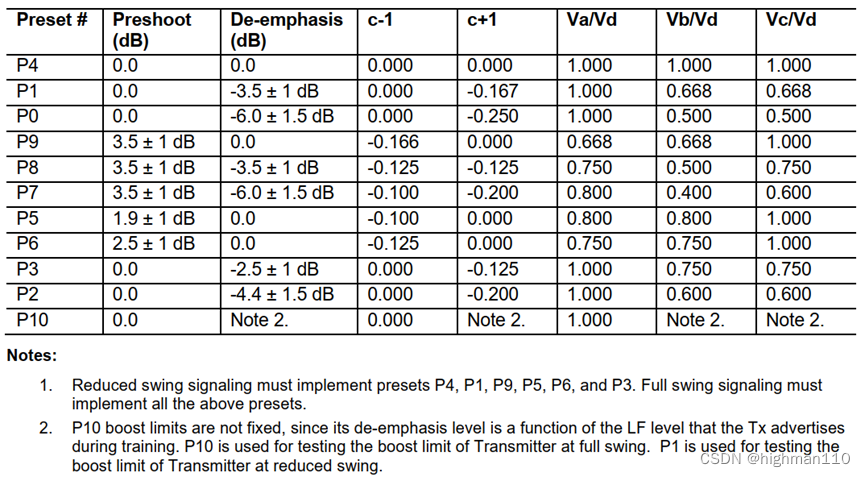

三抽头FIR均衡器如上图所示,该均衡器有三个输入,分别为当前发送比特、前一比特及后一比特,这三比特信号按照一定权重相加后作为输出,输出表达式如上图中下部。 其中,下一比特、当前比特及前一比特的权重系数 C-1、C0、C+1分别称为FIR方程的Pre-cursor、Cusor及Post-cursor系数。Pre-cursor又称Pre-shoot系数,Post-cursor又称去加重系数。收发端在均衡过程中调整这三个系数的值,来获得最佳传输性能。Pre-cursor、Cusor及Post-cursor 系数满足的规则在上图中下部也写了,一般只要设定Pre-cursor和Post-cursor系数,Cusor系数可以根据约束规则算出来。 为实现粗粒度的发送均衡参数调节,PCIe3.0规范定义了11组FIR均衡器Preset 值,编号为P0~P11。在收发端均衡之初交换Preset编号即交换了一组FIR均衡器的系数。各组 Preset的编码、Pre-shoot、De-emphasis、Pre/Post-cursor及各种电平比率如下表所示:

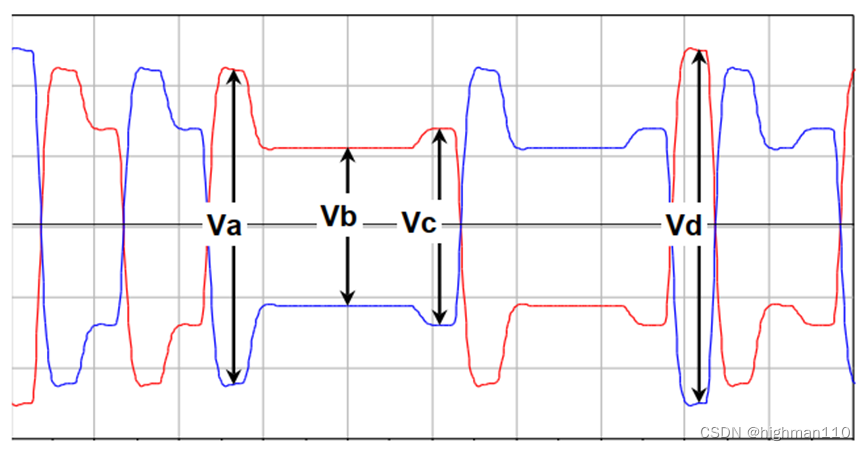

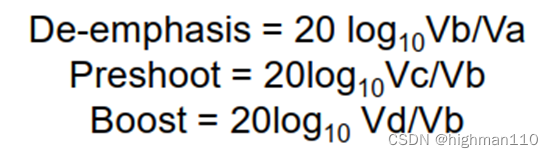

上面的注释中full swing mode一般指的是正常工作模式链路信号摆幅,reduced swing mode指的是低功耗模式的信号摆幅。 上表中的P0、P1两种Preset就是PCIE 1.0和2.0用的de-emphasis值,可以看到表中的preshoot为0,C-1系数为0。另外,P4这种C-1、C+1系数均为0,C0为1的preset,可以理解为FIR均衡器数据前后没有变化(这种Preset一般用来间接测量各种Preset下Va和Vc的电平)。简单理解就是,通过设置C-1、C+1为0可以关闭De-emphasis和Pre-shoot;若不考虑前一比特的影响,则设置C+1为0,则关闭了去加重;若不考虑后一比特的影响,则设置C-1为0,就关闭了Pre-shoot(有些文章翻译为前冲)。 那de-emphasis、Pre-shoot和boost的幅度怎么量化衡量的呢?毫无疑问就是通过不同的电平比值来衡量。我们看到上表中有Va、Vb、Vc、Vd四种电压,这是由于某个bit的前后bit的不同0、1场景,对应了4中不同的预加重电平调整结果,结合下图说明:

举个Preset=P7的例子:当前比特为1,C+1=-0.2,C0=0.7,C-1=-0.1: 连续3比特为011,输出电压为-C+1+C0+C-1=0.8,对应图中Va,称为Normal电平。 连续3比特为111,输出电压为C+1+C0+C-1=0.4,对应图中Vb,称为De-emphasized电平。 连续3比特为110,输出电压为C+1+C0-C-1=0.6,对应图中Vc,称为Pre-shoot电平。 连续3比特为010,输出电压为-C+1+C0-C-1=1.0,对应图中Vd,称为Maximum-height电平,可以简单理解为不经过FIR均衡器发送端的正常摆幅。 有了以上四种电平,就可计算出去加重、Pre-shoot及Boost幅度,表示为:

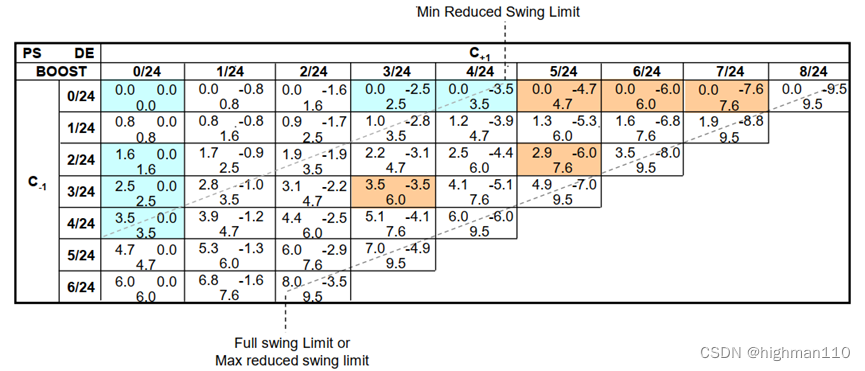

若不加限制,那么C-1、C0、C+1形成的组合非常之多。但并不是所有的组合在实际应用中都是合适的。其中一个最重要的约束条件就是:去加重电压Vb不能过小,过小的去加重电压会导致输出信号在接收端的眼高过低。因此通过BOOST比值对去加重地电压幅值进行限制:对于full swing mode的Tx输出,规范要求BOOST≤9.5dB;对于reduced swing mode的Tx输出,规范要求BOOST≤3.5dB。系数的具体要求如下: 1、系数必须支持上面的preset表中定义的所有11个预设值及其各自的公差; 2、所有Tx必须满足Full-swing信号VTX-EIEOS-FS限制,VTX-EIEOS-FS:Minimum voltage swing during EIEOS for full swing signaling。定义见PCIE 4.0规范文档8.3.6 Data Rate Dependent Parameters章节。 3、Tx可以选择性地支持Reduced-swing,支持Reduced-swing的话,必须满足 VTX-EIEOS-RS限制。VTX-EIEOS-FS:Minimum voltage swing during EIEOS for Reduces swing signaling。 4、系数必须满足Boost和分辨率(VTX-Boost-FS:Maximum nominal Tx boost ratio for full swing、VTX-Boost-RS:Maximum nominal Tx boost ratio for reduced swing、EQTXCOEFF-RES:Tx coefficient resolution)限制。 当以上约束均满足时,FIR系数空间可以映射到一个三角矩阵上。一个粒度为 1/24 的FIR系数三角矩阵如下图所示:

该矩阵中,去加重系数C+1映射到X轴,Pre-shoot系数C-1映射到Y轴。矩阵中每个单元格由3个元素组成:Preset(左上)、De-emphasis(右上)及 Boost(下中),每个单元格都代表了一种有效的Pre-shoot、去加重、Boost系数组合。对角线元素(8/24-8/24)为最大Boost比率(9.5 dB),这条线右侧的系数,Boost超过了9.5dB,这些参数不能使用,为空白单元格。Full-swing需实现所有蓝色及橙色单元格,Reduced-swing必须实现蓝色单元格。 发送端FFE就先介绍到这里,下一章讲述接收端DFE,敬请期待。

|

【本文地址】

今日新闻 |

推荐新闻 |