晶振差分时钟 |

您所在的位置:网站首页 › 晶振时钟信号波形图 › 晶振差分时钟 |

晶振差分时钟

|

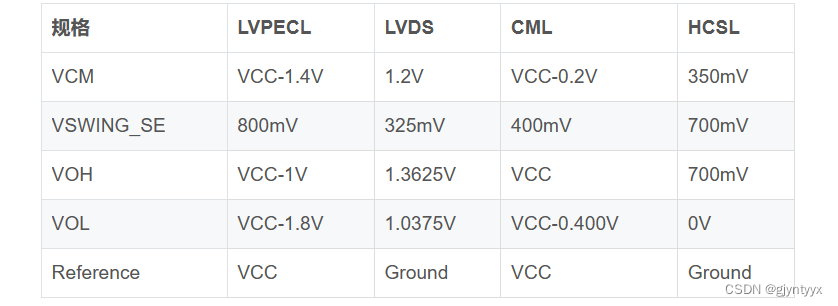

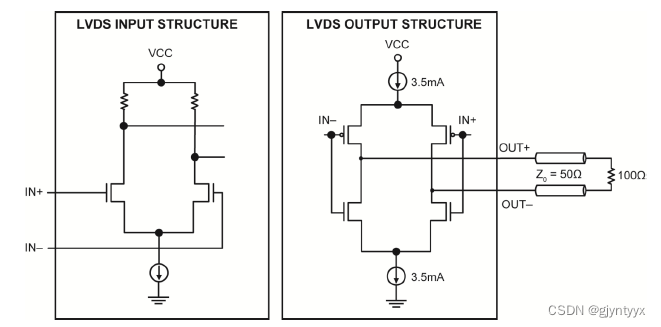

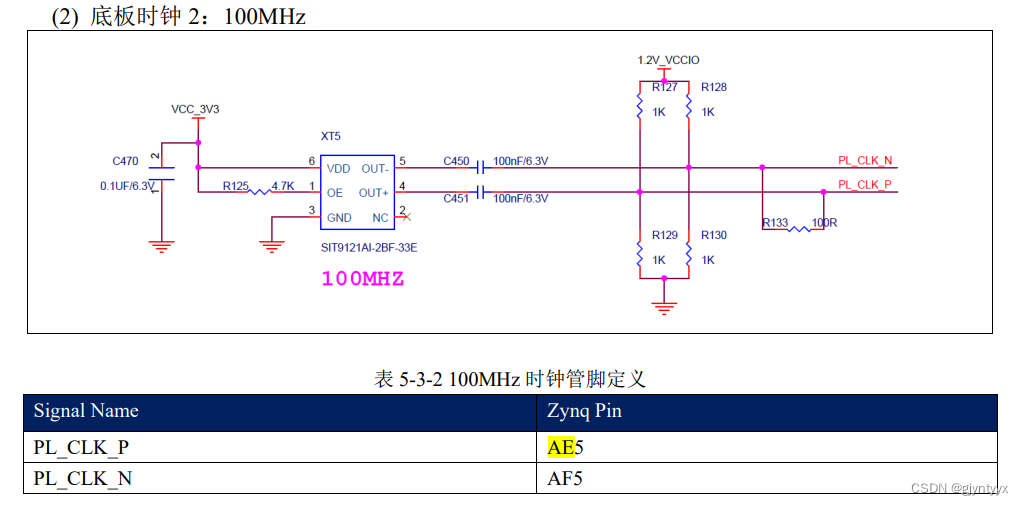

差分信号

差分信号的定义

所谓差分信号,即使用两个物理量之间的数值差异来表示一个信号。从严格意义上来讲,所有电压信号都是差分的,因为一个电压只能是相对于另一个电压而言的。 如果在一个电路系统中,将系统的"地"作为系统电压的基准点。若使用某一条传输线相较系统电压基准点的电压差表示待传输的信号,我们称这个信号为单端信号。若我们使用某一对传输线之间的电压差用于表示待传输信号,则我们称该型号为差分信号。 差分信号的优点差分信号的第一个好处是,因为你在控制‘基准’电压,所以能够很容易地识别小信号。在一个地做基准,单端信号方案的系统里,测量信号的精确值依赖系统内‘地’的一致性。信号源和信号接收器距离越远,他们局部地的电压值之间有差异的可能性就越大。从差分信号恢复的信号值在很大程度上与‘地’的精确值无关,而在某一范围内。 差分信号的第二个主要好处是,它对外部电磁干扰(EMI)是高度免疫的。一个干扰源几乎相同程度地影响差分信号对的每一端。既然电压差异决定信号值,这样将忽视在两个导体上出现的任何同样干扰。除了对干扰不大灵敏外,差分信号比单端信号生成的 EMI 还要少。 差分信号提供的第三个好处是,在一个单电源系统,能够从容精确地处理‘双极’信号。为了处理单端,单电源系统的双极信号,我们必须在地和电源干线之间某任意电压处(通常是中点)建立一个虚地。用高于虚地的电压来表示正极信号,低于虚地的电压来表示负极信号。接下来,必须把虚地正确地分布到整个系统里。而对于差分信号,不需要这样一个虚地,这就使我们处理和传播双极信号有一个高逼真度,而无须依赖虚地的稳定性。 差分晶振 差分晶振的定义所谓差分晶振,顾名思义,就是输出是差分信号的晶振。差分晶振是指输出差分信号的晶振,通过使用2种相位彼此完全相反的信号,从而消除了共模噪声,从而实现一个更高性能的系统。 差分晶振的选择选择差分晶振,首先要确认好频率,然后是电压,时钟逻辑类型,封装体积,工作温度以及频率稳定度(精度ppm)。 目前常用的时钟逻辑类型有LVDS,LVPECL,HCSL,CML四种类型。 目前市场主流差分晶振都是6脚贴片封装,常见的尺寸有7050(7.0*5.0mm),5032(5.0*3.2mm) ,3225(3.2*2.5mm) 差分晶振信号模式时钟逻辑类型有LVDS,LVPECL,HCSL,CML四种类型,每种逻辑类型具有不同的共模电压和摆幅电平。

|

【本文地址】

今日新闻 |

推荐新闻 |