【FPGA开发/IC开发之时序约束最全面的归纳总结】时序路径基本概念及时序约束分析方法 |

您所在的位置:网站首页 › 时钟的数字叫做什么 › 【FPGA开发/IC开发之时序约束最全面的归纳总结】时序路径基本概念及时序约束分析方法 |

【FPGA开发/IC开发之时序约束最全面的归纳总结】时序路径基本概念及时序约束分析方法

|

目录 一、为什么要进行时序约束 1.概述 2.相关术语 二、时钟的几种属性 1.时钟偏移 2.时钟抖动 3.时钟的转换时间 4.时钟的延时 5.Design Compiler中的时钟约束 三、时序路径及时序分析 1.四类常见的时序路径 2.建立时间分析 3.保持时间分析 四、DC中的约束规则及命令使用 1.寄存器CP端口到寄存器的D端口 2.输入端口到寄存器的D端口 3.寄存器的CP端口到输出端口 4.输入端口到输出端口 五、多时钟同步的时序约束 1.对于输入端口 2.对于输出端口 六、时序例外 1.异步路径 2.逻辑上不存在的路径 七、多时钟周期的时序约束 1.关于建立时间 2.关于保持时间 3.多时钟路径和普通路径同时存在 一、为什么要进行时序约束 1.概述RTL代码描述了电路的时序逻辑和组合逻辑,但代码中并不包括电路的时间信息(路径延时)和电路面积(门数)。为了使电路在规定的工作频率和工作环境下正确的工作,我们需要对设计中的所有时序路径进行约束。其目的是为了满足寄存器的建立时间和保持时间。 2.相关术语建立时间:在时钟有效沿到达之前,数据必须保持稳定的最小时间,简称Tsu 保持时间:在时钟有效沿到达之后,数据必须保持稳定的最小时间,简称Th 时序路径:一个点到点的数据通路。每一条时序路径有一个起点(startpoint)和一个终点(endpoint)。 发送沿:源端寄存器用于发送数据的时钟有效边沿。 捕获沿:目的端寄存器用于捕获数据的时钟有效边沿。默认情况下,发送沿和捕获沿相差一个时钟周期,有效边沿一般为上升沿。 起点:输入端口/触发器或寄存器的时钟引脚。 终点:输出端口/时序器件除时钟引脚以外的所有输入引脚。 二、时钟的几种属性时钟的四种属性:偏移(skew),抖动(jitter),延时(latency),转换(transition)时间。 1.时钟偏移时钟分支信号在到达寄存器的时钟端口过程中,都存在线网等延时,由于延时,到达寄存器时钟端口的时钟信号存在相位差,也就是不能保证每一个沿都对齐,这种差异称为时钟偏移(clock skew),也叫时钟偏斜。时钟的偏移如下图所示。

相对理想时钟沿而言,实际时钟存在不随时间积累,时而超前、时而滞后的偏移称为时钟抖动,简称抖动。 时钟偏移和时钟抖动都影响着时钟网络分支的延迟差异(相位差异),在Design Compiler里面,我们用时钟的不确定性(uncertainty)来表示这两种情况的影响。 3.时钟的转换时间自然界没有突变的事物,时钟由低电平到高电平的跳变或者由高电平到低电平的跳变称为时间的转换时间,并不是理想的时钟跳变。默认的上升转换时间为从电压的20%上升至80%的时间,下降的转换时间为从电压的80%下降至20%的时间。 4.时钟的延时时钟从时钟源(比如说晶振)出发到达触发器时钟端口的延时,称为时钟的延时,包含时钟源延迟(source latency)和时钟网络的延迟(network latency),如下图所示。

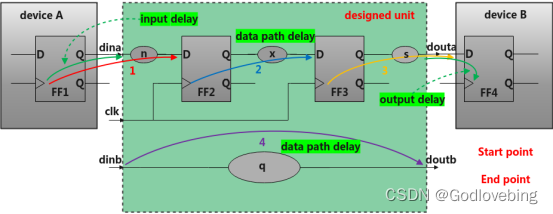

时钟源延迟(clock source latency),也称为插入延迟(insertion delay),是时钟信号从时钟原点到设计中时钟定义点(时钟的输入引脚)的传输时间,上图是3ns。 时钟网络延迟(clock network latency)是时钟信号从其定义的点(端口或引脚)到寄存器时钟引脚的传输时间,经过缓冲器和连线产生的延迟(latency),上图是1ns。 5.Design Compiler中的时钟约束时钟不确定建模:set_clock_uncertainty命令用于对时钟的偏移和抖动进行约束。假设时钟clk的周期为10ns,时钟的建立偏差为0.5ns。用下面的命令进行约束: create_clock -period 10 [get_ports clk] set_clock_uncertainty -setup 0.5 [ get_clocks clk] set_clock_uncertainty命令如果不加开关选项-setup或-hold,那么该命令给时钟赋予相同的建立和保持偏差值。此外,还可以对时钟的上升沿和下降沿进行偏差建模,比如上升沿的偏差是0.2ns,下降沿的偏差是0.5ns set_ clock_ uncertainty -rise 0.2 -fall 0.5 [get_clocks clk] 时钟转换时间建模:使用命令set_clock_transition进行约束设置。如果set_clock_transition命令中不加开关选项”-setup”或”-hold" ,那么该命令给时钟赋予相同的上升和下降转换时间。一般情况下,我们只约束最大的转换时间,如最大转换时间是0.2ns,那么就加上-max选项。 set_clock_transition -max 0.2 [get_clocks clk] 时钟延时建模:一般情况下,我们把时钟源延迟(source latency)和时钟网络的延迟(network latency)分开来,因为时钟源延时需要建模,是因为DC是真的不知道这个延时是多大,但是对于时钟网络的延迟,DC在布局布线前不知道,但是在布局布线后就可以计算出来时钟网络的延时了,因此在布局布线之后进行综合时,就没有必要对时钟网络进行约束,因此就要把这两个延时分开来进行约束。 布局布线之前:假设时钟周期为10ns,时钟源到芯片的时钟端口时间是3ns,时钟端口到内部触发器时钟引脚的时间是1ns。可以使用如下命令: create_clock -period 10 [get_ports clk] set_clock_latency -source -max 3 [get_clocks clk] //时钟源延时 set_clock_latency 1 [get_clocks clk] //时钟网路延时 布局布线之后:就可以计算实际的线网延时,就要使用set_propagated_clock [ get_clocks clk]这个命令代替上面的set_clock_latency 1 [get_clocks clk] 这个命令。 三、时序路径及时序分析 1.四类常见的时序路径如下图所示,中间绿色部分是我们数字电路设计逻辑模块所要综合的单元,device A为芯片的上游器件,device B为芯片的下游器件。四类最常见的时序路径依次作如下分析。

路径编号 起点/S 终点/E 描述 1 dina FF2/D 设计的输入端口到第一级寄存器数据端口 2 FF2/cp FF3/D 寄存器时钟端口到下一级寄存器数据端口 3 FF3/cp douta 末级寄存器时钟端口到设计的输出端口 4 dinb doutb 输入端口到输出端口的纯组合逻辑电路 前三类时序路径的共同点在于:起点为寄存器的时钟端口,终点为寄存器的数据端口;第四类为组合逻辑路径。我们以路径2作为分析入口:

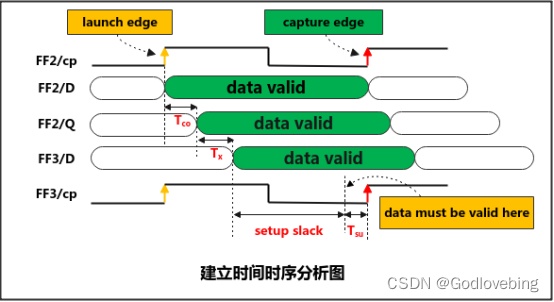

对于路径2,数据从FF2的D端口传输到FF3的D端口,主要经历的时间为:触发器的翻转时间(Tco),寄存器与寄存器之间的组合逻辑X延时Tx,到达寄存器FF3的数据端口D。 2.建立时间分析

为了满足FF3建立时间的要求,也就是数据经过上面的延时(触发器FF2的翻转时间/转换延时、寄存器与寄存器之间的组合逻辑延时)之后到达FF3的D端的时间再加上FF3的建立时间,需要小于时钟周期。以发送沿作为0时刻参考点: 数据到达时间:Tarrival=Tco+Tx。(数据到达寄存器FF3的D端口的实际时刻) 数据需求时间:Trequired=Tclk-Tsu-Tuncertainty。(为了满足建立时间需求,数据到达寄存器FF3的D端口最晚的时刻) 时间裕量:Tslack=Trequired-Tarrival 当Tslack>=0时,表示满足时序要求。 当Tslack=0 即:Tco+Tx+Tsu+Tuncertainty=0 即:Tco+Tx>=Th+Tuncertainty 结论:传输延时需要大于寄存器的保持时间和不确定之和。 注意:保持时间一般是能够满足的,也就是传输延时一般是大于触发器的保持时间的,即使满足不了,在后端版图设计的时候,也可以有修改措施(比如路径加缓冲器增加延时)。因此我们在约束的时候,我们一般不关注保持时间,而是注重建立时间。 四、DC中的约束规则及命令使用 1.寄存器CP端口到寄存器的D端口

图中路径N的最大时延应满足下列关系: TN |

【本文地址】

今日新闻 |

推荐新闻 |