高速串行接口简介 |

您所在的位置:网站首页 › 数据接口的作用有哪些 › 高速串行接口简介 |

高速串行接口简介

|

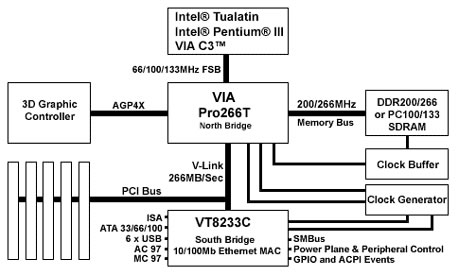

在计算机之间以及计算机内部各部分接口之间有两种数据传输方式:并行数据传输方式与串行数据传输方式。 并行数据传输方式通过多个通道在同一时间内传播多个数据流;而串行数据传输方式在同一时间内只传输一个数据流。 过去,前者,也即并行数据传输方式,是主流的数据接口,而后者常用于设备之间的远距离、低速率的数据通信以及设备内芯片之间的低速率通信。 比如,早期的计算机内的并行接口有:ISA,ATA,SCSI,PCI、SDRAM和前端总线(FSB,Front Side Bus)等等,而PC与外部设备的数据接口有LPT(Line Printer Terminal)并行端口。 威盛 VIA Pro266T 芯片组架构图 如今,PC主板上除了从SDRAM演进过来的DDR SDRAM接口之外,其它的并行接口已基本被团灭. 上边这张图是今年(也即2021年)3月16号,Intel新发布的第11代处理器的芯片组架构图。其中的数据互联总线,除DDR-DRAM外,其他接口均为串行接口。 其中,PCIe 4.0 的每Lane的传输速率达到了16GT/S,Thunderbolt 4 为 40Gbps,USB4 Gen 3×2为 40Gbps,eDP 1.4b HBR3 8.1 Gbit/s 每lane,共32.4 Gbit/s 带宽,HDMI 2.0b 带宽 18 Gbit/s。 PC外设的连接接口部分,也没有了并行总线的身影。 甚至苹果最新的MacBook产品线,随着Apple M1处理器将DRAM封装进芯片基板上,无论是PCB中的互联还是与外部设备的接口,已经没有并行接口了,直接团灭!🤞 如今,高速串行接口不仅应用于个人计算机、服务器和通信设备,还应用于数字消费电子、医疗设备、广播设备、半导体制造和测试设备以及其他许多电子设备和应用。 高速互联串行化已经成为行业共识,这种转变趋势几乎是不可逆的,所以,了解高速串行接口已经成为电子设计人员的基本要求。 因此,《PCB设计一板即成功专栏》高速串行接口章节,将重点介绍关于Gbps串行接口的PCB设计相关知识,并以一些大家熟悉的PC内部和外设互联接口标准为实例,对其包括仿真及测量方法进行介绍。 为什么要高速串行化?串行接口本身长期以来一直用于芯片间的控制和设备间的通信,如I2C、SPI、UART、RS-232等等,但这里的高速串行接口是指 “物理层数据速率超过Gbps “的接口,因为它需要传输大量的数据。 数据带宽需求急剧增加怎么会这么快? 单位时间内传输的数据量称为数据带宽。其原因是多媒体应用对数据带宽需求的持续增长。 老wu还记得玩的第一款纯3D游戏是古墓丽影,当时电脑里用的是3dfx的Voodoo显卡,显卡接口还是PCI的并行接口。 《古墓丽影》劳拉 3dfx的Voodoo显卡 而现在的《古墓丽影:暗影》,都可以开启光线追踪了,3dfx 也已被nVidia收购,显卡也来到了RTX 3090,显卡接口也来到了 PCI Express 4.0 标准。 从历史上看,传输和存储的数据已经从文本为主的格式转向了Hi-Res无损音频/音乐格式、从静态图像转向了4K/8K高清视频。更高清晰度的视频意味着更高的分辨率、更高的色彩深度和更高的帧率,也即需要更高的带宽。 像现在的3A大作,画面制作非常精良,为了有更好的游戏画面体验,分辨率一般要4K,刷新达到了了120Hz,电竞的显示器甚至达到了240Hz的水平. 如果想要以4K的分辨率、4:4:4 RGB (未压缩的色彩空间)、 HDR 10 (10bit 色深)、120Hz刷新率,需要的带宽为 40.1 Gbps,显然,DisplayPort 1.4以及HDMI 2.0的带宽都不够用了,这需要HDMI 2.1(48Gbps)或者DisplayPort 2.0 (80Gbps)。 而在数据中心方面,作为互联网业务赖以生存和发展的基础设施,早已从最初的千兆、万兆网络,走到了“25G接入+100G互联”规模部署的阶段。而随着VR/AR、16K视频、自动驾驶、人工智能、5G、物联网等层出不穷的数字化应用,带宽需求的持续提升也是必然。 而400 Gb以太网(400 GbE)是新一代的有线通信标准,IEEE以太网标准组802.3已确定在400GE接口中的物理层采用50Gbps/lane PAM4编码技术,8 lane组成400 Gbps。 并行接口的缺点在并行传输方式中,要增加数据带宽,可以增加总线宽度或提高数据传输速率。 例如,SCSI接口,它是通过增加总线宽度和传输速率来提升的。 但随着传输速率的提高,各信号之间的偏斜 (skew) 也就更加明显,时钟和strobe 信号与数据之间的建立时间和保持时间难以保证,此外,随着速度的提高,抖动的影响也越来越明显,后来,SCSI 就串行化啦,演化为SAS(Serial Attached SCSI,串列SCSI)接口。 规格 别名 规范文件 接口 数据包 (bits) 频率 带宽 (Mbit/s) SCSI-1 Narrow SCSI SCSI-1 (1986) IDC50; Centronics C50 8 5 MHz 40 Mbit/s Fast SCSI SCSI-2 (1994) IDC50; Centronics C50 8 10 MHz 80 Mbit/s Fast-Wide SCSI SCSI-2; 2 x 50-pin (SCSI-2); 16 10 MHz 160 Mbit/s SCSI-3 SPI (1996) 1 x 68-pin (SCSI-3) Ultra SCSI Fast-20 SCSI-3 SPI IDC50 8 20 MHz 160 Mbit/s Ultra Wide SCSI SCSI-3 SPI 68-pin 16 20 MHz 320 Mbit/s Ultra2 SCSI Fast-40 SCSI-3 SPI-2 (1997) 50-pin 8 40 MHz 320 Mbit/s Ultra2 Wide SCSI SCSI-3 SPI-2 68-pin; 80-pin (SCA/SCA-2) 16 40 MHz 640 Mbit/s Ultra3 SCSI Ultra-160; Fast-80 wide SCSI-3 SPI-3 (1999) 68-pin; 80-pin (SCA/SCA-2) 16 40 MHz DDR 1280 Mbit/s Ultra-320 SCSI Ultra-4 SCSI or Fast-160 SCSI SCSI-3(2002) 68-pin; 80-pin (SCA/SCA-2) 16 80 MHz DDR 2560 Mbit/s Ultra-640 SCSI Ultra-5; SCSI-3(2003) 68-pin; 80-pin 16 160 MHz DDR 5120 Mbit/s提高信号的速度意味着提高逻辑电平变化的速度,也就增加了多路信号间的串扰和地弹(Ground Bounce)等问题。 此外,总线位宽的增加,同时也增加了引脚数量,从而导致封装和芯片尺寸的增大,增加了印刷电路板上的布线难度和所需要的布线层数,同时带来了功耗过大的问题。 串行接口的优势相对于并行数据传输需要IC之间的多个连接通道而言,串行数据传输只需要两对连接即可实现全双工高速传输。 串行数据传输由于其优点(例如低功耗,强大的EMI性能以及易于封装的设计)而成为高速数字传输的理想选择。 自由选择传播媒介不仅可以选择铜线,还可以选择光纤作为介质。 设计自由度高可以用细电缆代替扁平电缆。 设备与设备间的连接电缆较少。 易于连接减少了信号线的数量,也即减少连接器的尺寸。 容于PCB布线上边说了,相对于并行总线而言,串行嵌入了时钟,采用一对走线即可实现数据的传输,而为了实现更高的带宽,也会采用多通道的连接方式,但通过在每个通道中设置CDR(时钟数据恢复)或均衡器,可以放松通道之间的偏斜要求,通道之间不再需要严格的等长布线。 减少引脚数芯片尺寸减小,使得在相同的封装尺寸内实现更高的集成度和功能,以及集成多种接口成为可能。 串行接口特有的功能 发送端均衡器( Tx Equalizer)SERDES 信号从发送芯片到达接收芯片所经过的路径称为信道(channel),包括芯片封装,pcb 走线,过孔,电缆,连接器等元件。从频域看,信道可以简化为一个低通滤波器(LPF)模型,如果SERDES 的速率大于信道(channel)的截止频率,就会一定程度上损伤信号。均衡器的作用就是补偿信道对信号的损伤。发送端的均衡器采用 FFE(Feed forward equalizers)结构,发送端的均衡器也称作加重器(Emphasis)。加重(Emphasis)分为去加重(De-emphasis)和预加重(Pre-emphasis),De-emphasis降低差分信号的摆幅(swing),Pre-emphasis 增加差分信号的摆幅。 接收端均衡器(Decision Feedback Equalizer)如前所述,信道频率响应的表现就像一个低通滤波器,通过信道的高频信号受到衰减,而低频信号则不受影响。在时域上,这种损耗会分散信道所传输的符号,使接收端符号的脉冲宽度拖尾持续时间大于符号的周期,从而该符号与相邻的符号间产生相互干扰,这种现象被称为符号间干扰。 当数据传输通过信道时,符号间干扰会引起信道输出端眼图闭合,从而对时钟数据恢复电路的设计带来困难,导致误码率(BER)上升。 为解决这一问题,SERDES 接收均衡器采用判决反馈均衡器,判决反馈均衡器将恢复出的二进制数据与一定的系数相乘后立即反馈到信号输入端,并与当前数据相加减,通过反馈回来的二进制数据将当前接收到的数据中存在的符号间干扰消除。判决反馈均衡器采用已经恢复出来的数据值来消除当前判决中所存在的符号间干扰,从而不会放大噪声成分。 时钟恢复和时钟数据恢复通常,了让接收器正确地接收数据,需要一个strobe 和一个时钟来锁存(保持)数据。 但是,在高速串行接口上发送时钟并不能解决时钟和数据之间的偏斜问题。 此外,从EMI和串扰的角度来看,用高频率来发送时钟是不可取的。 为了解决这个问题,发送端按时钟时序串行化并传输数据,而接收端则利用PLL从数据流中提取时钟,即不单独进行时钟信号的传输。 在这种方法中,接收端产生一个与接收数据流的数据速率(频率)同相的时钟。 用恢复的时钟来锁存数据的电路也被称为 “时钟数据恢复电路”(CDR),SerDes电路的核心是时钟数据恢复(CDR)电路,即从输入数据流中分离出时钟和数据信号,消除传输过程中带来的抖动和失真,将数据解串后送入后续的电路,时钟数据恢复电路的性能决定了整个SerDes电路的性能。 高速串行接口的发展趋势 总体趋势以下是对当今串行接口的总体趋势的总结: 接口的速度持续提升 原本以串行为标准的接口,如USB、以太网等,速度都有了提升。设备内部接口的串行化,过去是并行传输方式的PCI(PC扩展接口)已经被PCI Express所取代,存储接口的ATA(并行ATA)已经被SATA(串行ATA)所取代。已经串行化的接口,则每一代都将以更高的速度为目标进行技术迭代。 例如,USB3.0(5 Gbps)→3.1(10 Gbps)→3.2(10 Gbps×2)→4(20 Gbps×2)。 由标准化组织进行标准化 生产商并不是自己制定标准,而是通过建立标准化组织进行标准化,并发布规范。 该规范包括测试方法。 典型的例子是USB和PCI Express。 USB-IF和PCI-SIG正在推动标准化工作。 展望 PCI Express® 6.0规范将计划在2021年发布,下一代PCIe技术将使数据速率再次翻倍,达到64 GT/s,将会利用PAM-4编码,利用业界现有的56G PAM-4标准。 VESA 计划于今年春季举办首次 PlugTest 活动,有望于 2021 年末看到首款搭载 DP2.0 接口的产品。 2020年发布的PS5已经XBox都搭载了HDMI 2.1接口,相信2021年会有更多搭载HDMI 2.1接口的8K/120Hz刷新率的高端电视出现。 |

【本文地址】

今日新闻 |

推荐新闻 |