数字逻辑期末考试必考知识点(从题目中分析) |

您所在的位置:网站首页 › 工业设计期末考试考什么 › 数字逻辑期末考试必考知识点(从题目中分析) |

数字逻辑期末考试必考知识点(从题目中分析)

|

1、一个触发器只有两种状态,构成组合逻辑电路,要看最大值是多少,几位二进制数能够满足要求

既然是模4,那么最大值为3,化成二进制是11,那么只需要两个触发器即可 2、奇偶校验位: 若为奇校验:原数据中1的个数为奇数时,校验位为0,反之为1; 若为偶校验:原数据中1的个数为奇数时,校验位为1,反之为0;

求偶检位,1有三个,所以检验位是1,完整的偶检验码:100111 3、对偶式:把一个式子里面的“和”变成“且”,“0”变成“1”,“1”变成“0”:

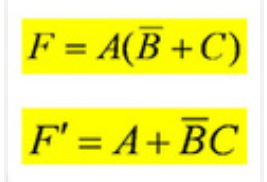

这个标准式子里面,之所以没有把A变成A的反,是因为A的具体状态不知道,,,,咱也不懂,就记住这个不确定是0还是1的变量不变 4、数字信号是不均匀的,模拟信号是均匀的 5、余三码是无权码,余三码是在8421BCD码的基础上加0011,利用余三码进行加法运算,有进位结果加3;无进位结果减三;且余三码的加法运算是需要修正的 6、无权BCD码不能直接进行算术运算 7、异或与同或的运算: 若运算单位为奇数个:异或运算等于同或运算取非 若运算单元为偶数个:异或运算等于同或运算 8、设计四位二进制数的奇校验码发生器需要4个两输入的异或门 设计四位二进制数的偶校验码发生器需要3个两输入的异或门 9、竞争现象:输入信号经过不同的路径到达输出端的时间有先有后 10、冒险:有竞争导致的错误输出信号 11、编码器与译码器: 我们只需要知道编码器是多变少,译码器是少变多,如二进制译码器编码器:n->2^n 12、2-4译码器可以扩展成3-8译码器 74138译码器就是带使能端的3-8译码器 使能端是什么,可以控制电路正常工作或者禁止工作 13、数据选择器:从多路数据输入中选择一条路到输入端,是输入端多 数据分配器:多路复用器,是输出端多 14、算术逻辑电路: 半加器(HA):本位和S=A异或B,进位C=A且B 全加器(HA):本位和=A异或B异或上一轮进位,进位=A异或B且上一轮进位+A且B;本位和是三个数异或运算,进位是两个数异或再且上一轮进位加两个数的且 15、7483通用加法器: 7483通用加法器是四位并行加法器:CI是上一轮进位,CO是传给下一个的进位 16、时序逻辑电路: 关注四个点:输出方程、驱动方程、状态方程、状态图 1、锁存器与触发器:锁存器直接由激励信号控制电路状态、触发器由激励信号和时钟一起控制 2、RS锁存器:

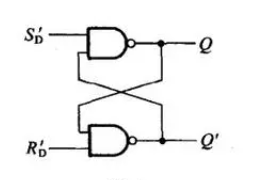

两个输入端(激励信号),S是置1端、置位端,R是置0端、复位端 刻到脑子里,Q为0为0状态、Q为1位1状态 只需要知道,R和S不能同时为1,都为0时Q不变,R=1时,Q变为0状态;S=1时,Q变为1状态 RS锁存器的约束条件:RS=0

特性方程等于R的非且上一个状态加S 3、门控RS锁存器: 就是加了一个C来控制锁存器的状态是否能够转换,只有C为1的时候才有效 4、门控D锁存器:用D来替代了RS,输入分别是D和D的非, 5、JK门控锁存器: RS分别对应KJ,S=K(Q的非),R=JQ Q=JQ\+K\Q 6、在门控D锁存器中,当C=1时,锁存器的状态会随着信号D变化而变化,若D变化剧烈,会发生空翻现象 7、触发器:激励信号与时钟一起控制电路 工作特点:由时钟脉冲确定状态转换的时刻,由输入信号决定状态转换的方向 8、边沿触发器:在时钟为稳定的0或1期间,输入信号无法进入触发器,触发器的状态不变 17、同步时序与异步时序逻辑电路: 按照逻辑功能分为:计数器、寄存器以及移位寄存器 分析步骤:1、输出方程与驱动方程 2、将驱动方程带入到特性方程,导出状态方程 3、画出状态图,说明逻辑功能 所谓输出方程就是最终得到的那个值的表达式,器件的输出算作Q,直接写, 驱动方程就是写出触发器的输入端的表达式 把表达式带入到特性方程里面去,画出状态图

这里最后那个Q2的次态方程写错了,应该是Q2的n次方取反。还有Q3的次态方程,应该再加一个括号。

画的比较一般,有些冗余, |

【本文地址】