数字IC经典电路(4) |

您所在的位置:网站首页 › 实现音频信号数字化的最核心的硬件电路是 › 数字IC经典电路(4) |

数字IC经典电路(4)

|

数字IC经典电路(4)—经典数字滤波器(滤波器简介及verilog实现)

写在前面的话数字滤波器分类

经典数字滤波器FIR滤波器FFT—FIR滤波器并行FIR滤波器串行FIR滤波器CIC滤波器卡尔曼滤波器

总结参考资料

写在前面的话

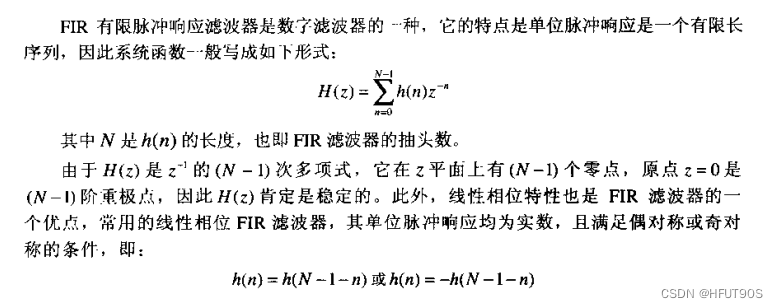

数字滤波器一般可以分为两类:有限冲激响应(FIR)滤波器和无限冲激响应(IIR)滤波器。 在Verilog综合方面,通常可以实现四种数字滤波器: 基于时域采样的FIR滤波器(Time Domain Sampling FIR Filter)快速傅里叶变换(FFT)算法实现的FIR滤波器(FFT-based FIR Filter)直接IIR滤波器(Direct Form IIR Filter)级联IIR滤波器(Cascade IIR Filter)其中,基于时域采样的FIR滤波器适用于低通、高通、带通、带阻等常见滤波器类型,但其抗混叠能力较差;FFT-based FIR滤波器适用于平滑频率特性要求高的滤波器,但需要额外硬件支持FFT运算;直接IIR滤波器和级联IIR滤波器适用于需要更少延迟和低硬件成本的滤波器设计,但容易出现稳定性问题。 数字滤波器分类数字滤波器是一种数字信号处理技术,用于对数字信号进行去噪、滤波和频谱分析等处理。根据其响应特性和算法实现方式,数字滤波器可以分为多种类型。 FIR滤波器FIR滤波器是一种有限冲激响应(Finite Impulse Response)滤波器,具有线性相位、无回声等特点,常用于需要精确控制滤波器通带和阻带幅度响应的应用中,如语音和音频处理、图像处理和通信系统中的调制解调等。 IIR滤波器IIR滤波器是一种无限冲激响应(Infinite Impulse Response)滤波器,可以通过递归方式获得稳定性,具有较低的阶数和更好的全通性能,适用于带限信号处理和模拟滤波器的数字实现。 频域滤波器频域滤波器是基于傅里叶变换等频域分析技术设计的滤波器,包括低通、高通、带通和带阻四种类型,可用于滤波器设计、频域分析和信号还原等方面。 自适应滤波器自适应滤波器是一种能够根据输入信号和环境的变化自行调整滤波系数的滤波器,主要用于去除噪声和复杂的干扰。 数字时域处理滤波器数字时域处理滤波器是利用离散时间信号的离散微分、差分或积分等进行信号滤波的滤波器,常见的有均值滤波器、中值滤波器和高斯滤波器等。 以上各种数字滤波器的选择取决于应用场景和设计要求,需要综合考虑其性能、稳定性、响应速度和资源消耗等因素。 经典数字滤波器 FIR滤波器

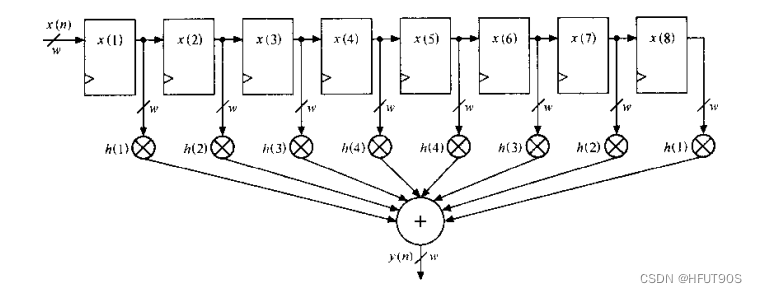

线性相位的FIR滤波器结构图 FIR滤波器具有稳定、线性和时不变的特性,能够精确控制频率响应。 FIR滤波器计算简单,容易实现。 理论上,FIR滤波器能够完全去除滤波器输入信号中的周期性干扰。 FIR滤波器具有简单的调整滤波器特性的方式,只需要简单地添加或减少滤波器的系数并重新编程即可。 在Verilog设计FIR滤波器时需要注意以下几点: 定义好滤波器的系数,FIR滤波器的效果和性能主要取决于这些系数。在计算系数时,请使用MATLAB或其他专业工具来保持准确性。 确定输入/输出数据的宽度,这通常需要根据具体应用来确定。您需要考虑您的信号源的噪声和分辨率,并设置数据宽度以确保不会有过多的噪声或失真。 确定时钟频率,这也需要根据该设计中的最大数据速率来确定。如果时钟周期不足以处理所有输入数据,则需要增加时钟频率或引入流水线来处理。 注意FIR滤波器延迟的问题。由于FIR滤波器中的系数乘法运算是串行的,会导致输出数据的延迟。您需要在设计中考虑这个因素,并相应地调整时序。 经过设计和仿真后,需要进行一些性能测试来确保您的FIR滤波器在实际使用中能够按预期工作。请特别注意过高的噪声和失真,这些问题通常可以通过调整系数、增加时钟频率等方式来解决。 Verilog代码 example1 module fir_filter #( parameter WIDTH = 16, // 数据位宽 COEFF_SIZE = 5, // 系数位宽 TAP_NUM = 10 // 块大小或阶数 ) ( input clk, input rst, input signed [WIDTH-1:0] din, output reg signed [WIDTH-1:0] dout ); reg signed [WIDTH-1:0] shift_reg [0:TAP_NUM-1]; reg signed [COEFF_SIZE-1:0] coeff [0:TAP_NUM-1]; integer i; integer j; reg signed [WIDTH+COEFF_SIZE-2:0] sum; initial begin for (i=0; i |

【本文地址】

今日新闻 |

推荐新闻 |

普通FIR滤波器实现方案

普通FIR滤波器实现方案

FIR特点及注意点 FIR滤波器(Finite Impulse Response Filter,有限脉冲响应滤波器)的特点:

FIR特点及注意点 FIR滤波器(Finite Impulse Response Filter,有限脉冲响应滤波器)的特点: