组合逻辑电路( Combinational Logic Circuit)知识点总结 |

您所在的位置:网站首页 › 基本的逻辑门电路有哪5种组成方式呢 › 组合逻辑电路( Combinational Logic Circuit)知识点总结 |

组合逻辑电路( Combinational Logic Circuit)知识点总结

|

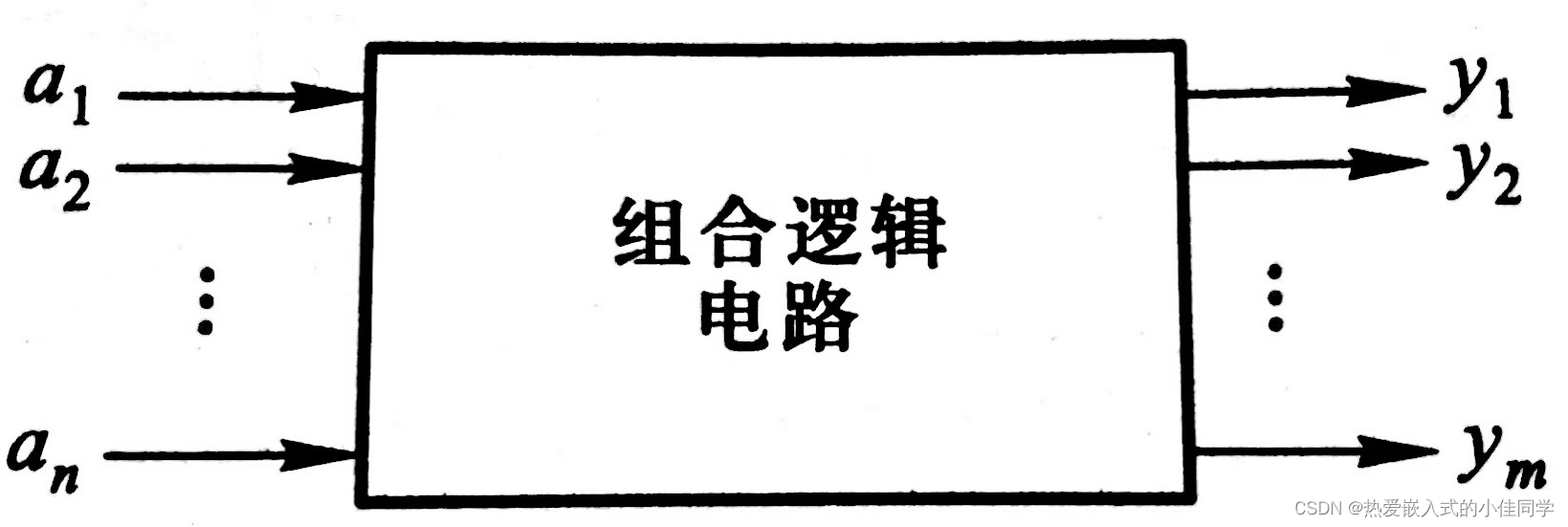

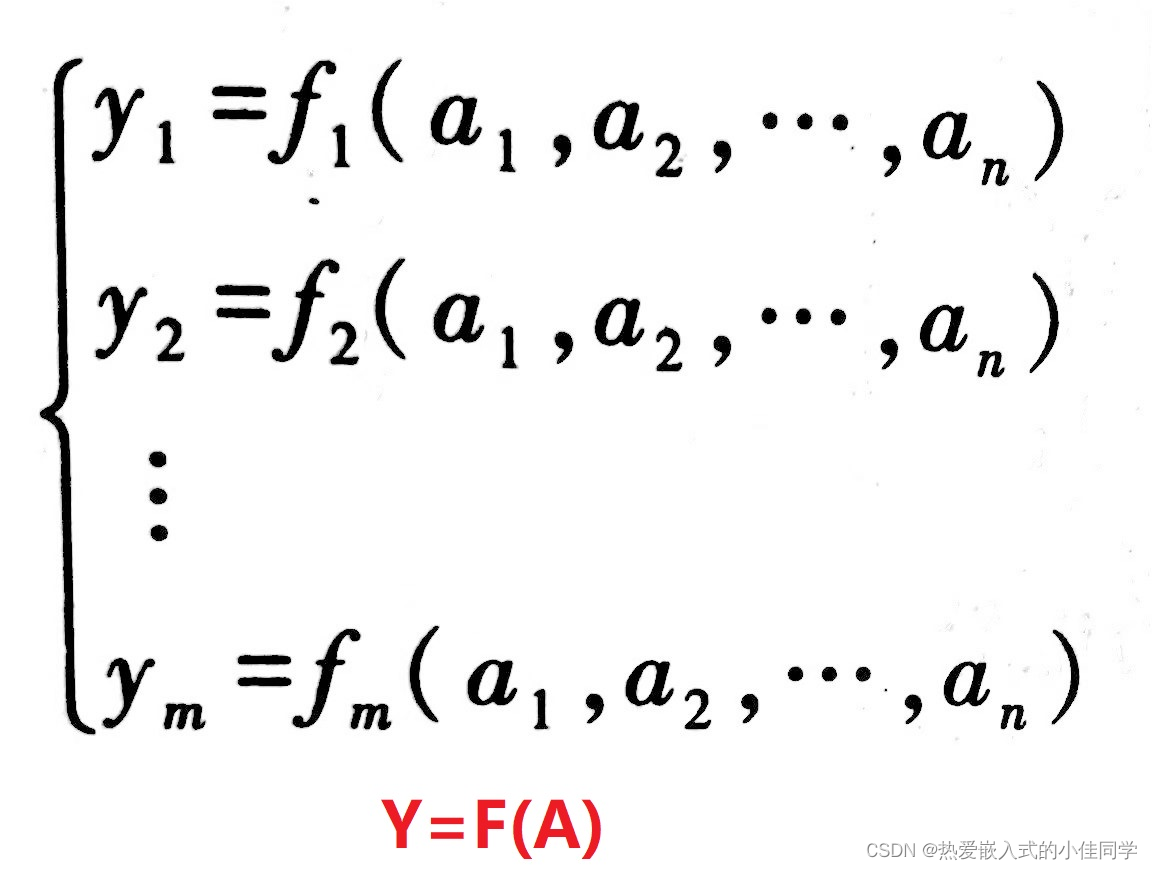

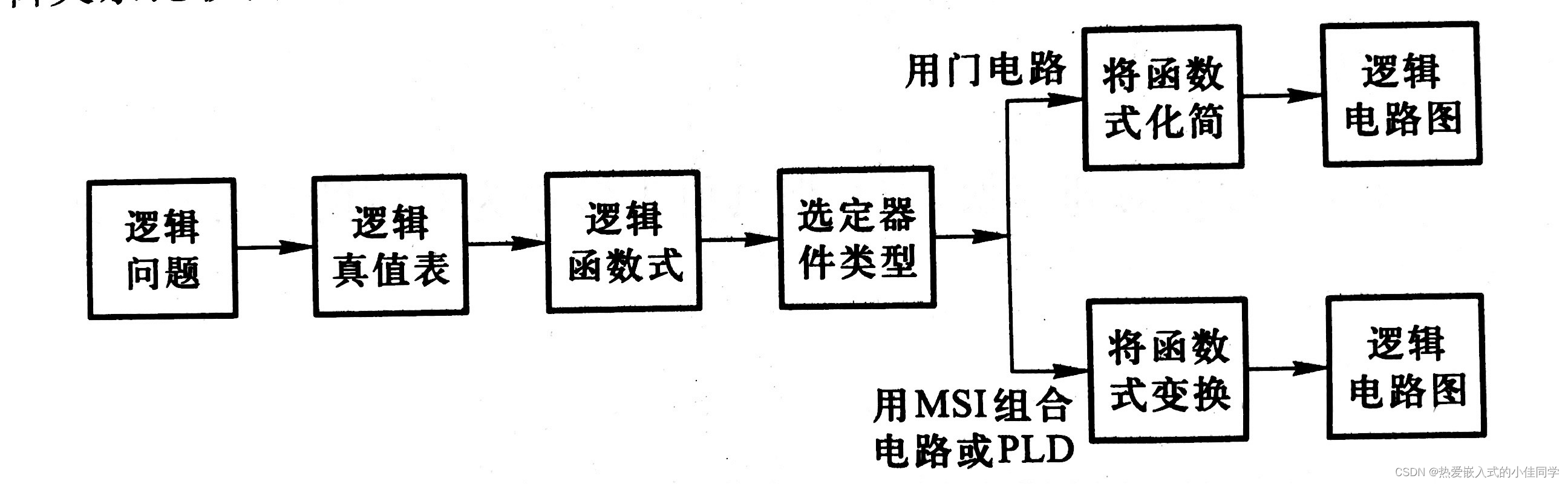

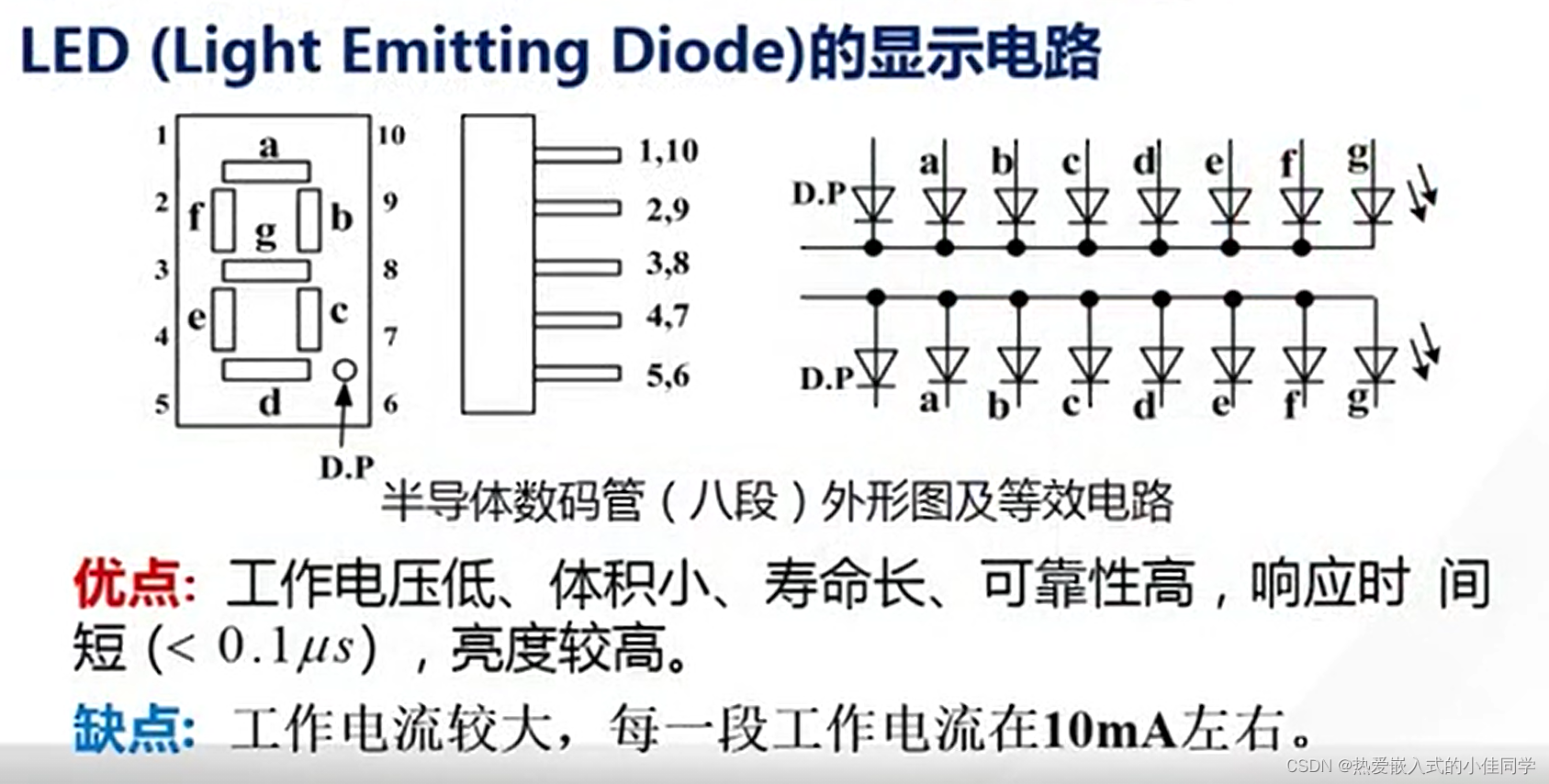

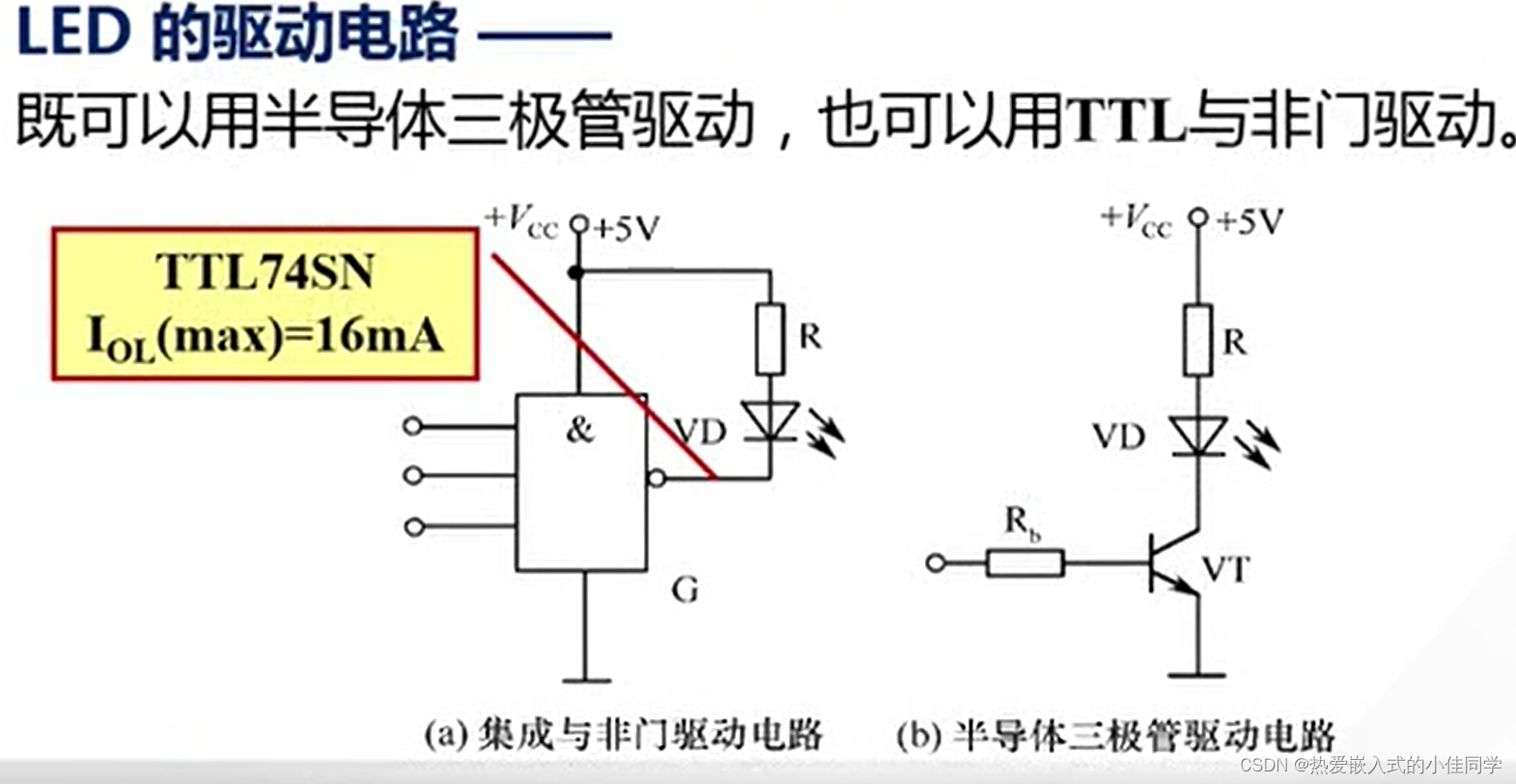

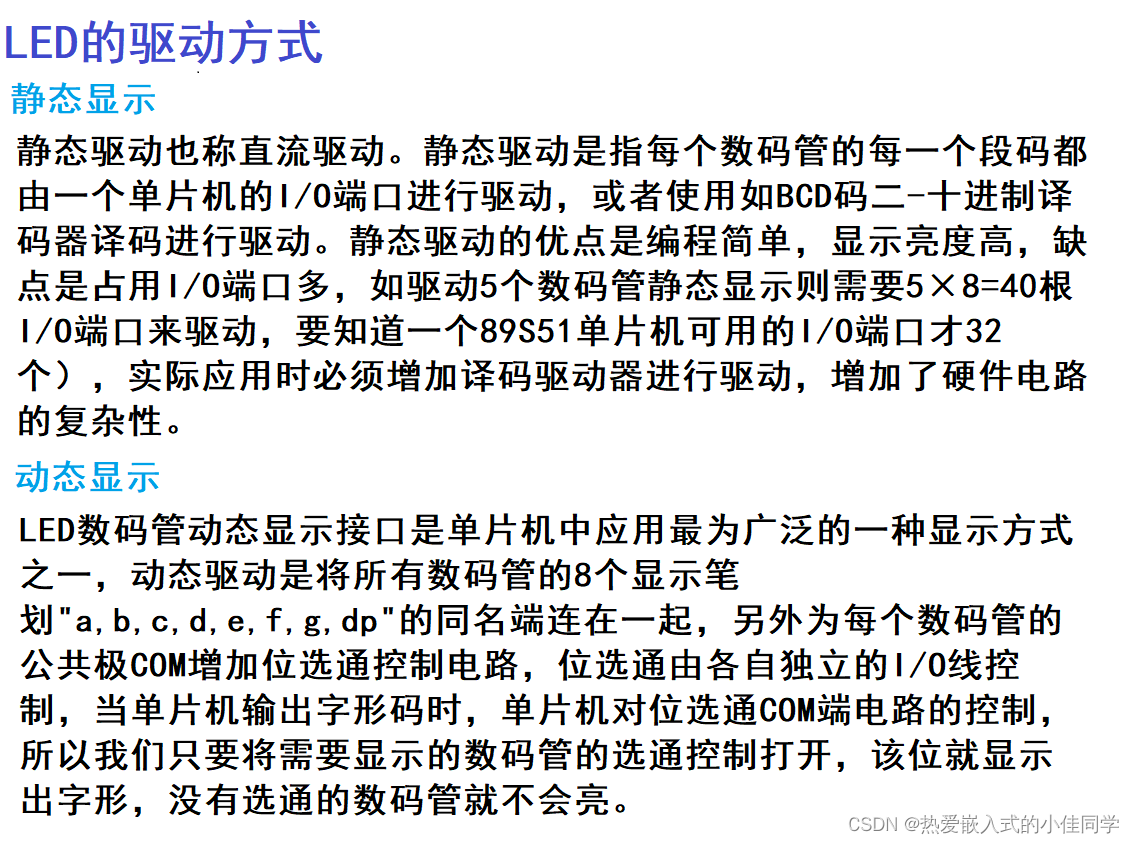

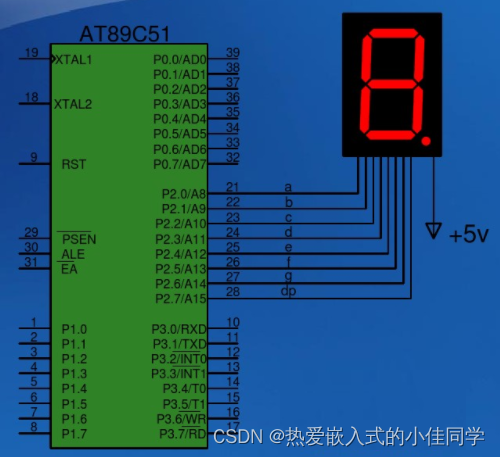

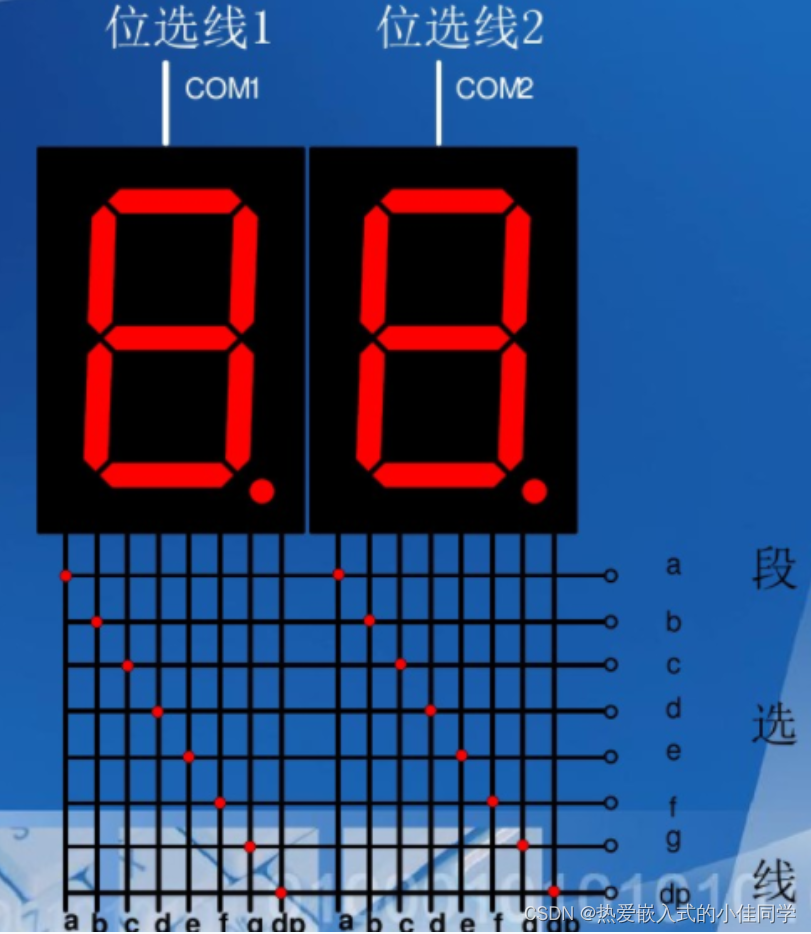

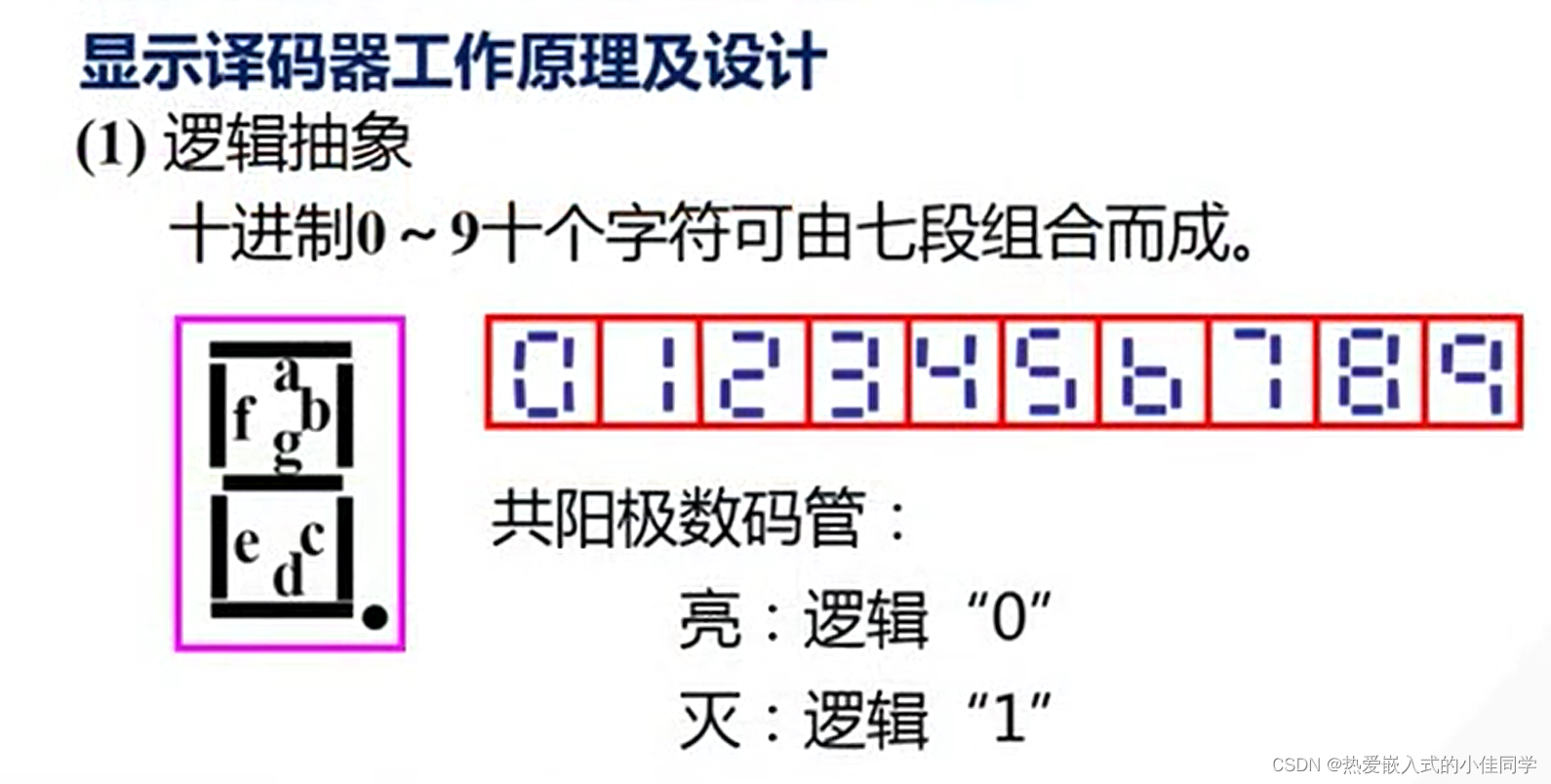

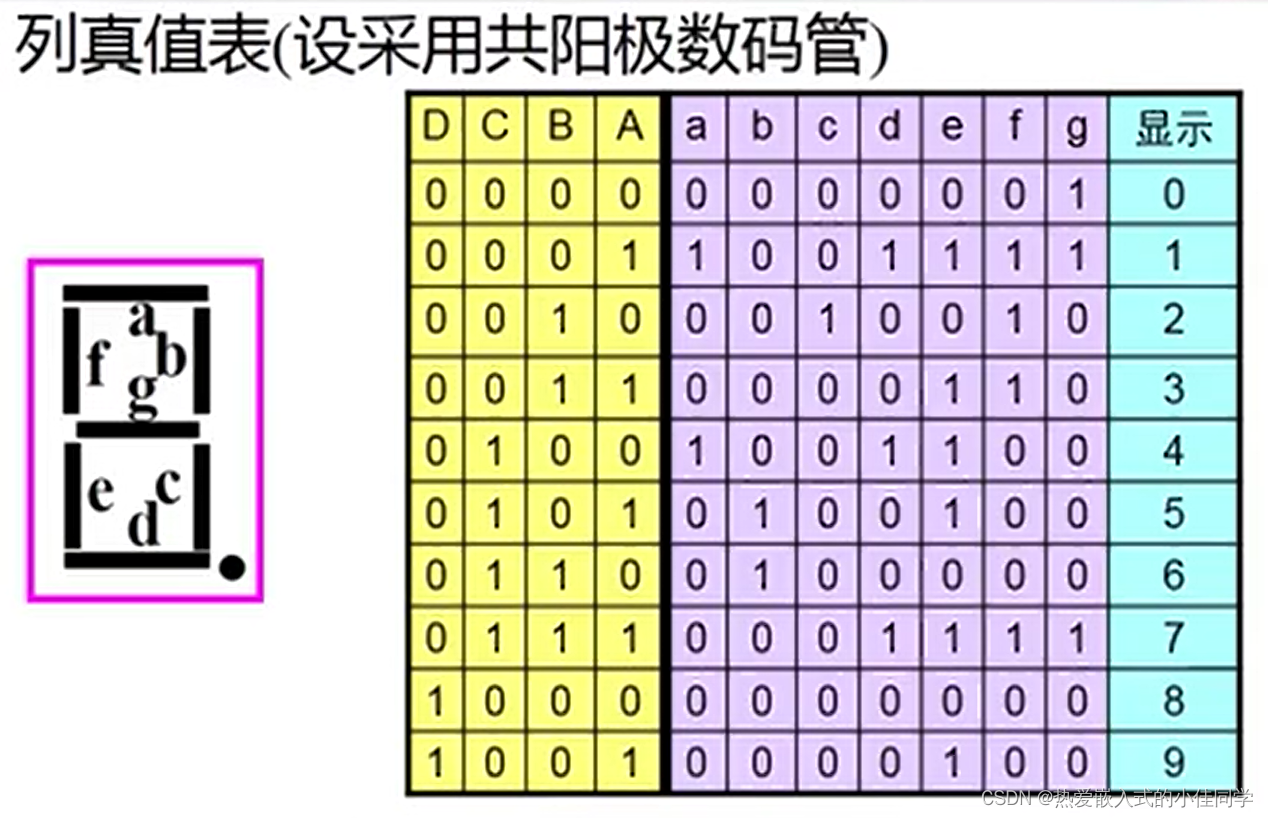

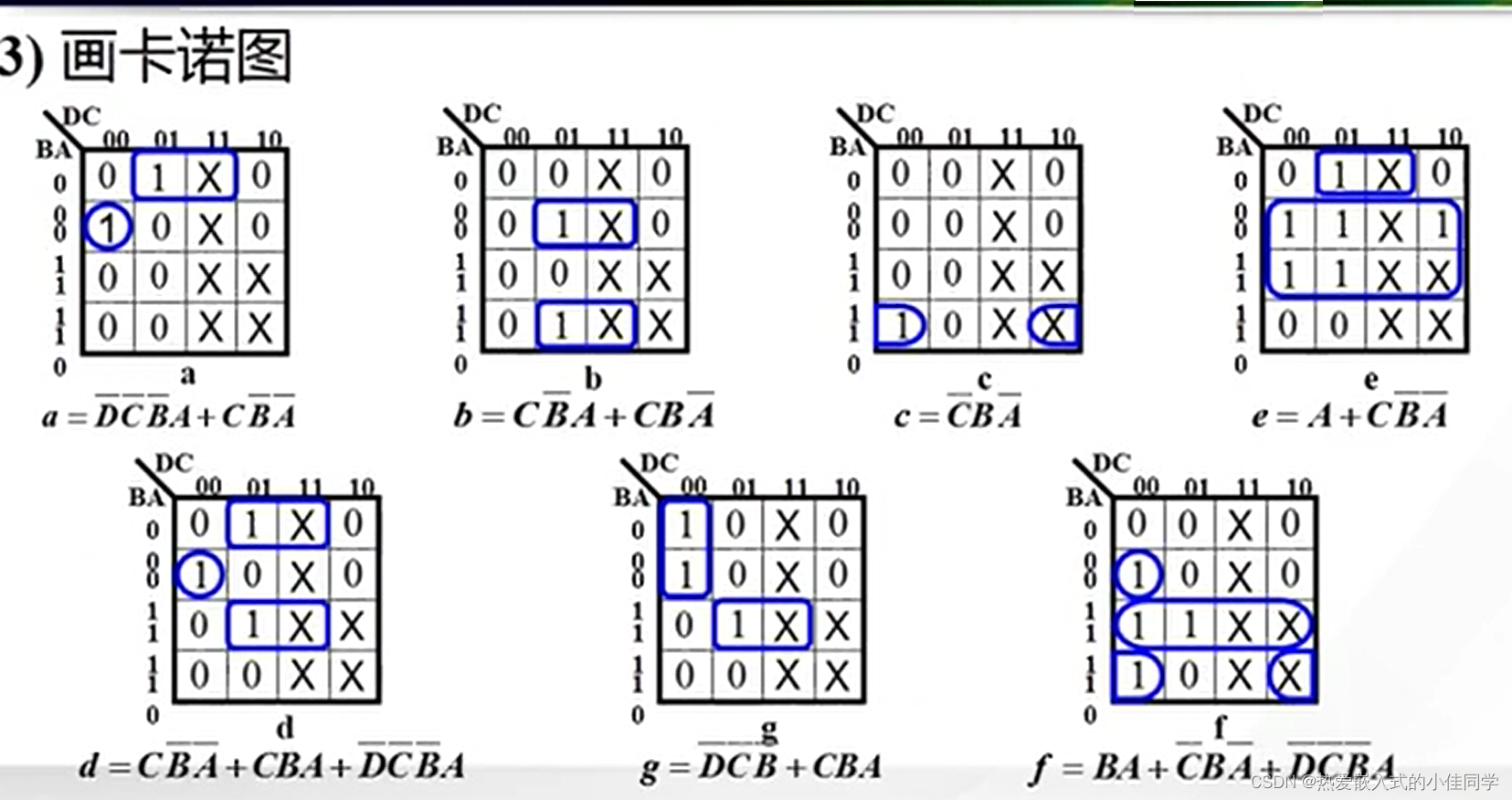

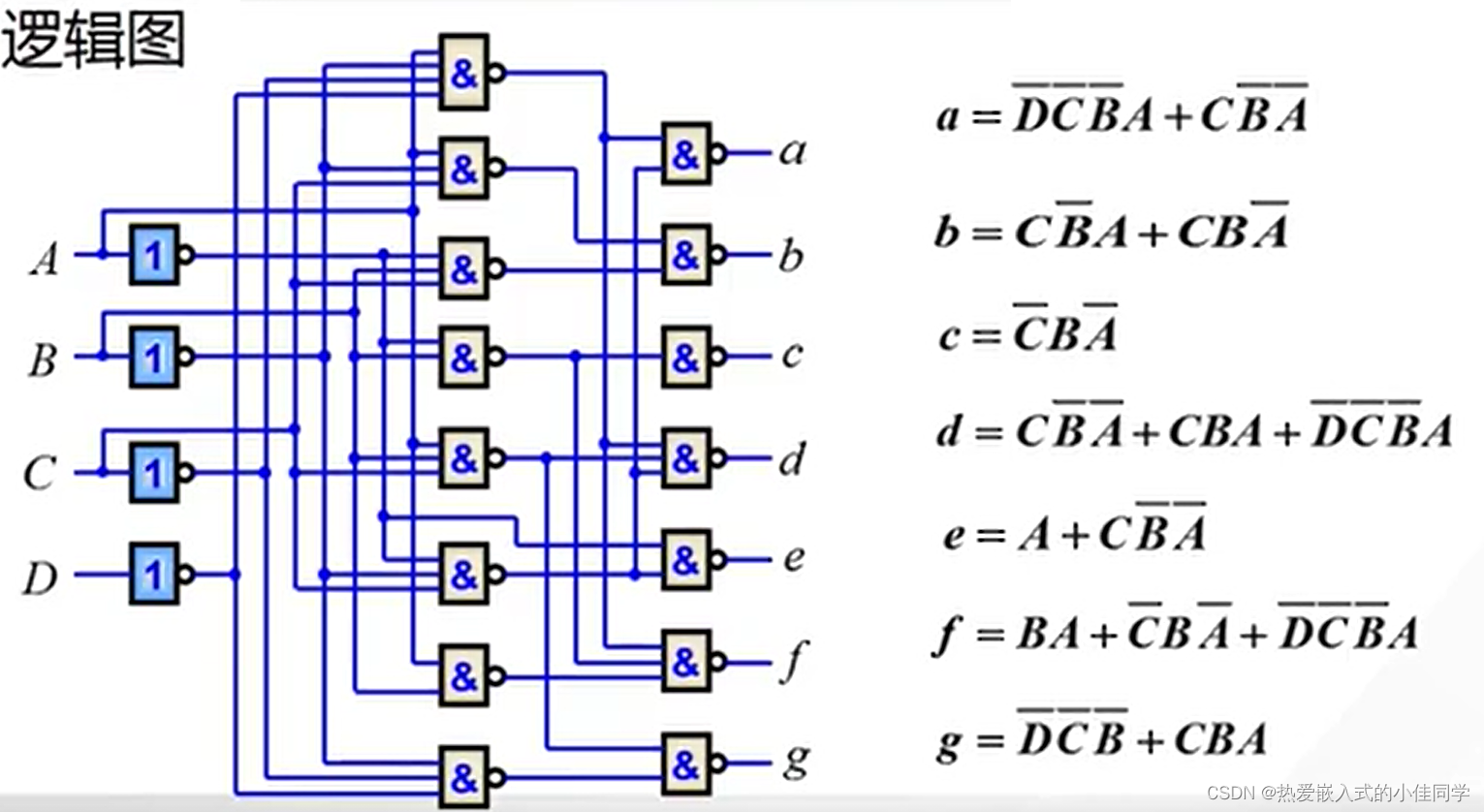

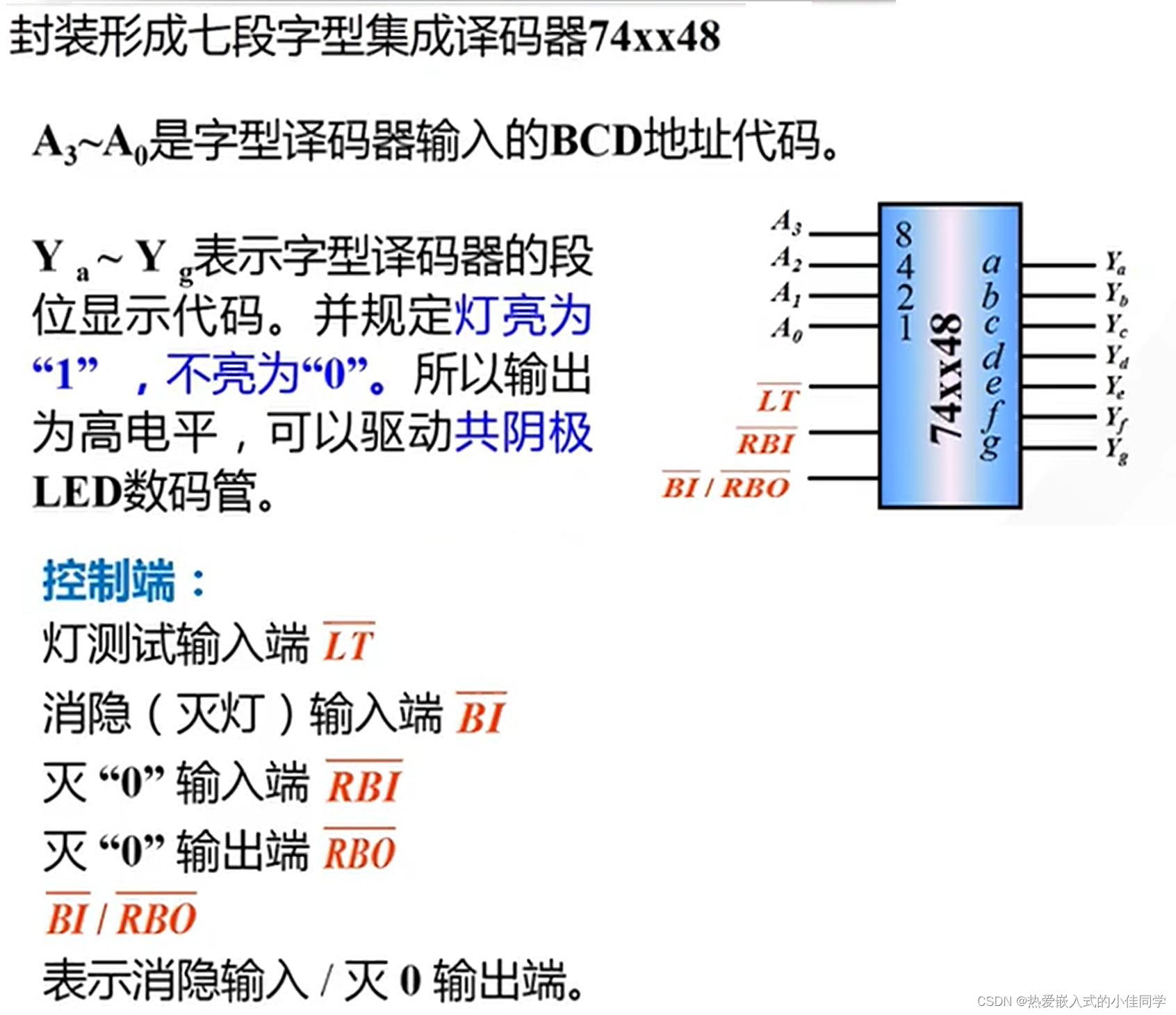

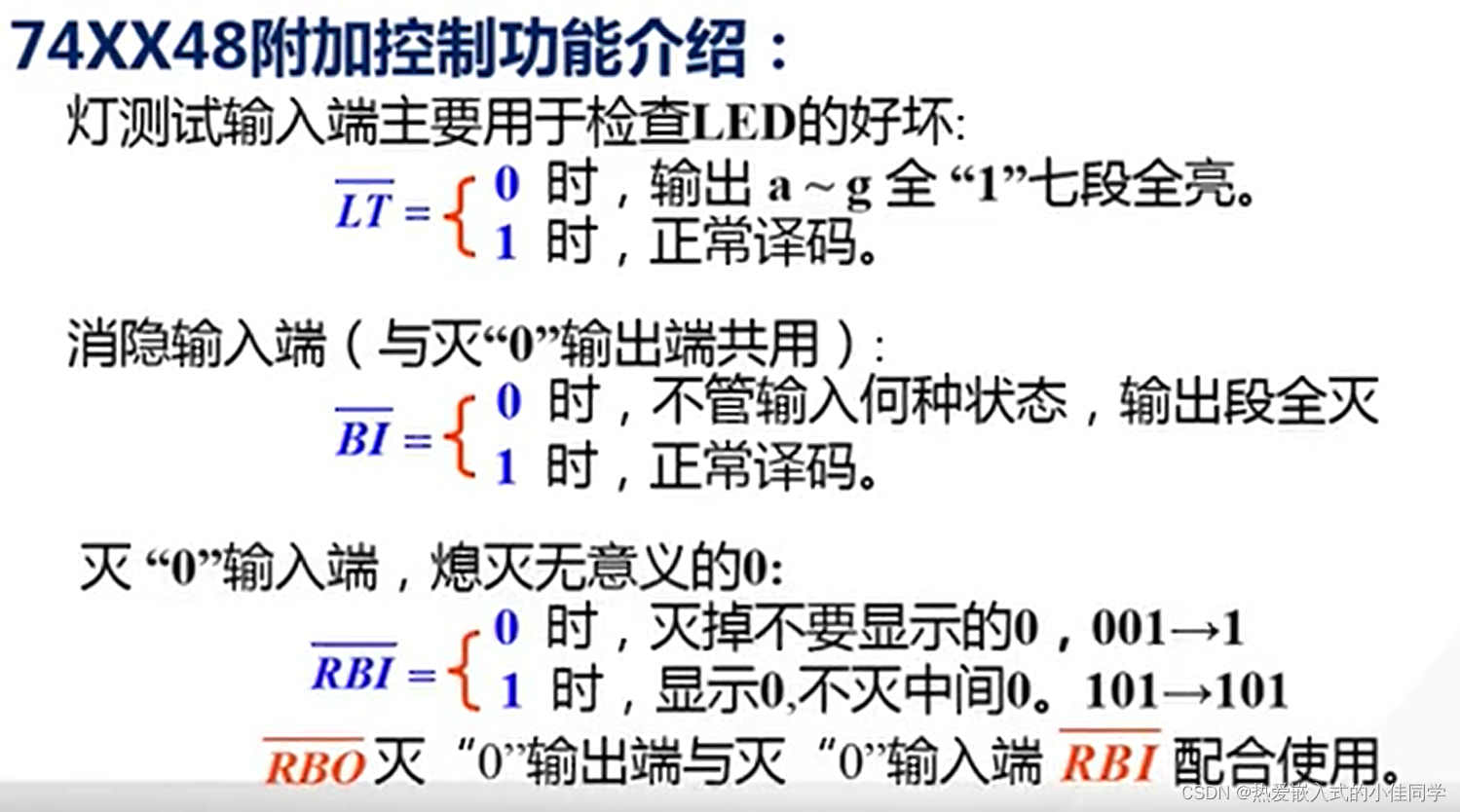

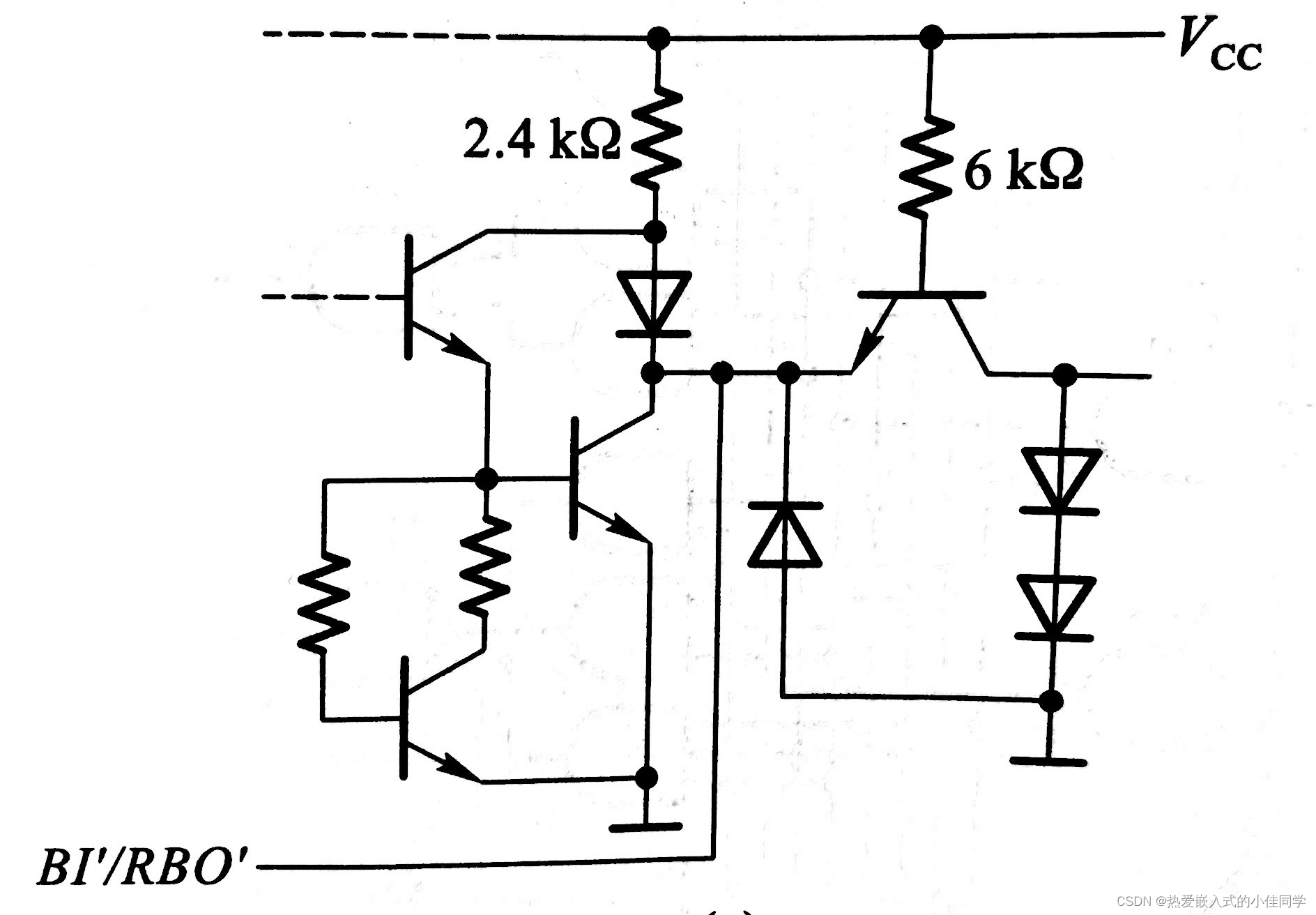

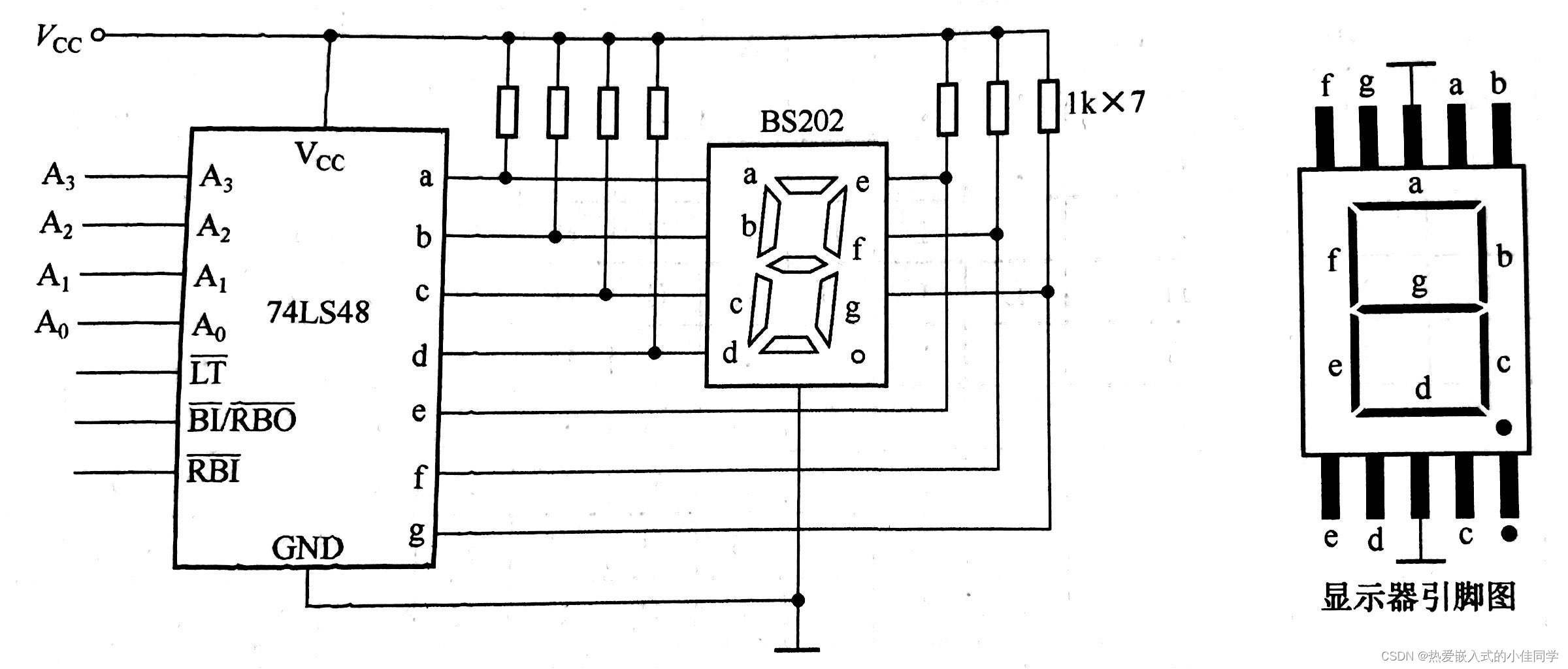

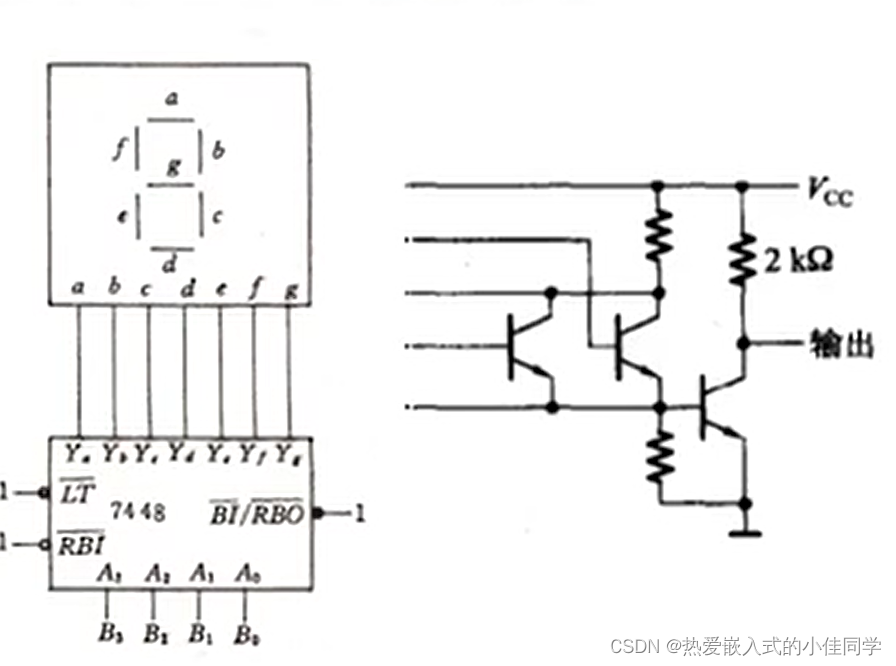

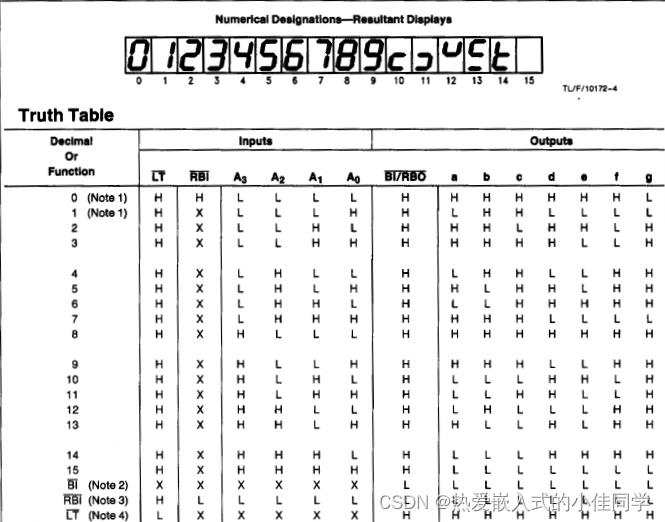

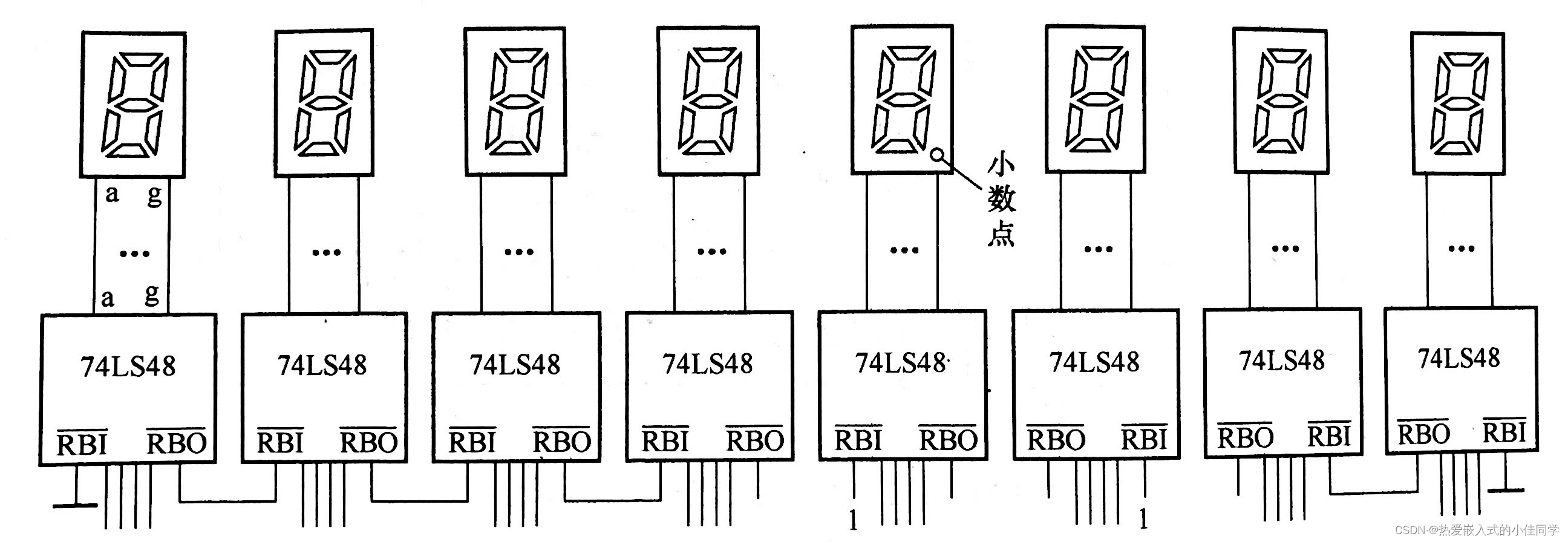

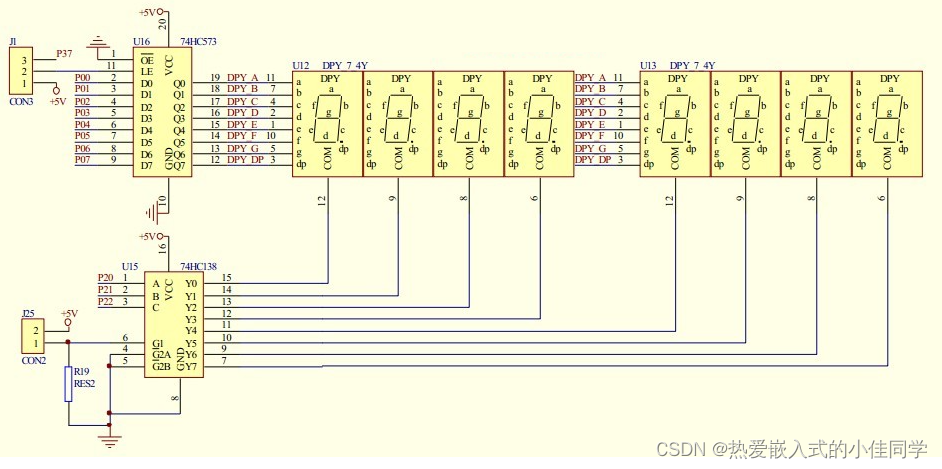

目录 一、组合逻辑电路的基本设计方法 1.特点 2.逻辑功能的描述 3.组合逻辑电路的分析步骤 4.组合逻辑电路的设计方法 二、编码器的逻辑电路 1.普通编码器 2.优先编码器 三、二进制和二-十进制译码器 1.3-8译码器 2.二-十进制译码器 3.应用:逻辑函数发生器 四、LED数码管原理 LED(Light Emitting Diode) 五、LCD段码液晶屏显示原理 六、显示译码器(Display Decoder) 七、用74LS48译码器控制LED数码管显示驱动能力 1.一位数码显示电路 2.多位数码显示电路 八、数据选择器(Data Selector) 九、加法器 1.串行进位加法器(Serial Carry Adder) 2.超前进位加法器(Carry Look ahead) 十、数值比较器 Comparator 1.一位数值比较器 2.多位数值比较器 十一、可编程逻辑器件 十二、组合逻辑电路中的竞争-冒险现象 1.竞争冒险之间的关系 2.竞争-冒险的危害性 3.竞争-冒险的判别方法 4.竞争-冒险的消除方法 一、组合逻辑电路的基本设计方法 1.特点任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。

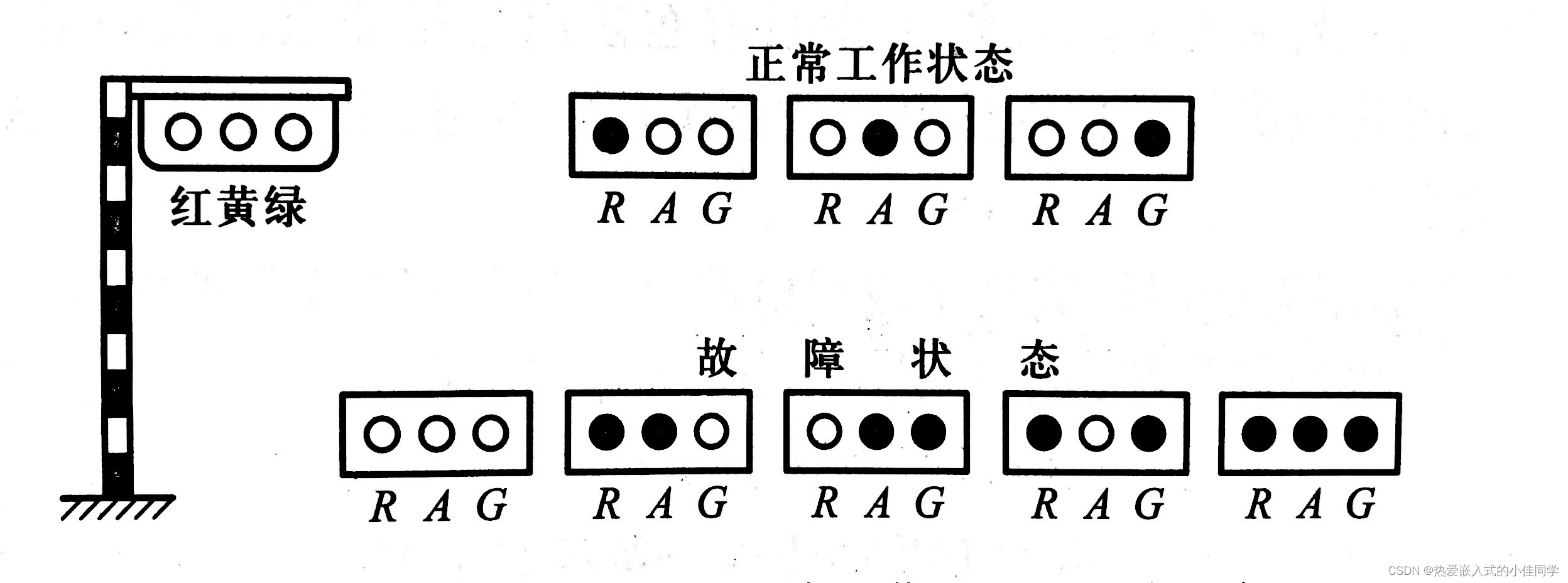

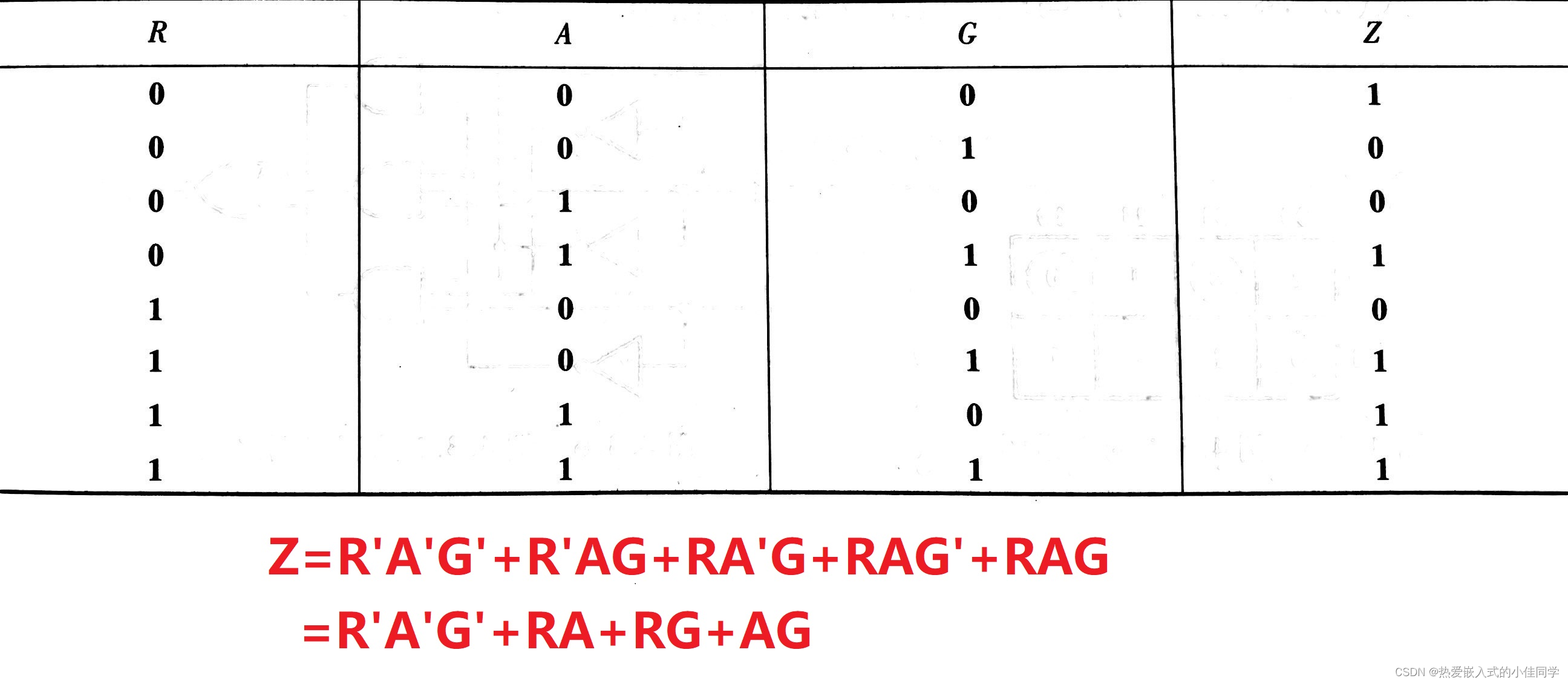

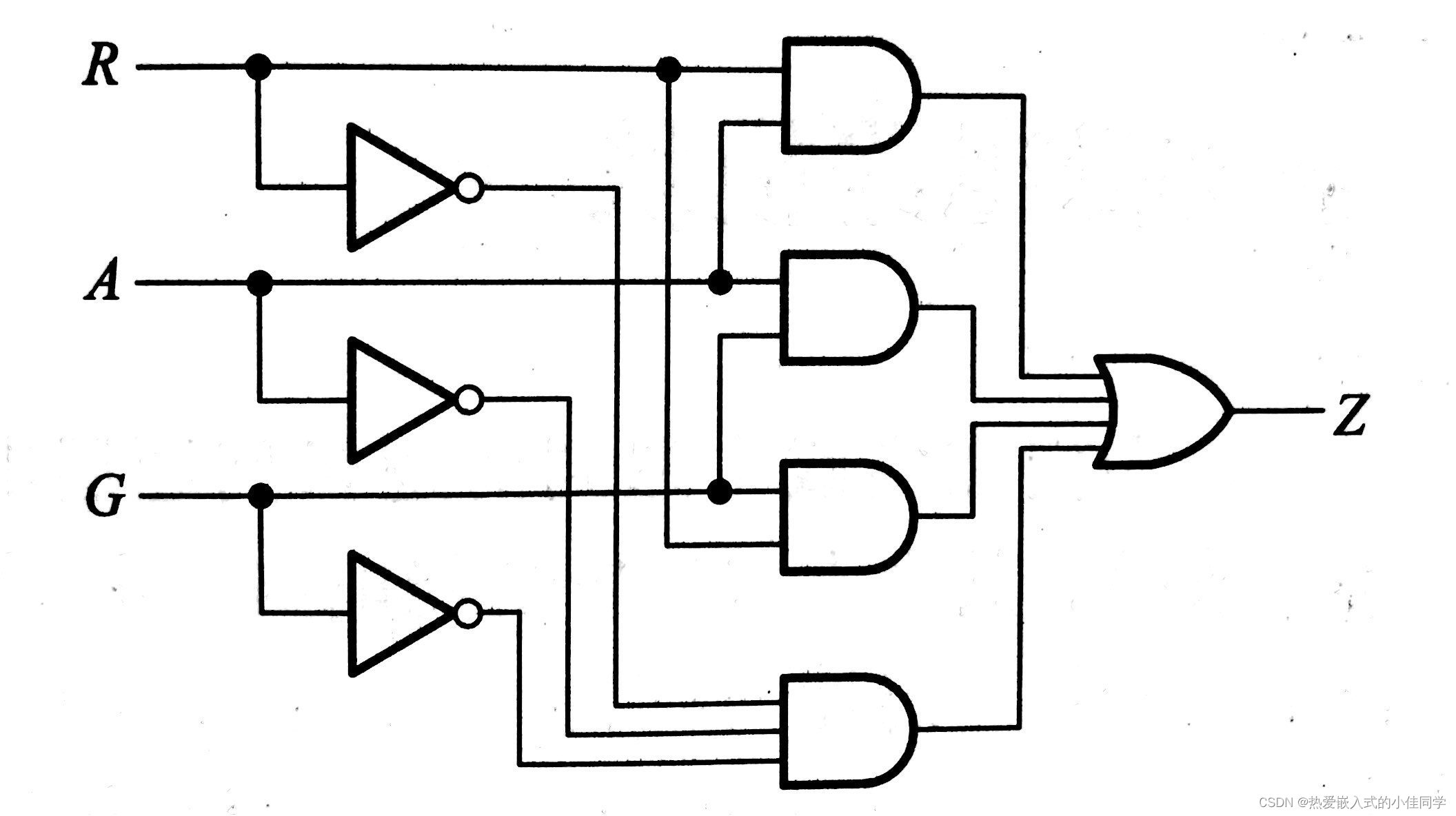

红绿灯设计:

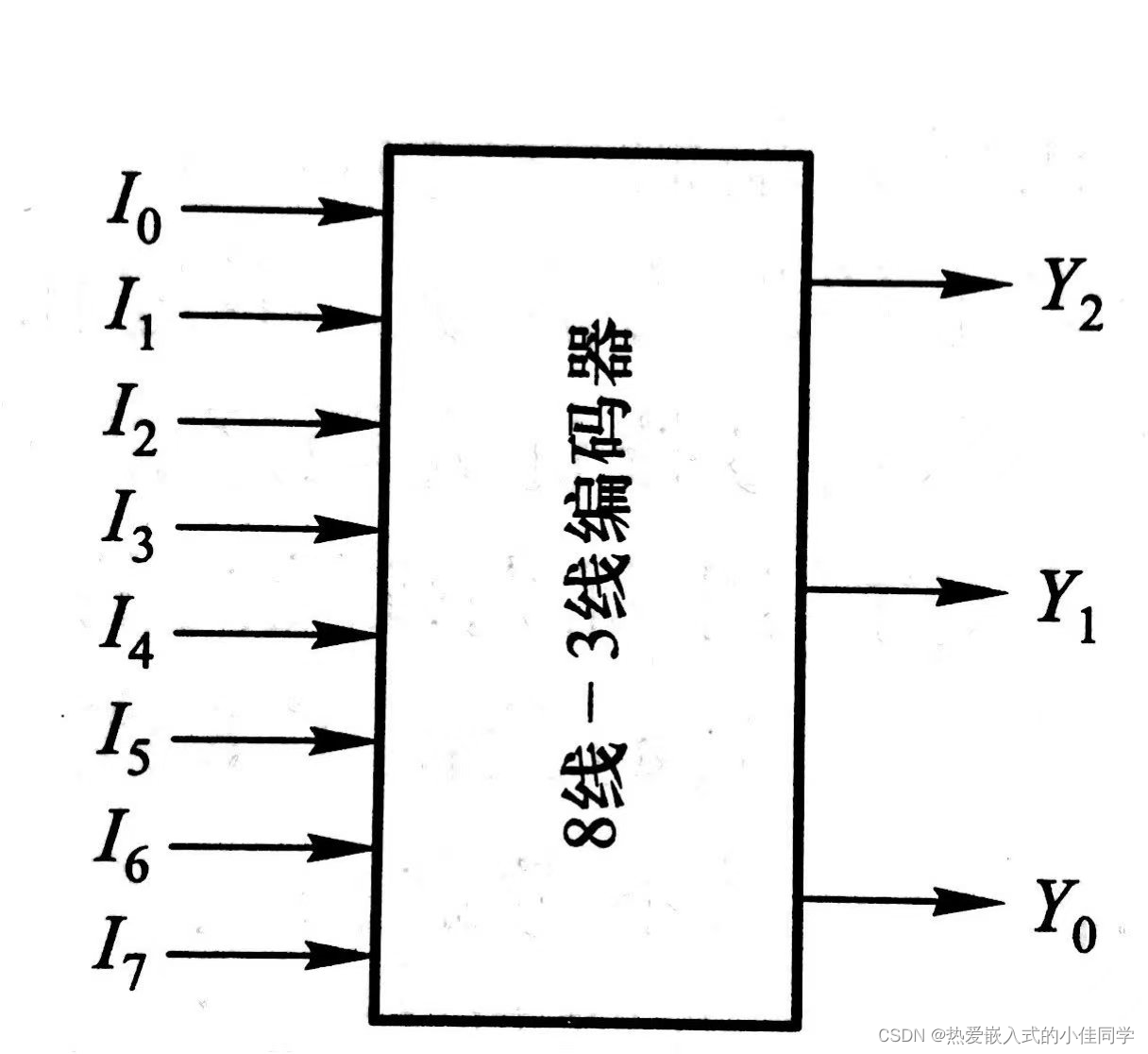

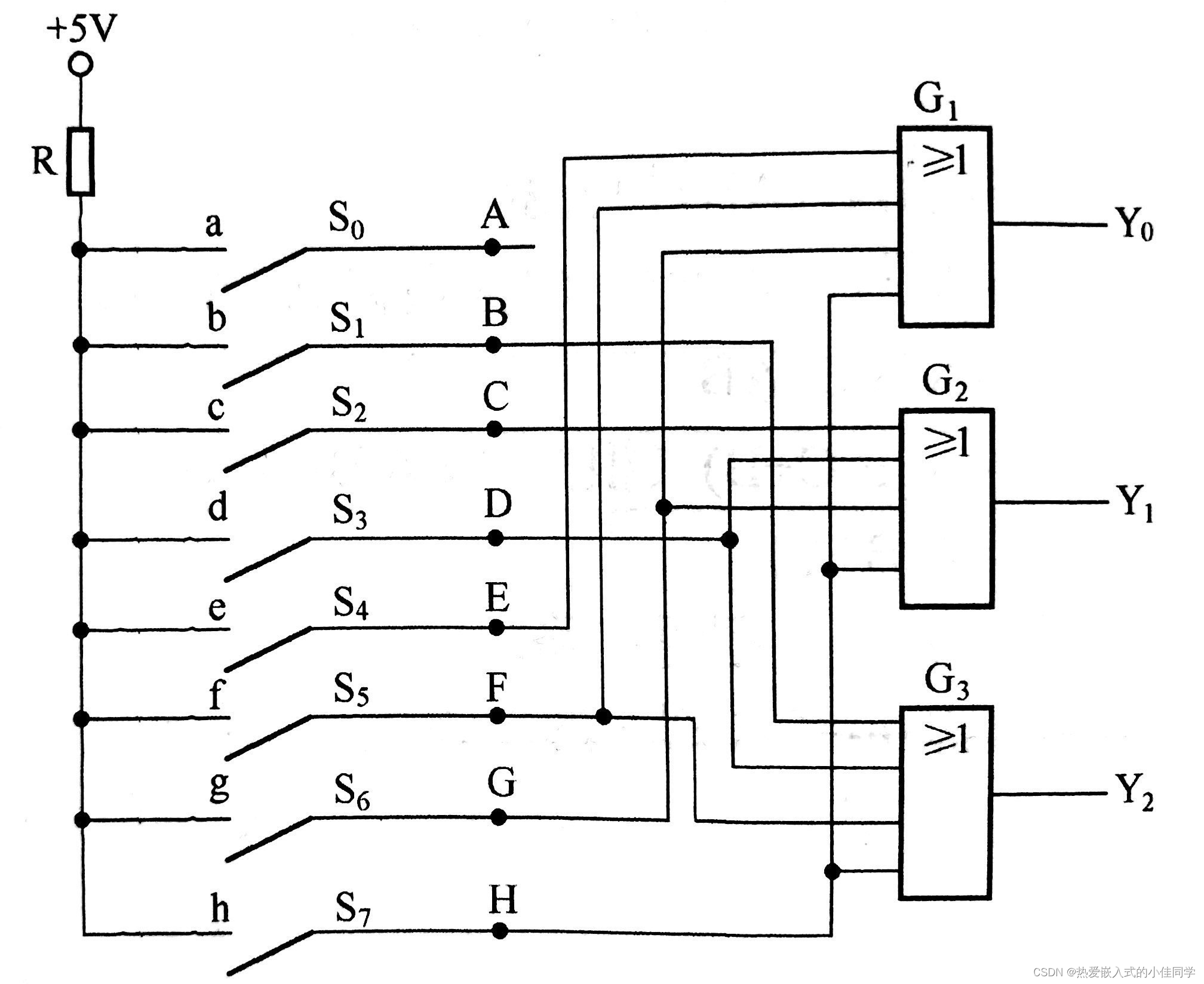

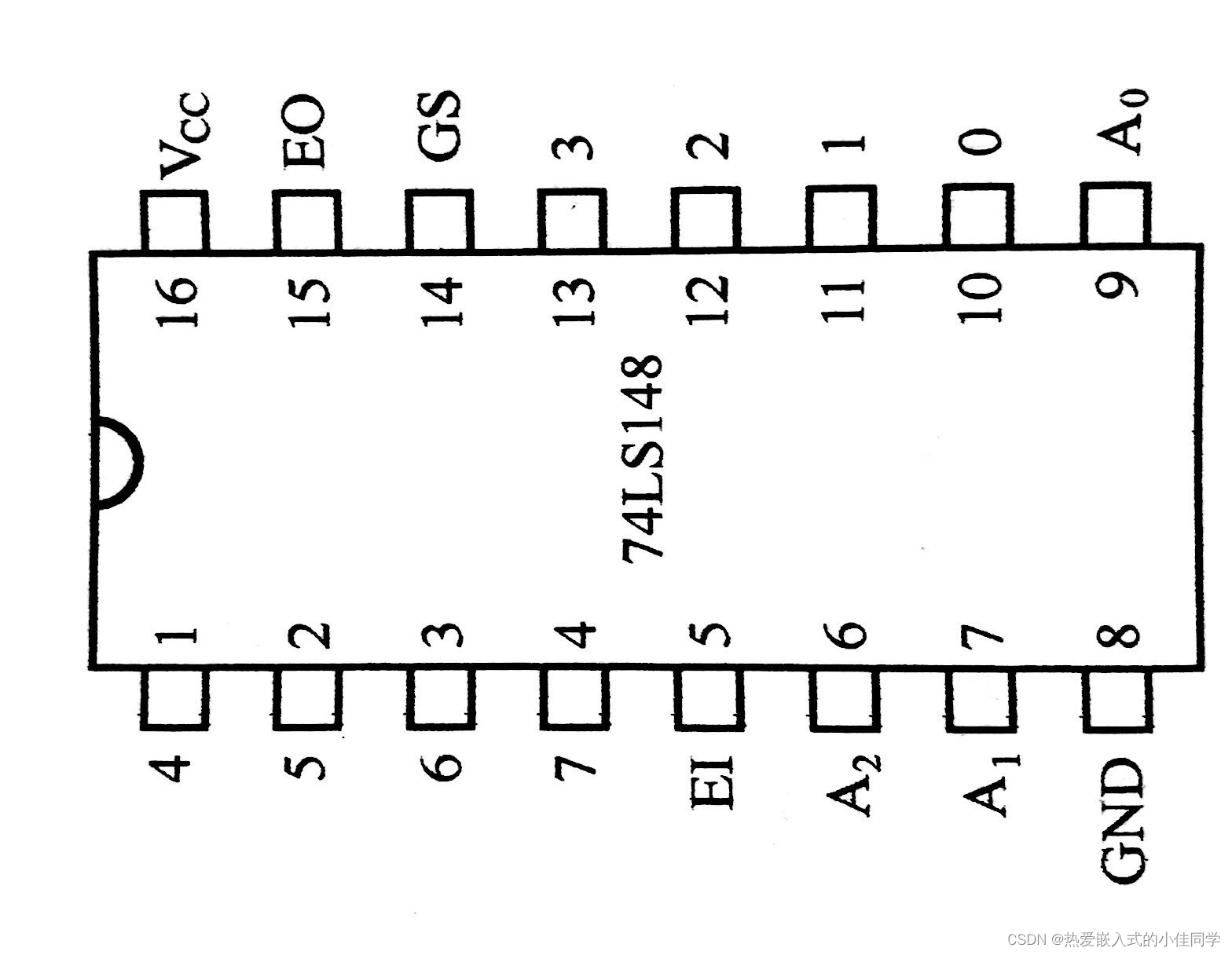

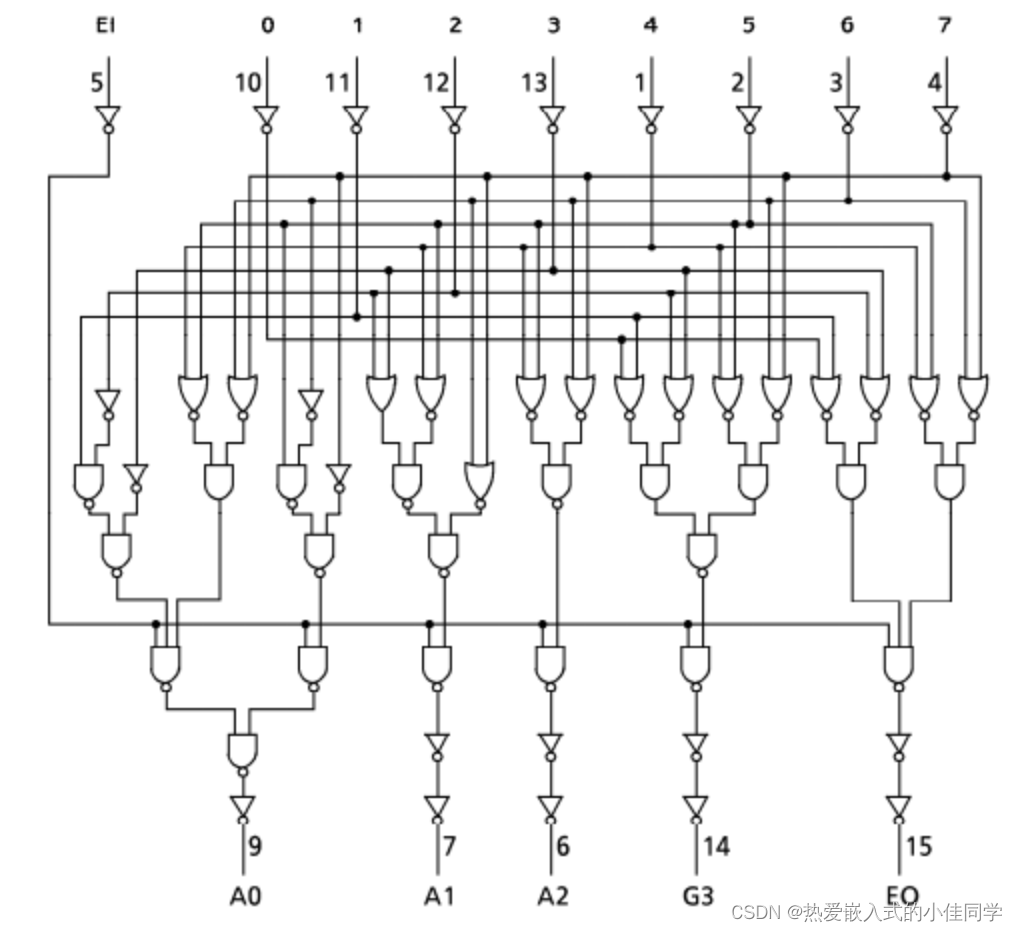

在数字电路中,将含有特定意义的数字和符号信息转换成相应若干位二进制代码的过程称为编码。 编码器(Encoder): 具有编码功能的组合逻辑电路 分类:普通编码器和优先编码器或二进制编码器和二-十进制编码器 1.普通编码器任何时刻只允许输入一个信号,若同时输入多个信号,编码输出就会产生混乱 例如:8-3编码器

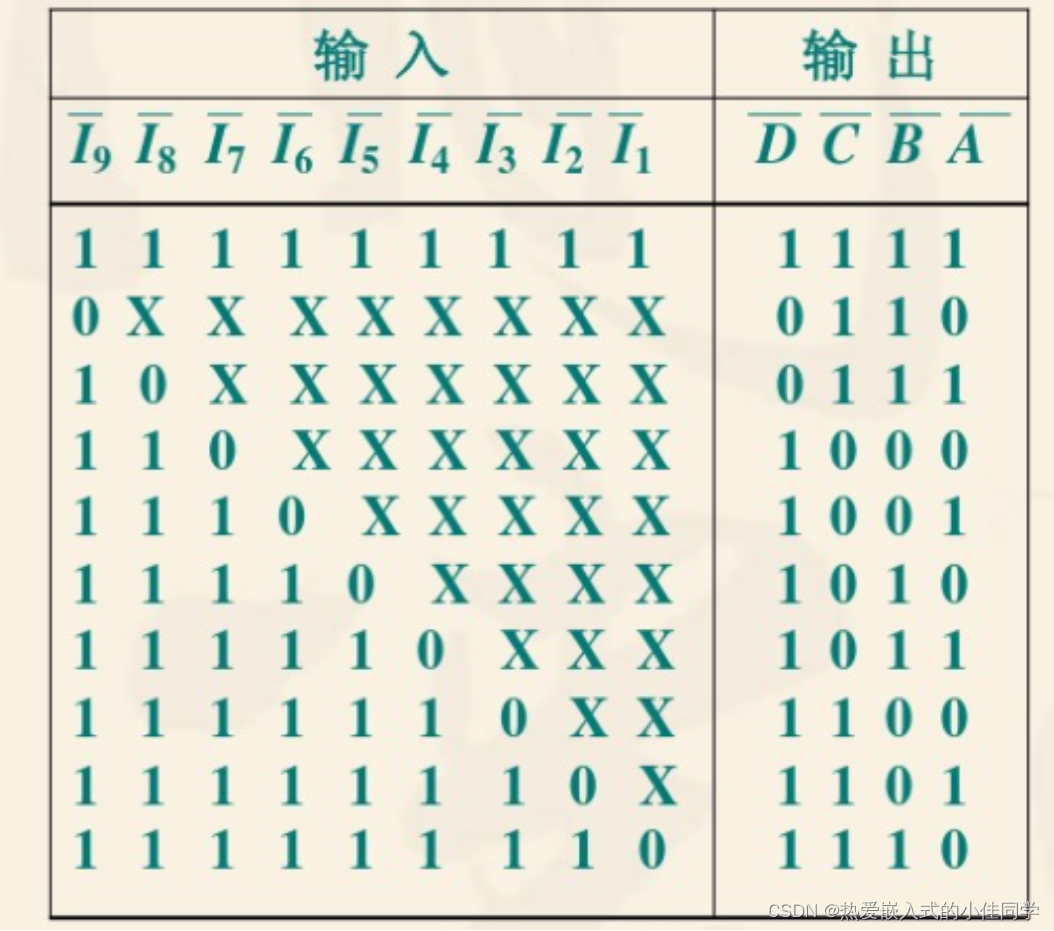

同一时刻允许多个输入信号,但仅对输入信号优先级别最高的一个信号进行编码输出。

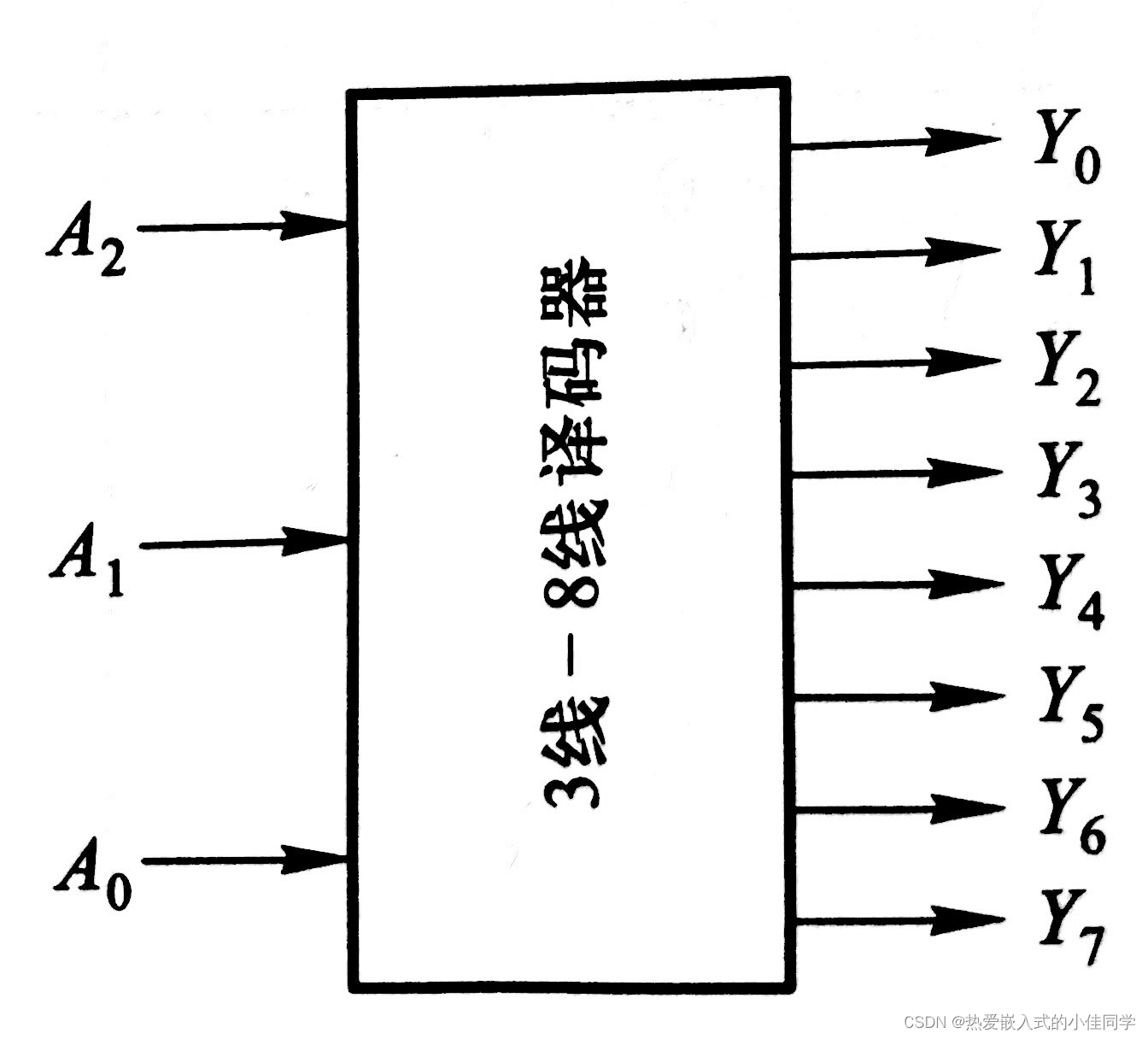

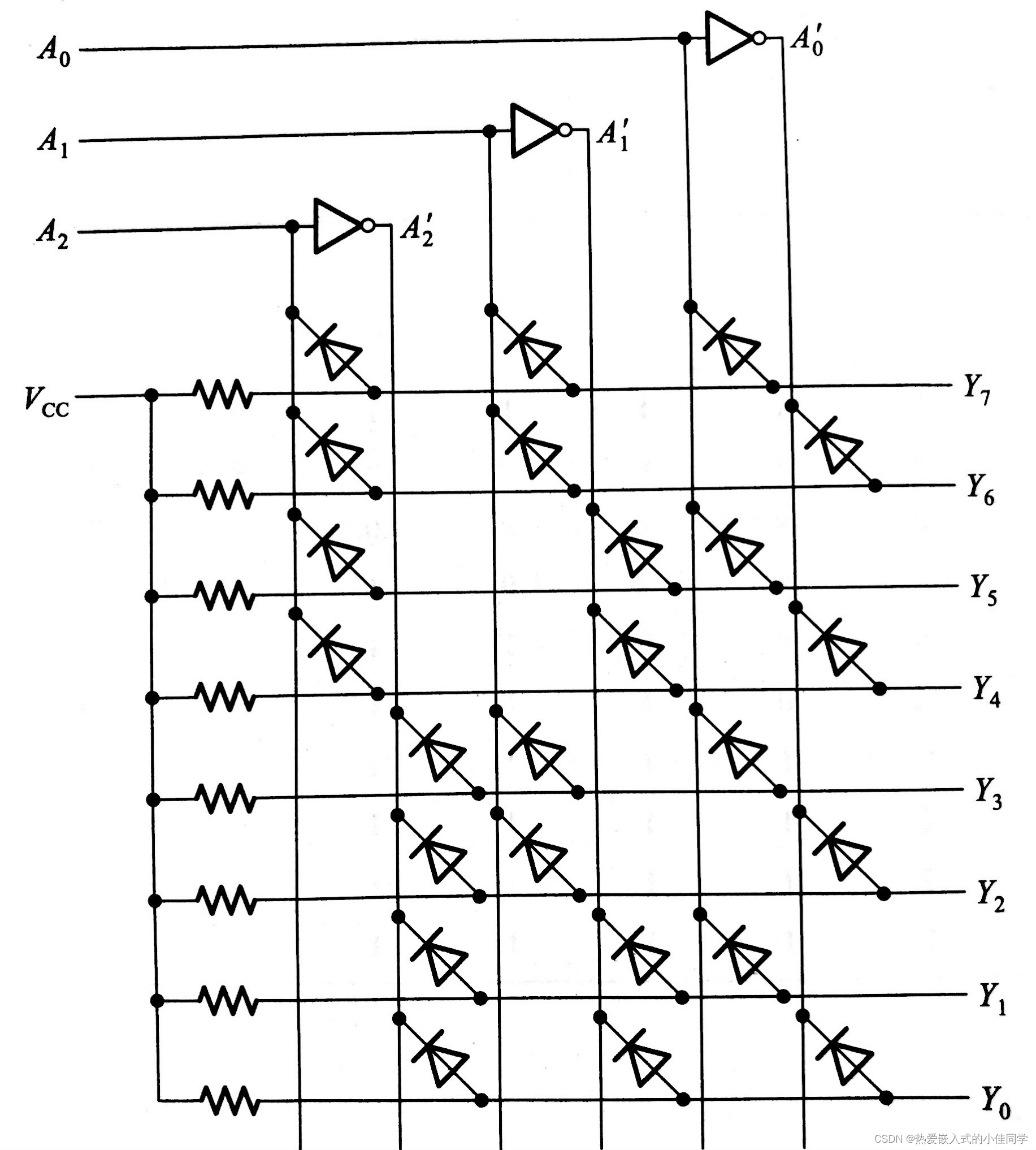

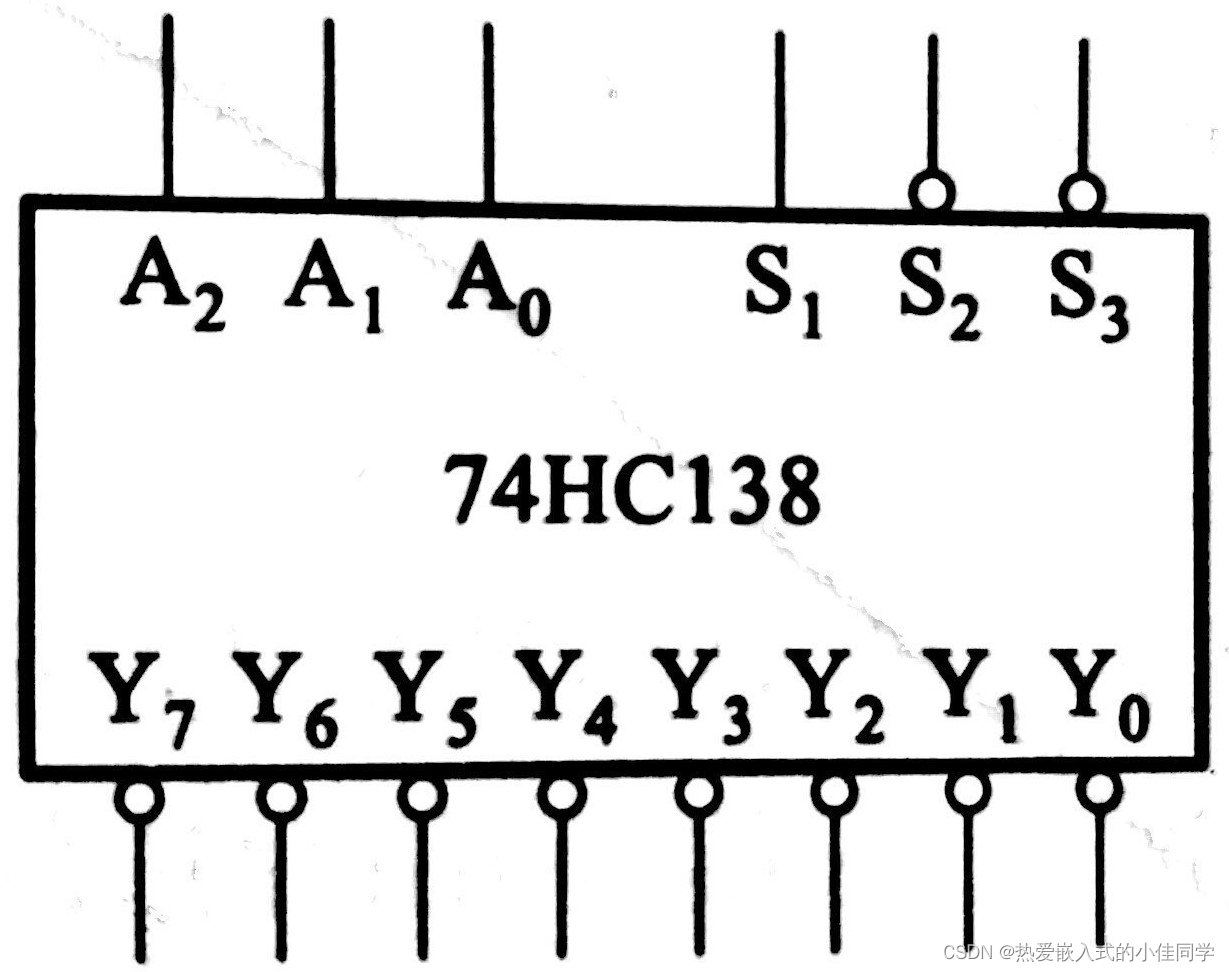

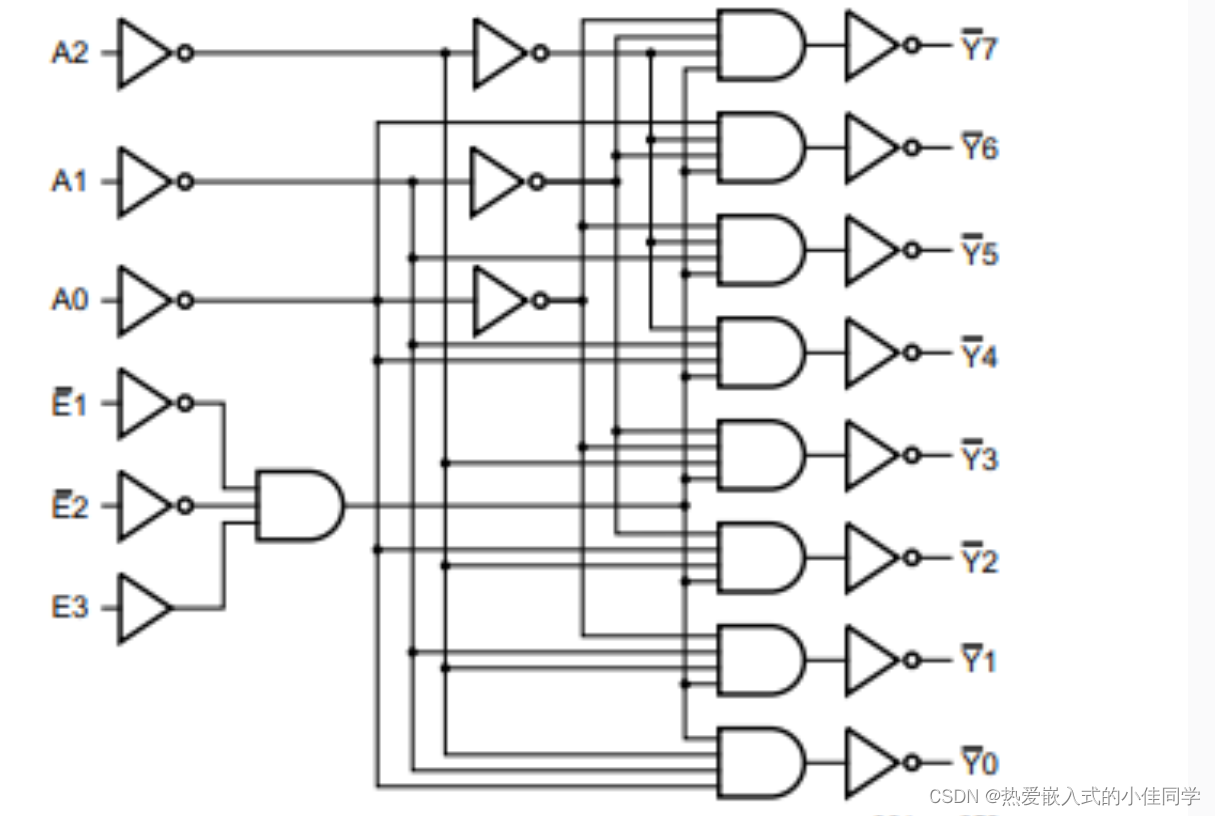

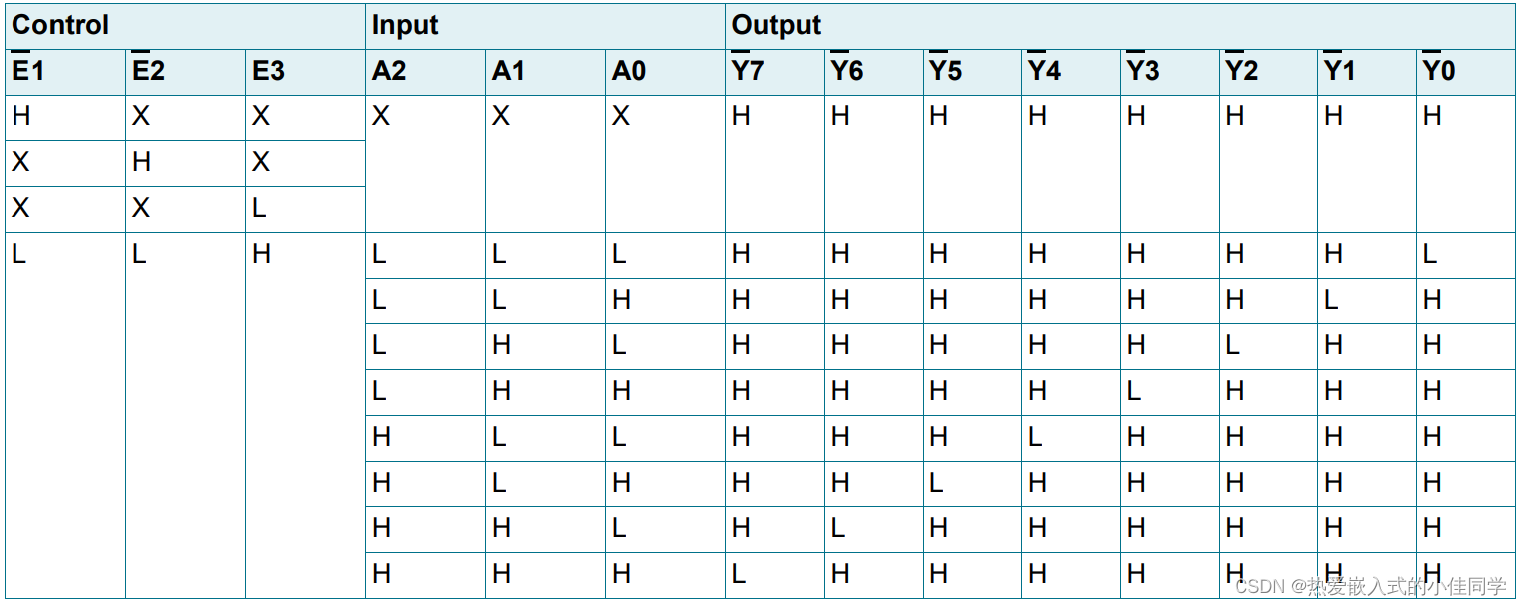

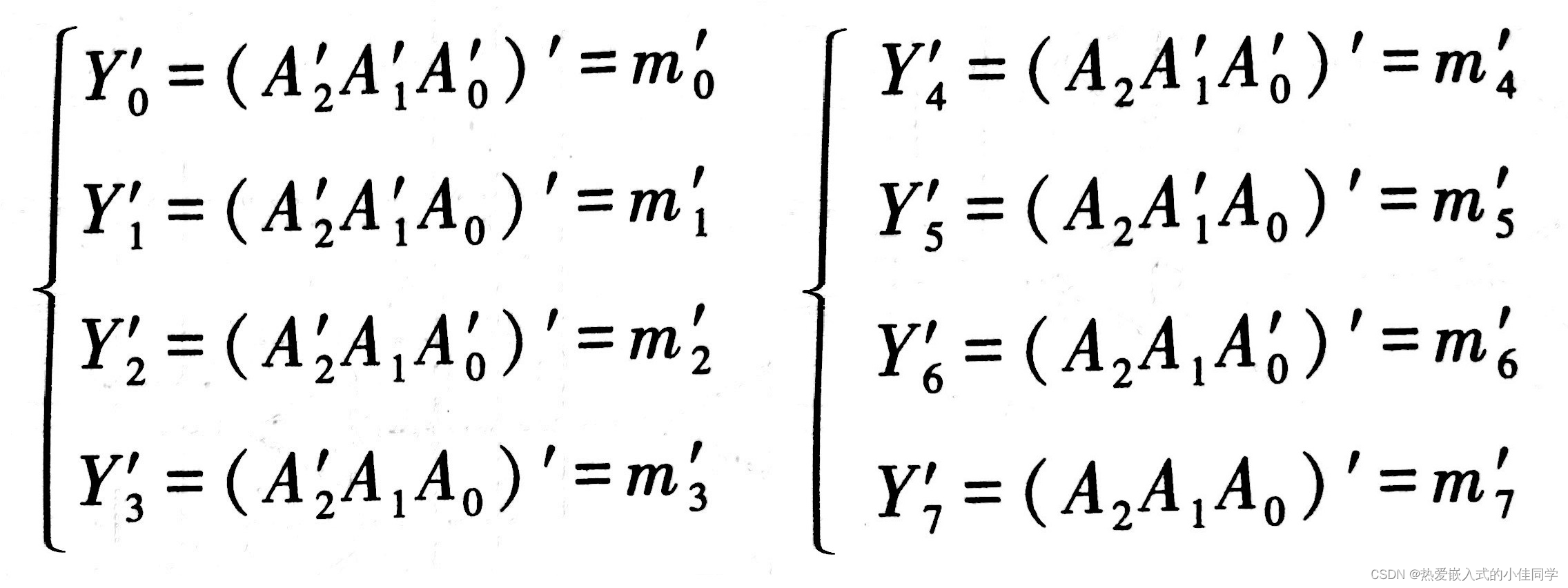

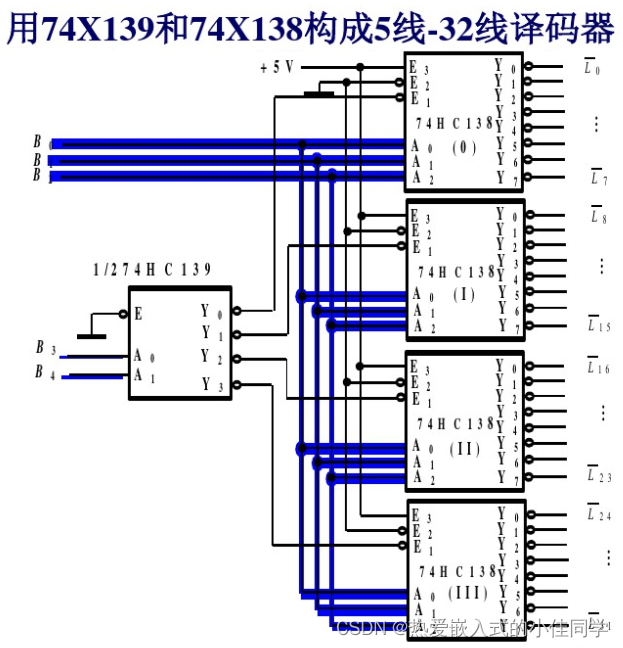

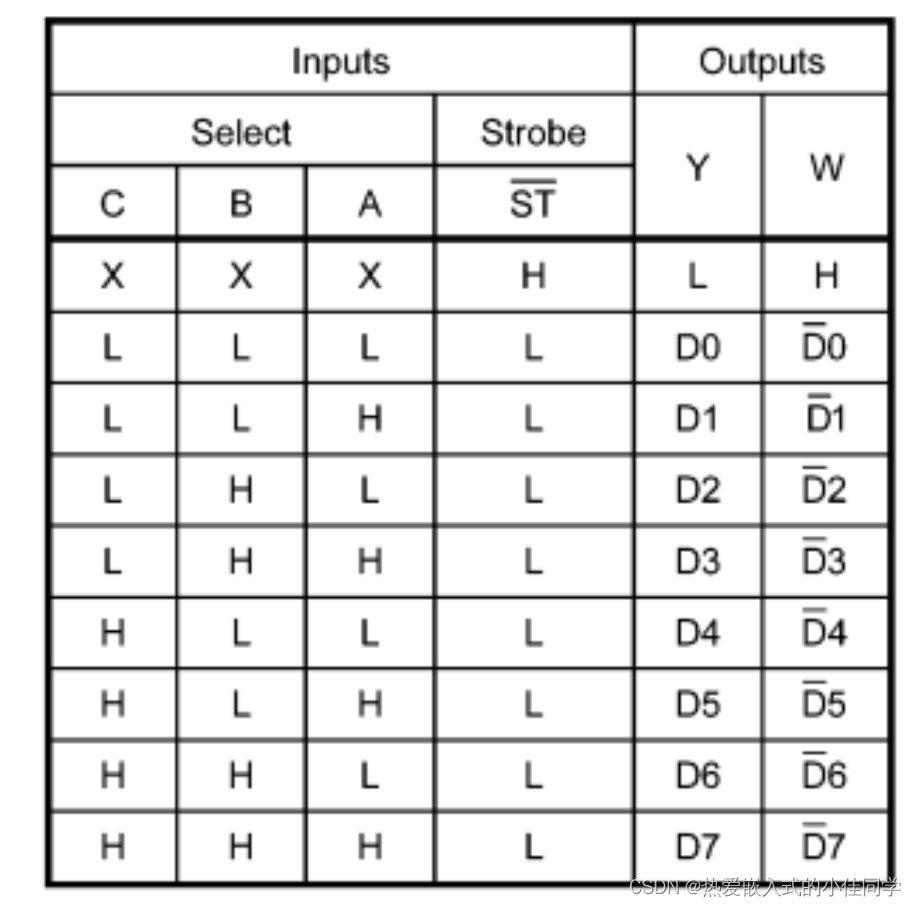

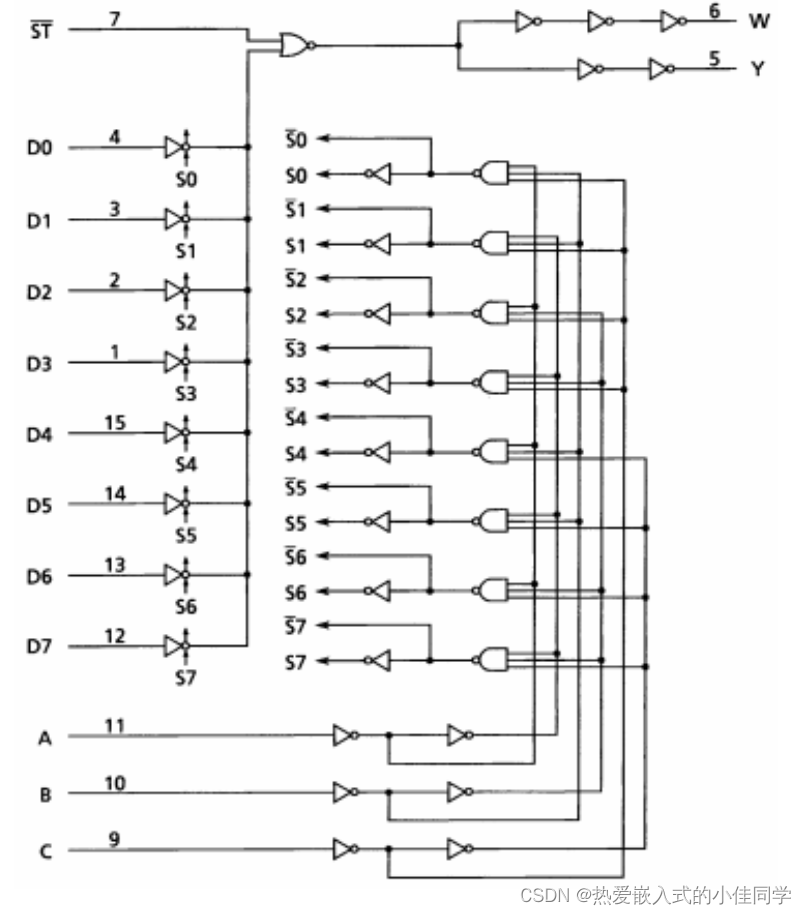

将每个输入的二进制代码译成对应的输入高、低电平信号或另外一个代码。 常见的有二进制译码器、二-十进制译码器和显示译码器 (Decoder) 二进制译码器:输入是一组二进制代码,输出是一组与输入代码一一对应的高低电平信号 1.3-8译码器

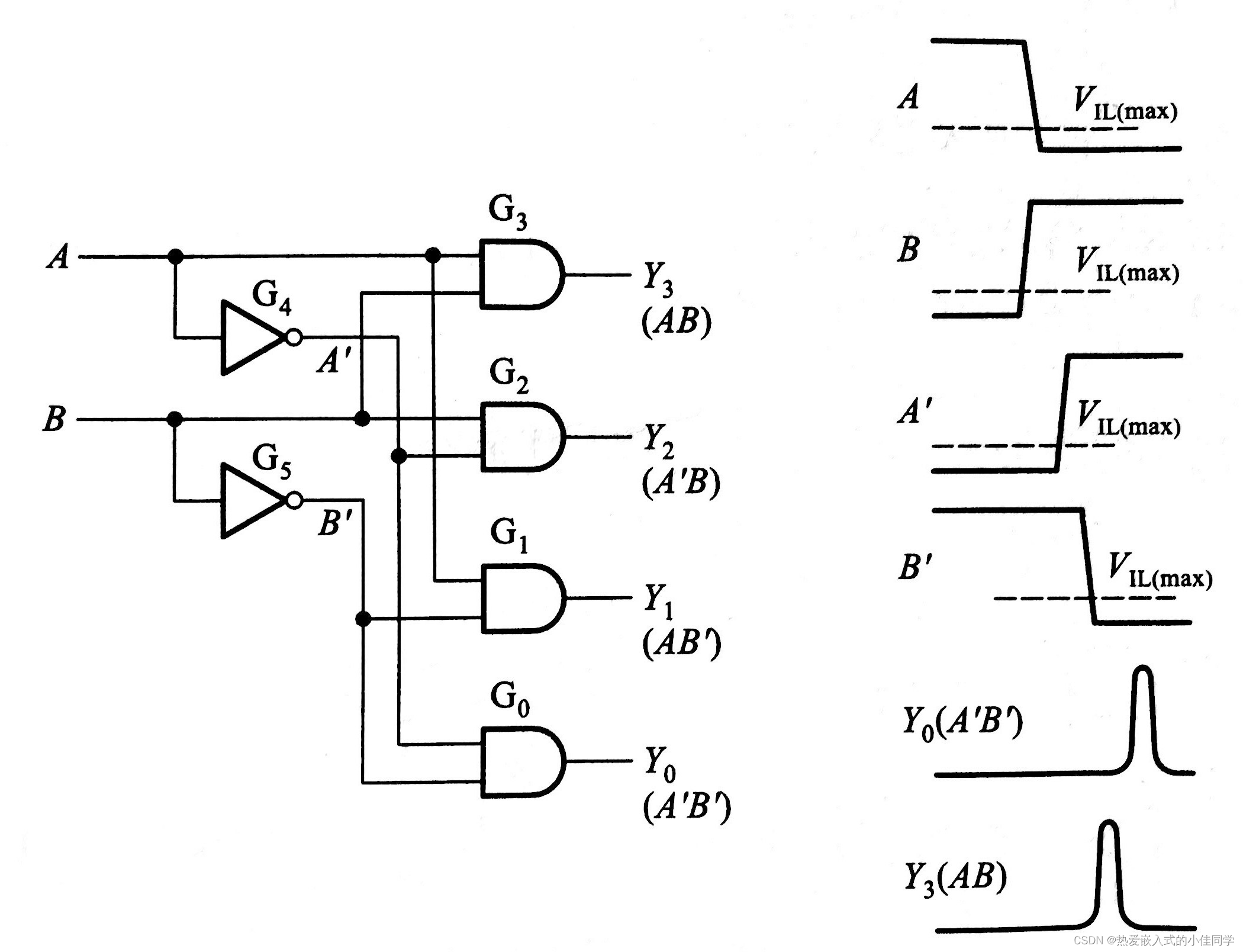

CMOS门电路组成的3线-8线译码器:

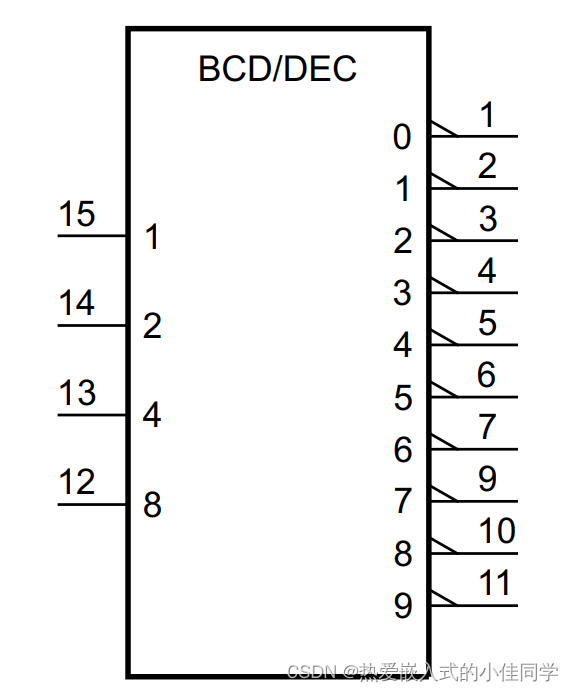

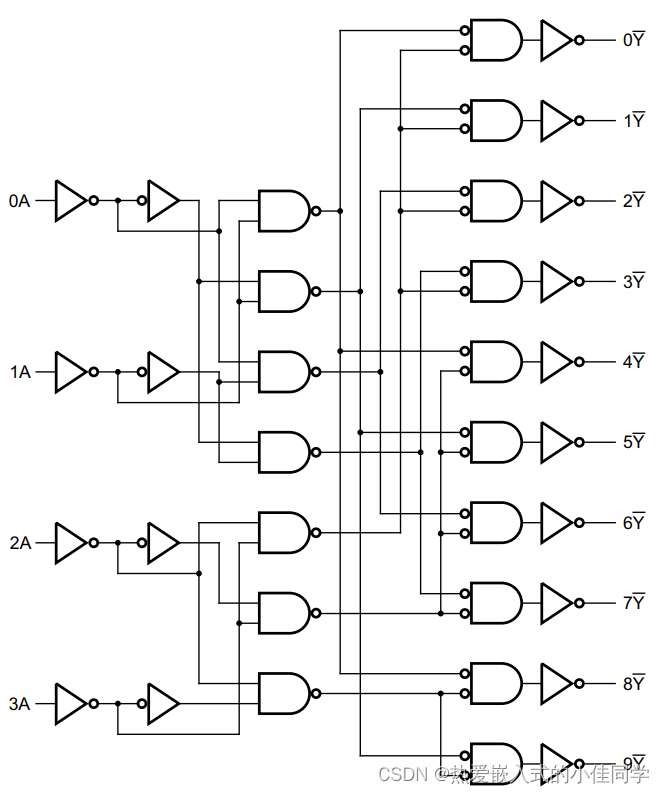

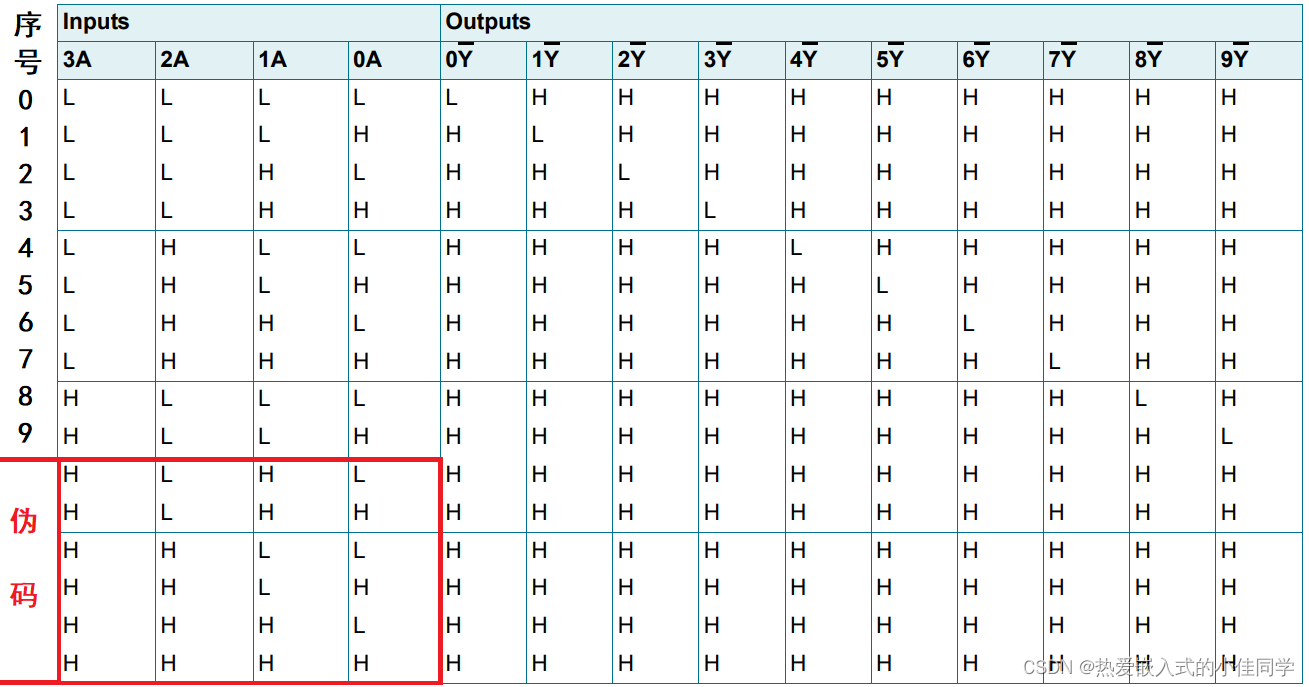

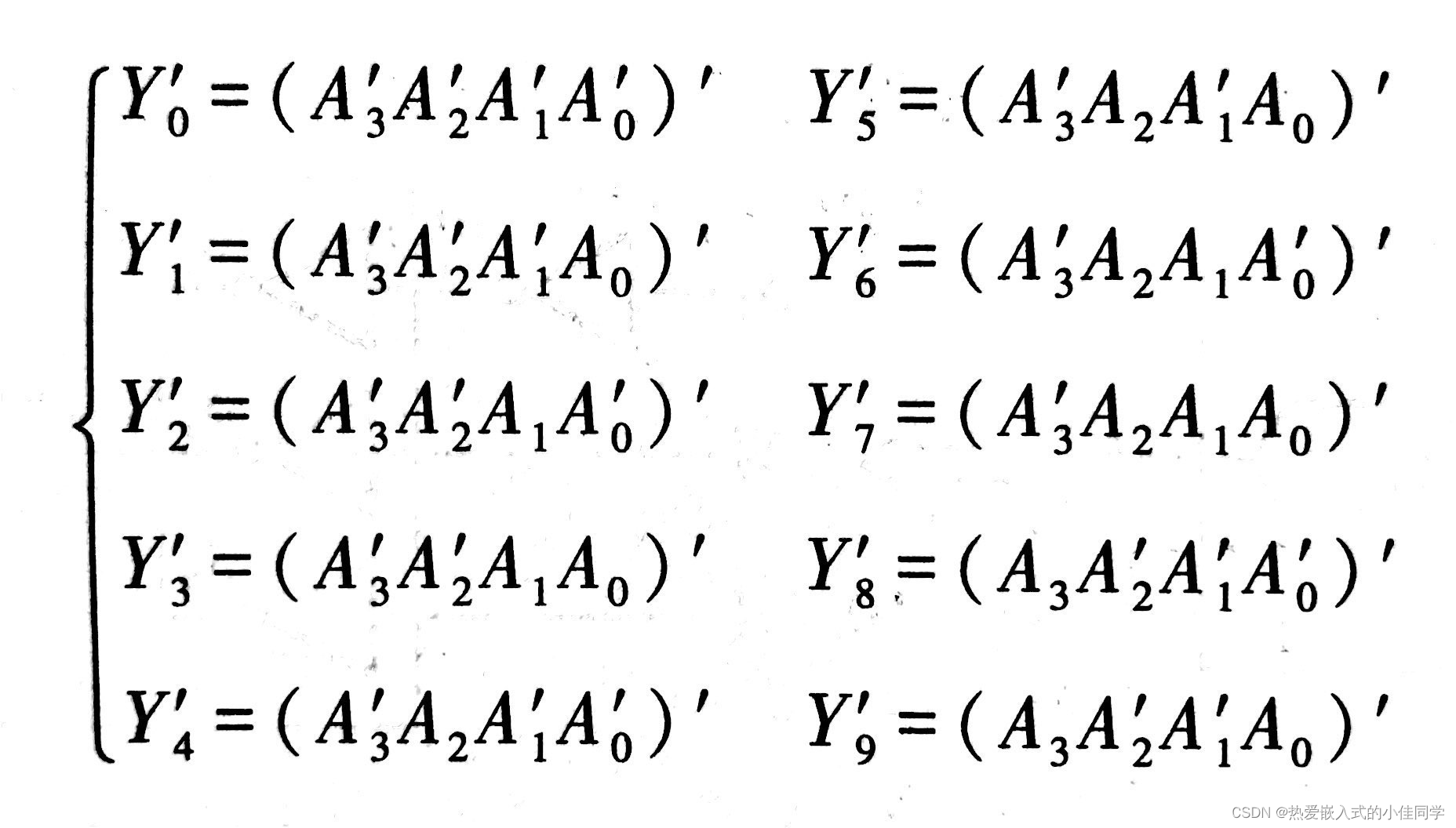

将输入BCD码的10个代码译成10个高、低电平输出信号。

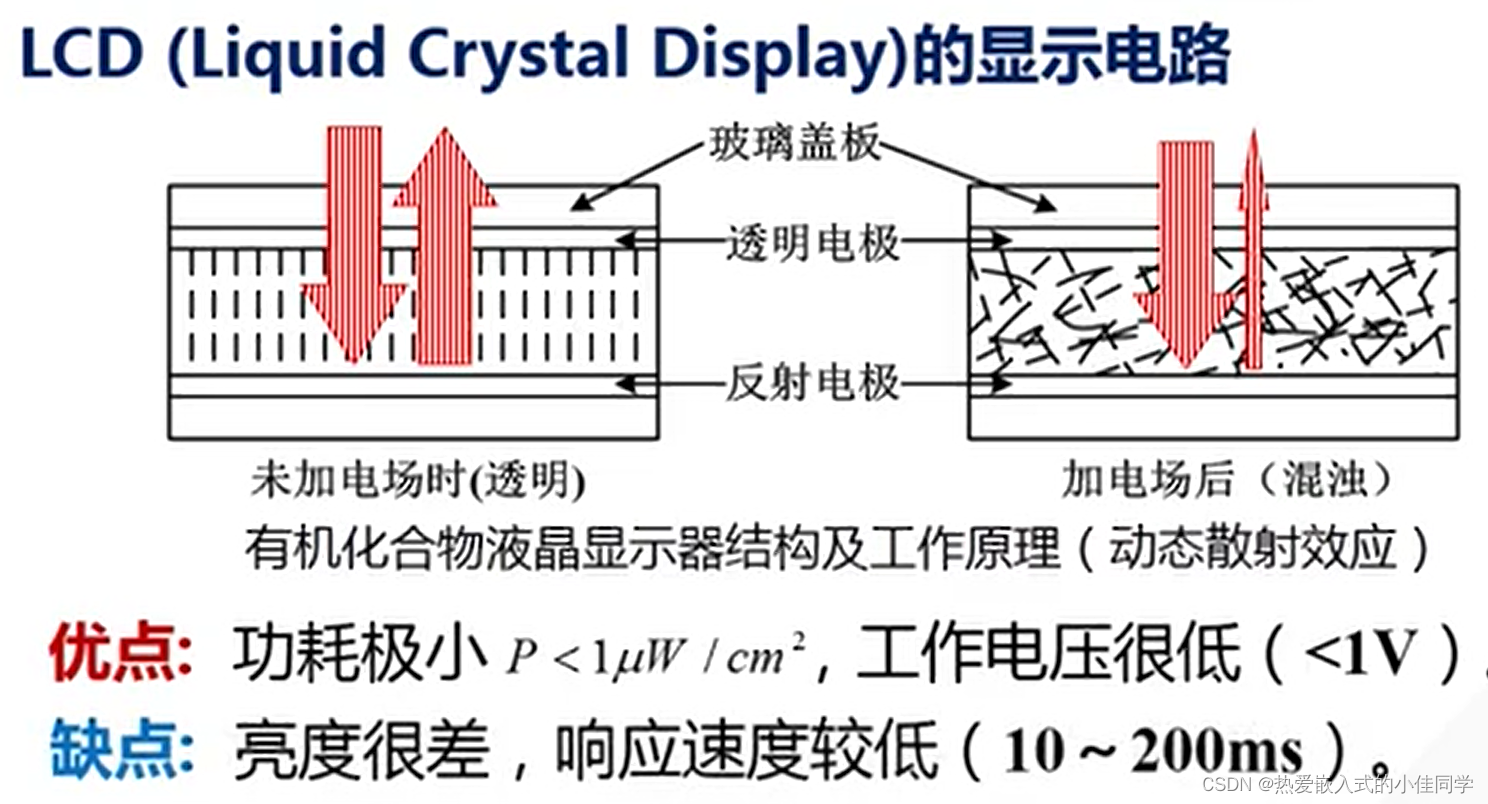

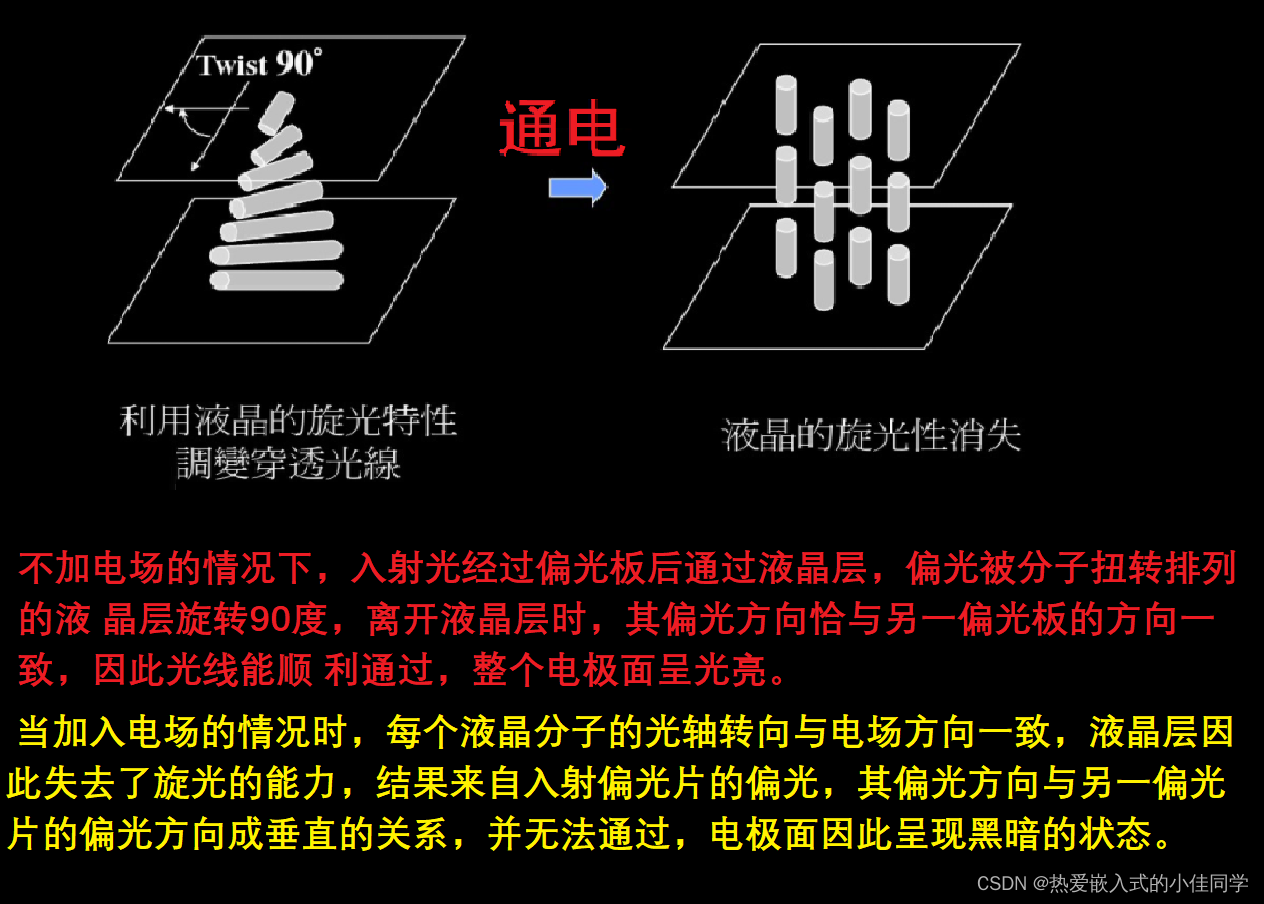

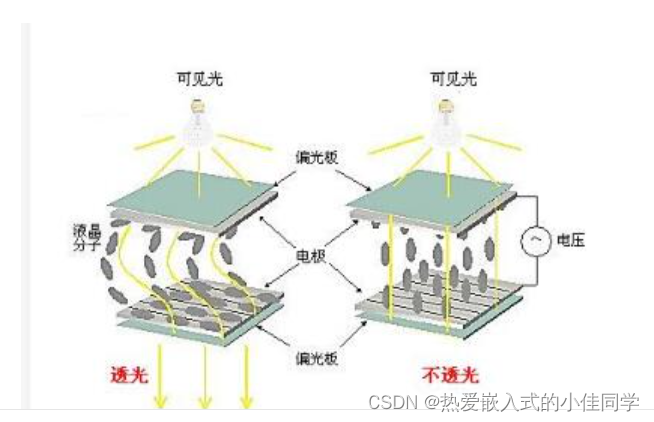

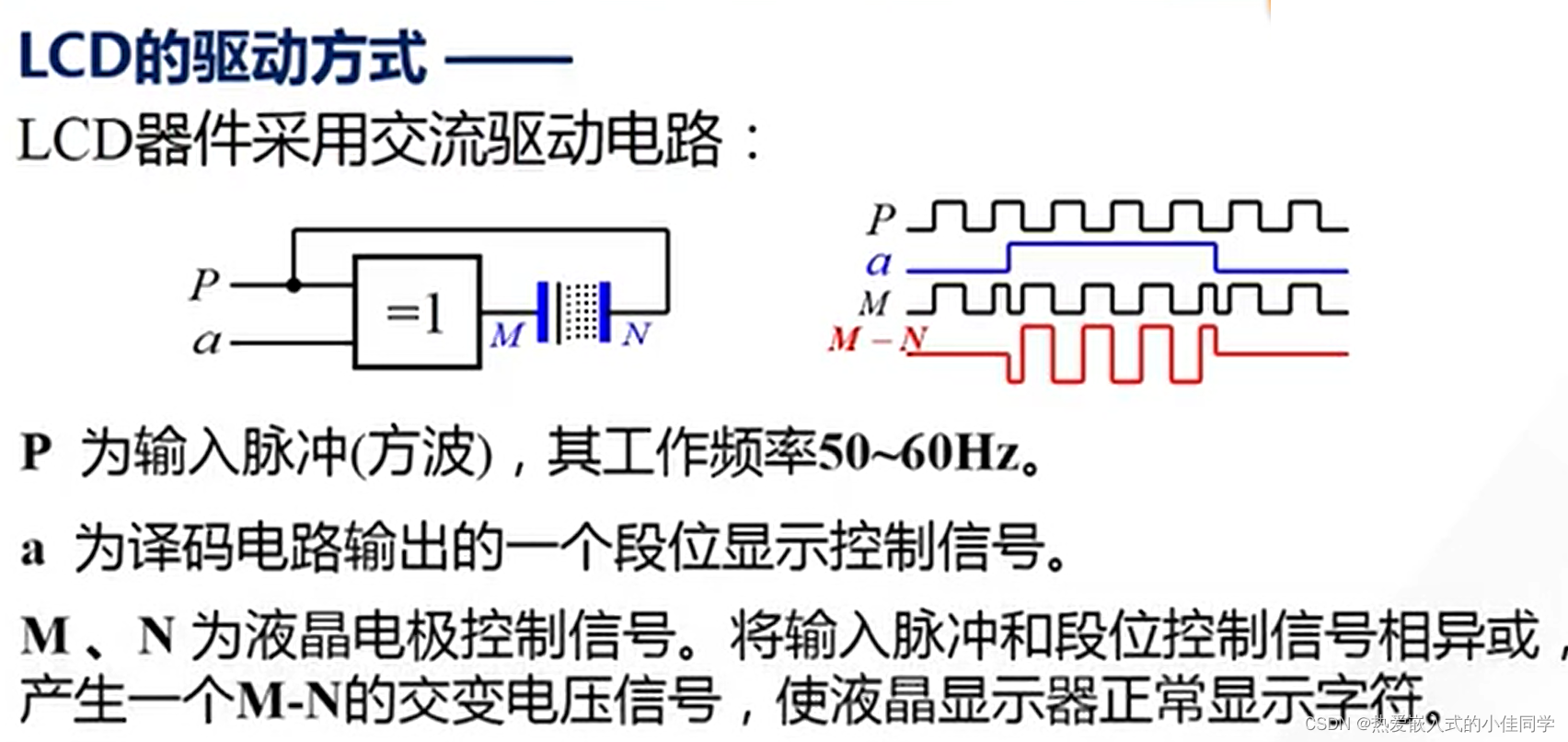

在电极上加上电压以后,液晶分子因电离而产生正离子,这些正离子在电场作用下运动 并碰撞其他液晶分子,破坏了液晶分子的整齐排列,使液晶呈现混浊状态。这时射入的 光线散射后仅有少量反射回来,故显示器呈暗灰色。这种现象称为动态散射效应。

显示模式 全透:光源来在液晶背后。半透:介于二者之间,既有来自液晶后方的光线也有反射的前方光线。反射:光源来自液晶的前方,被液晶屏的偏光片反射到观察者眼睛。

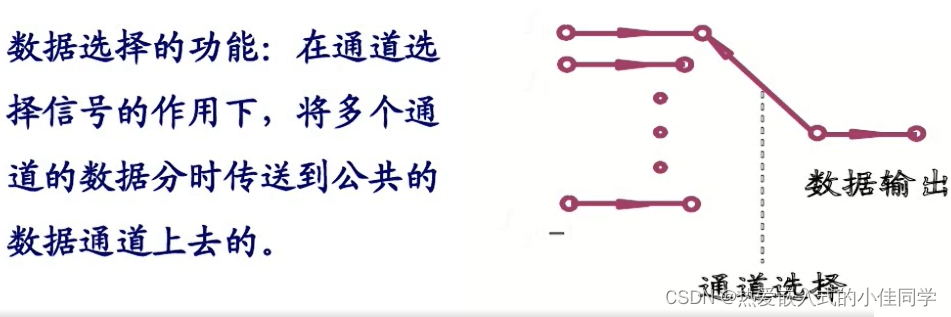

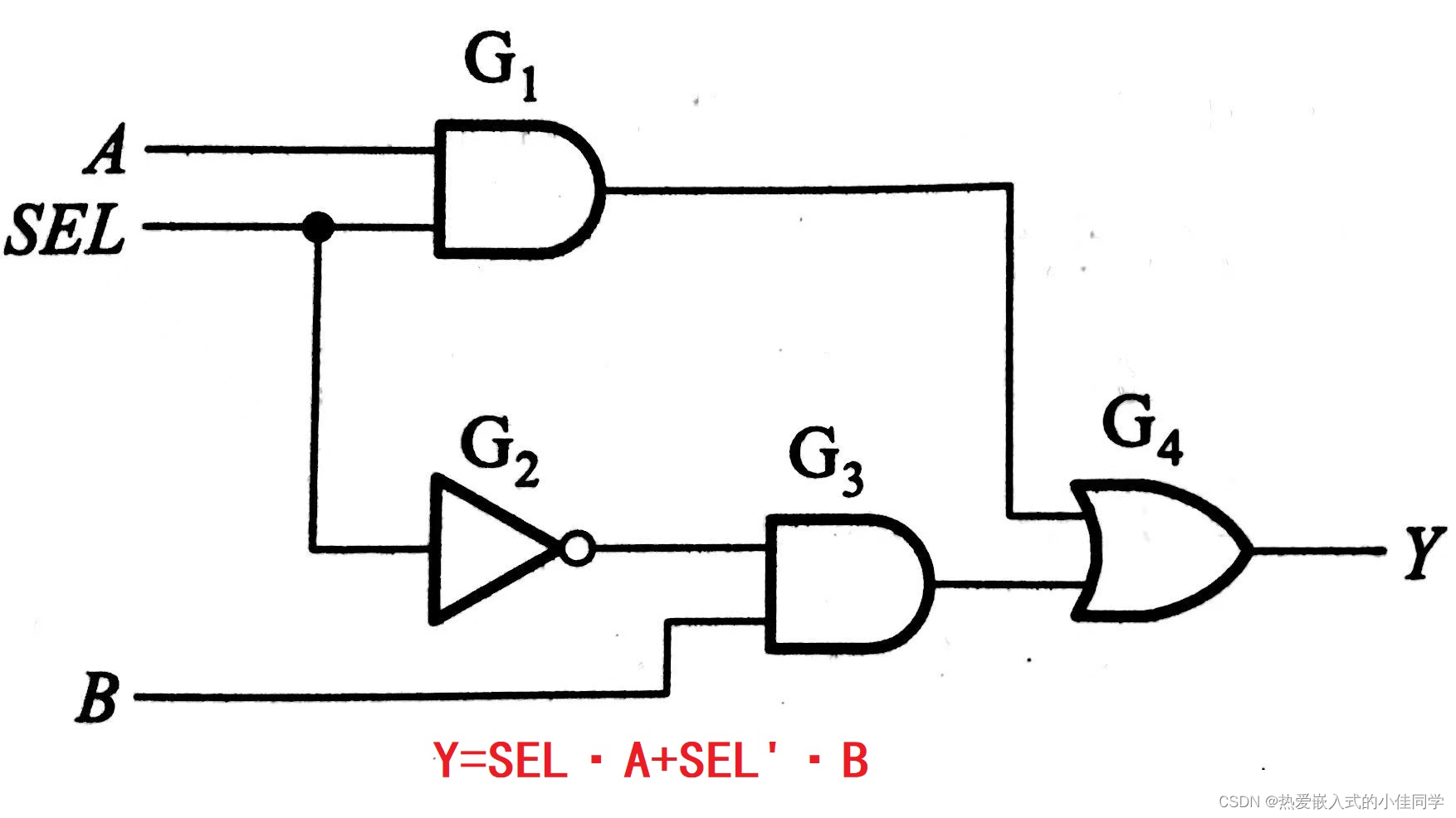

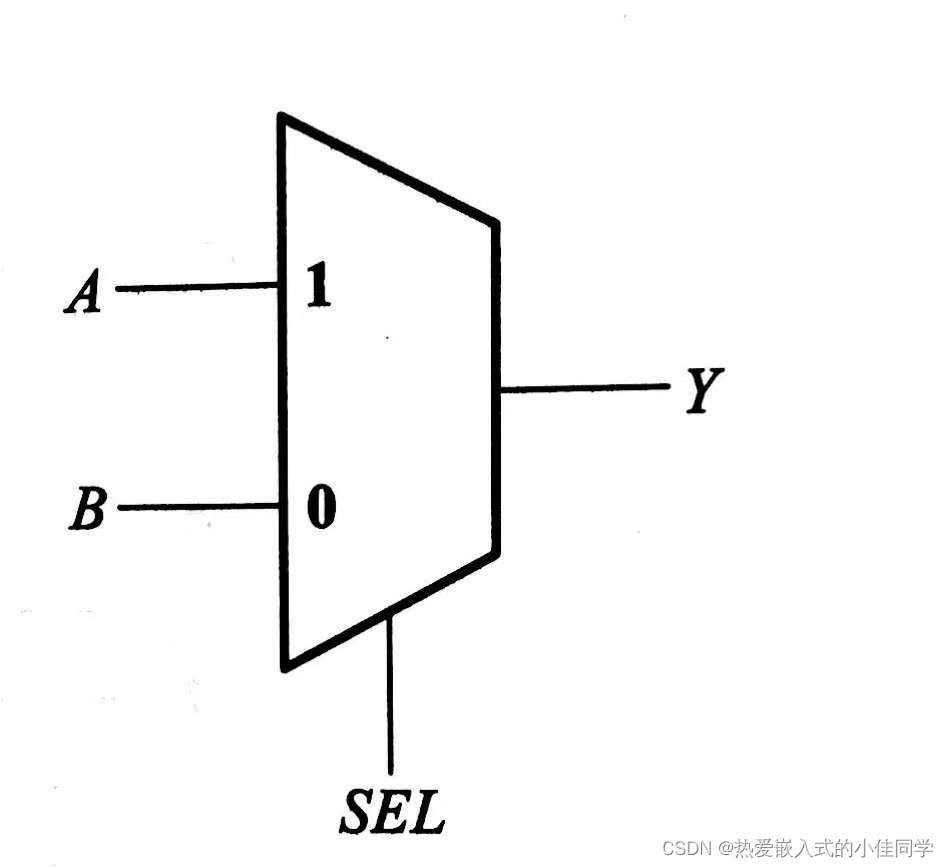

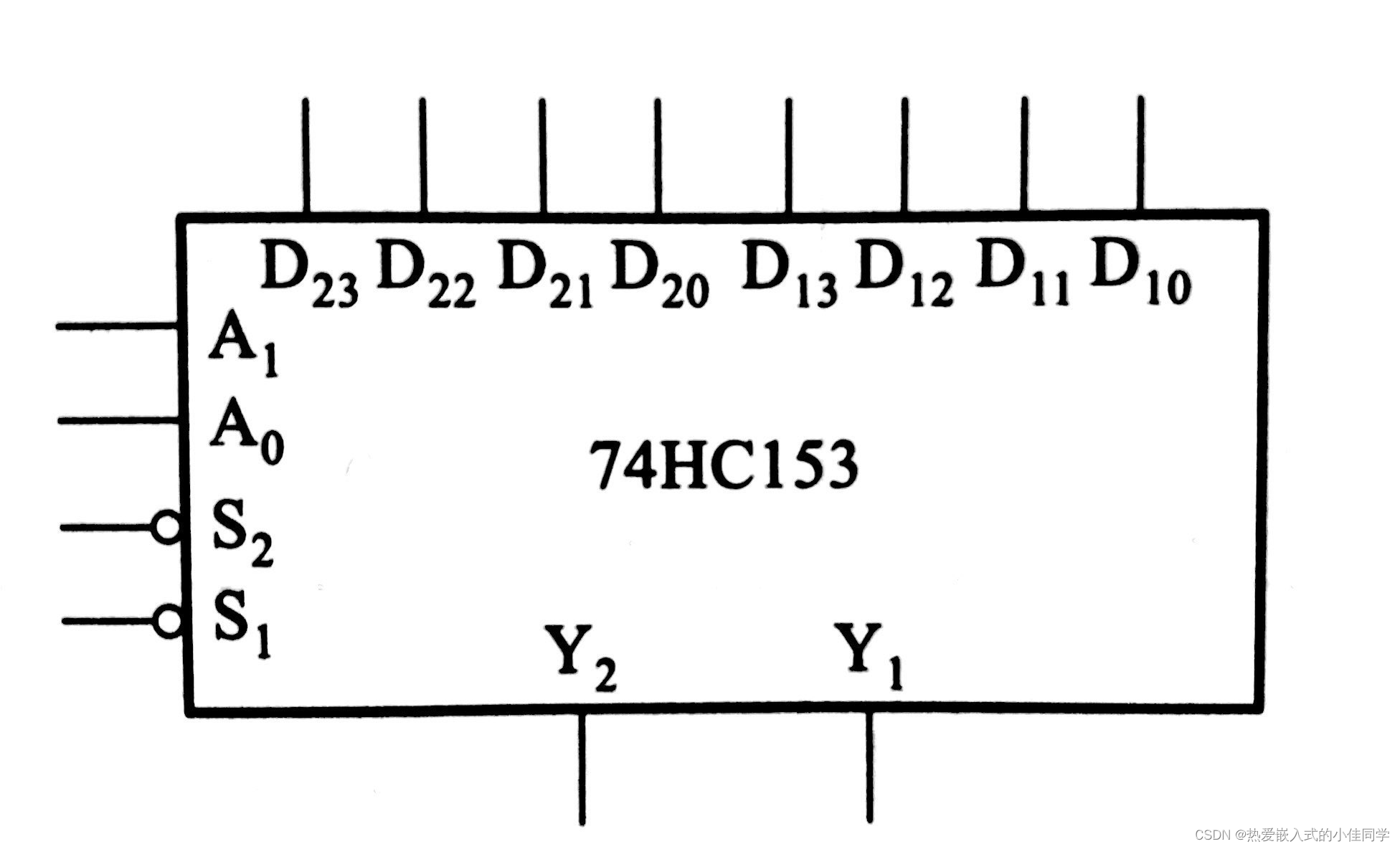

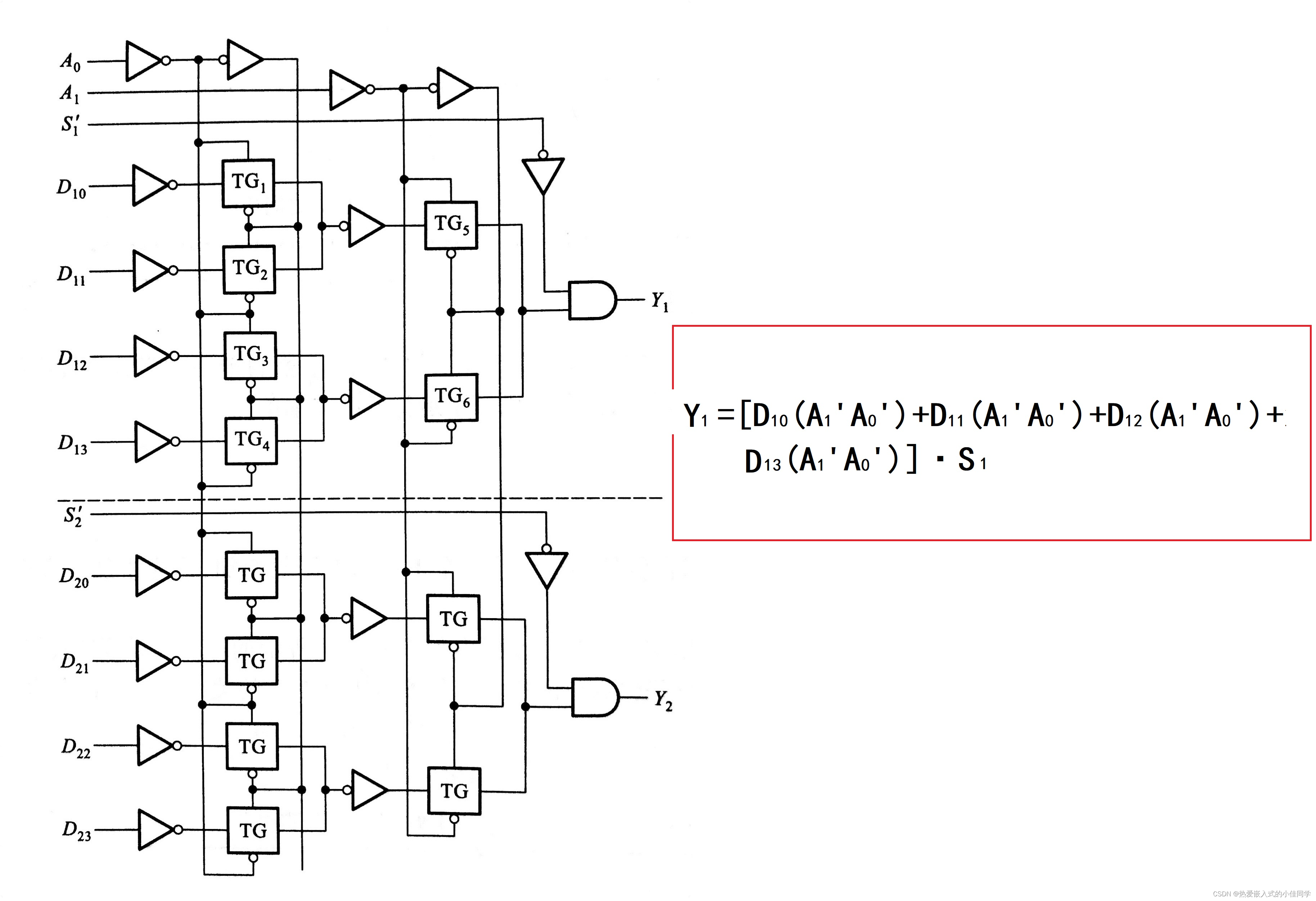

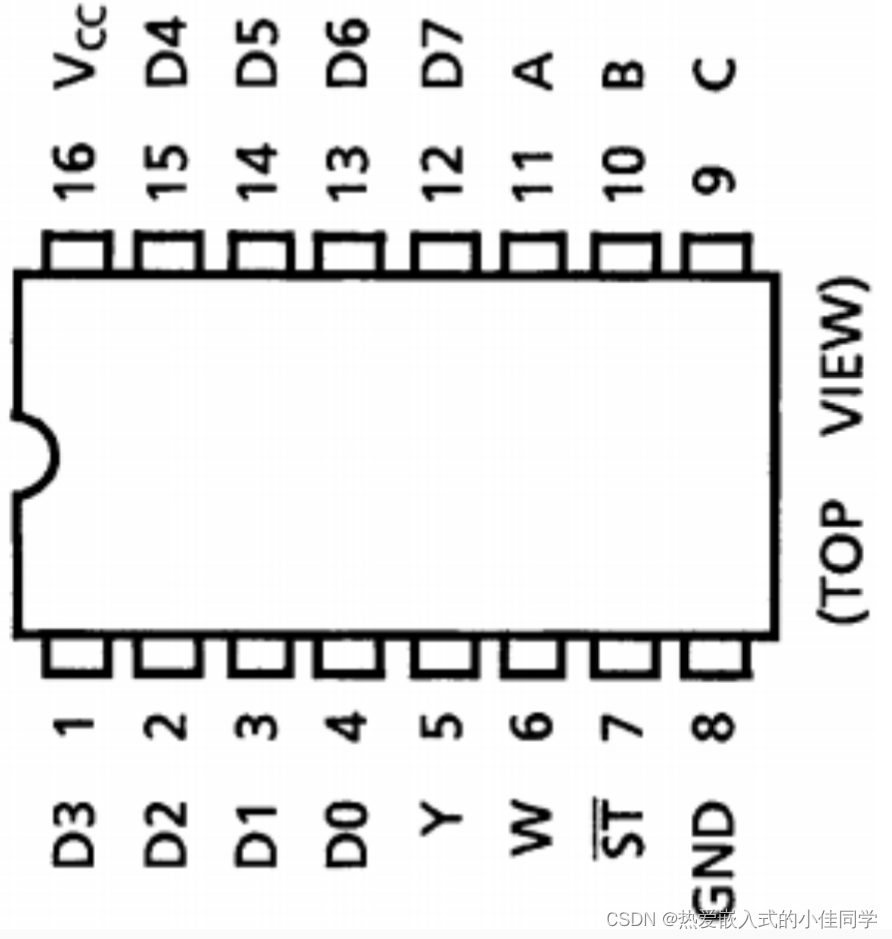

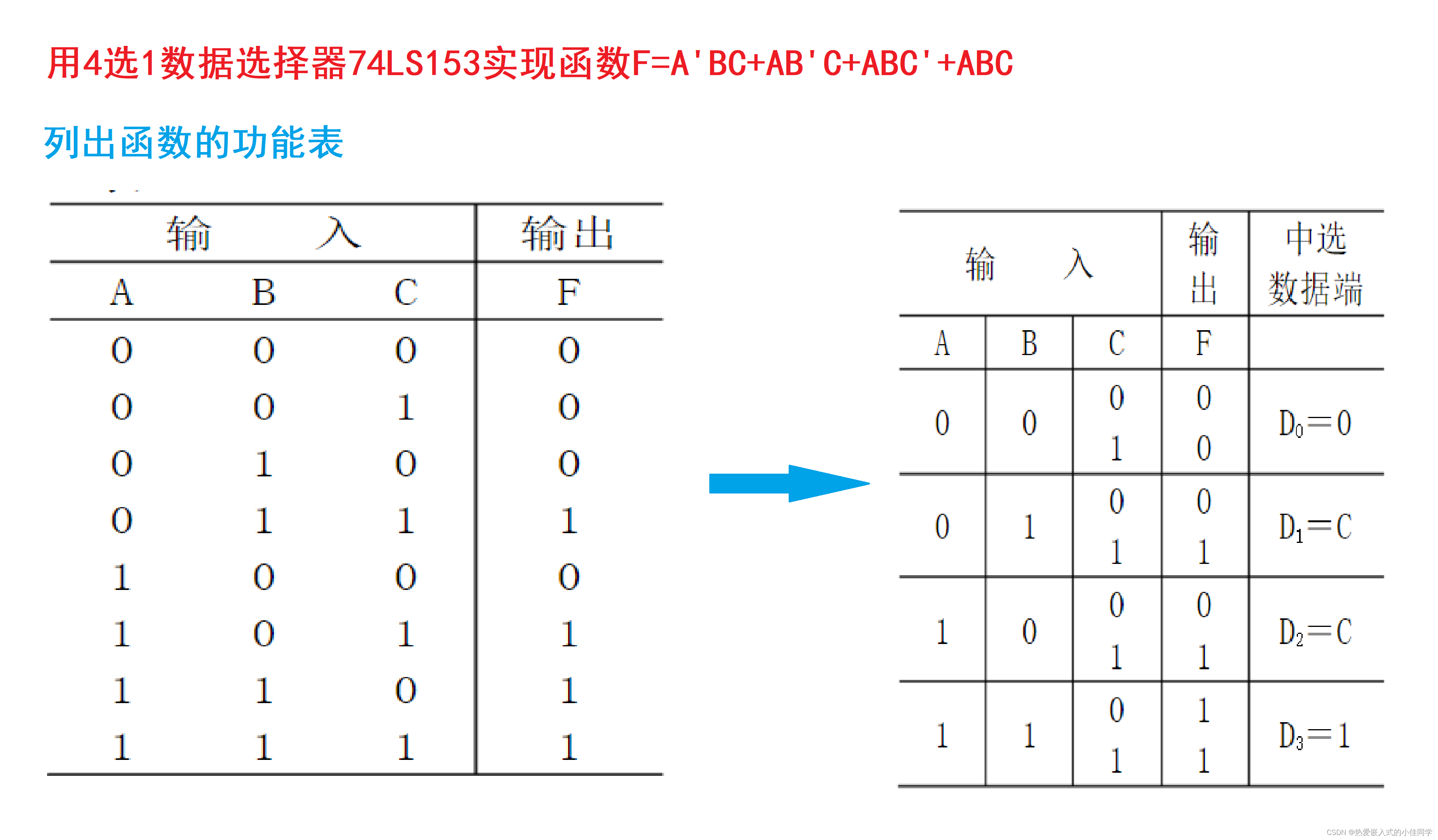

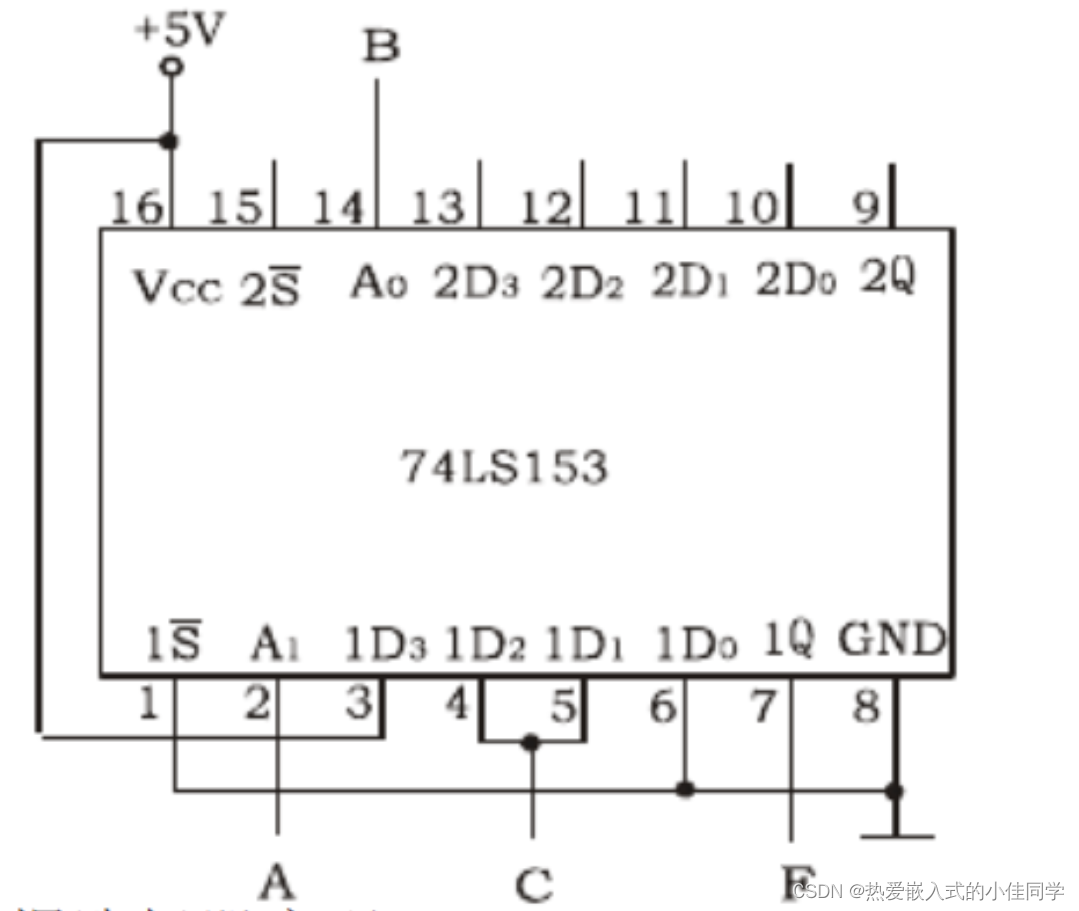

能实现数据选择功能的逻辑电路,它的作用相当于多个输入的单刀多掷开关, 又称”多路开关(Multiplexer,简称MUX)“

应用:实现逻辑函数

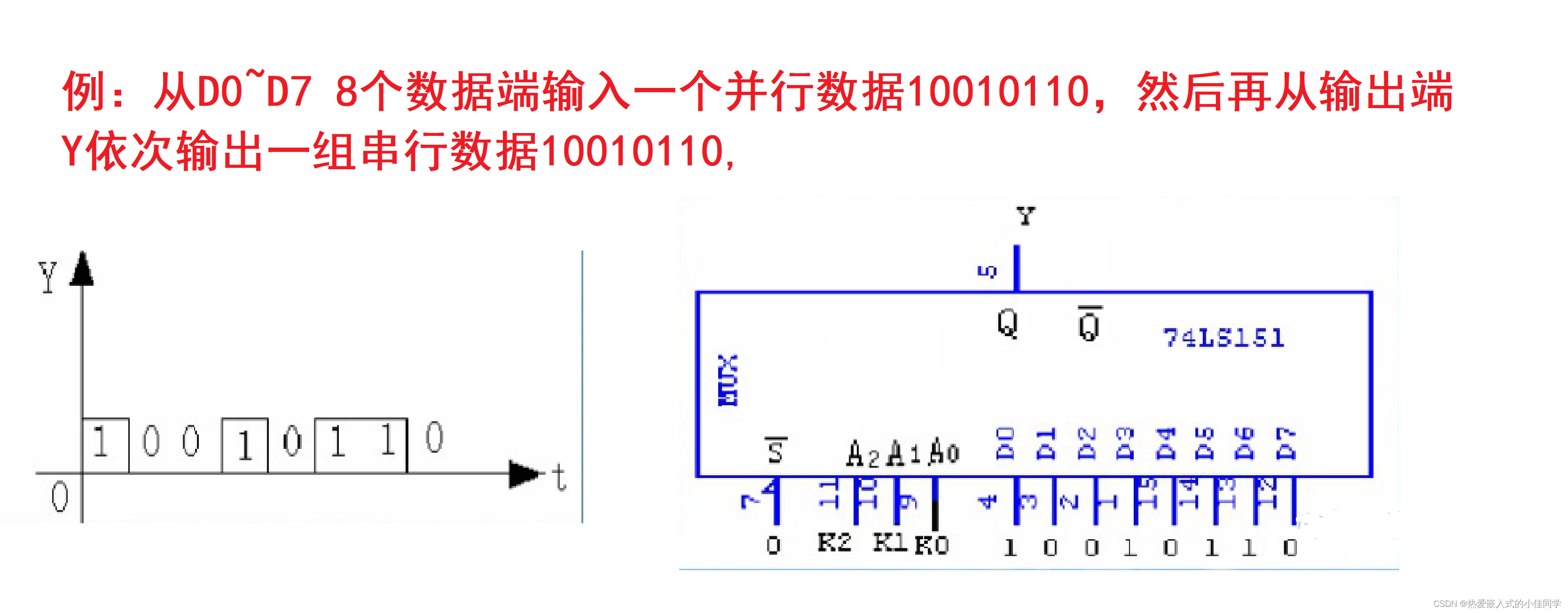

实现并行数据到串行数据的转换:

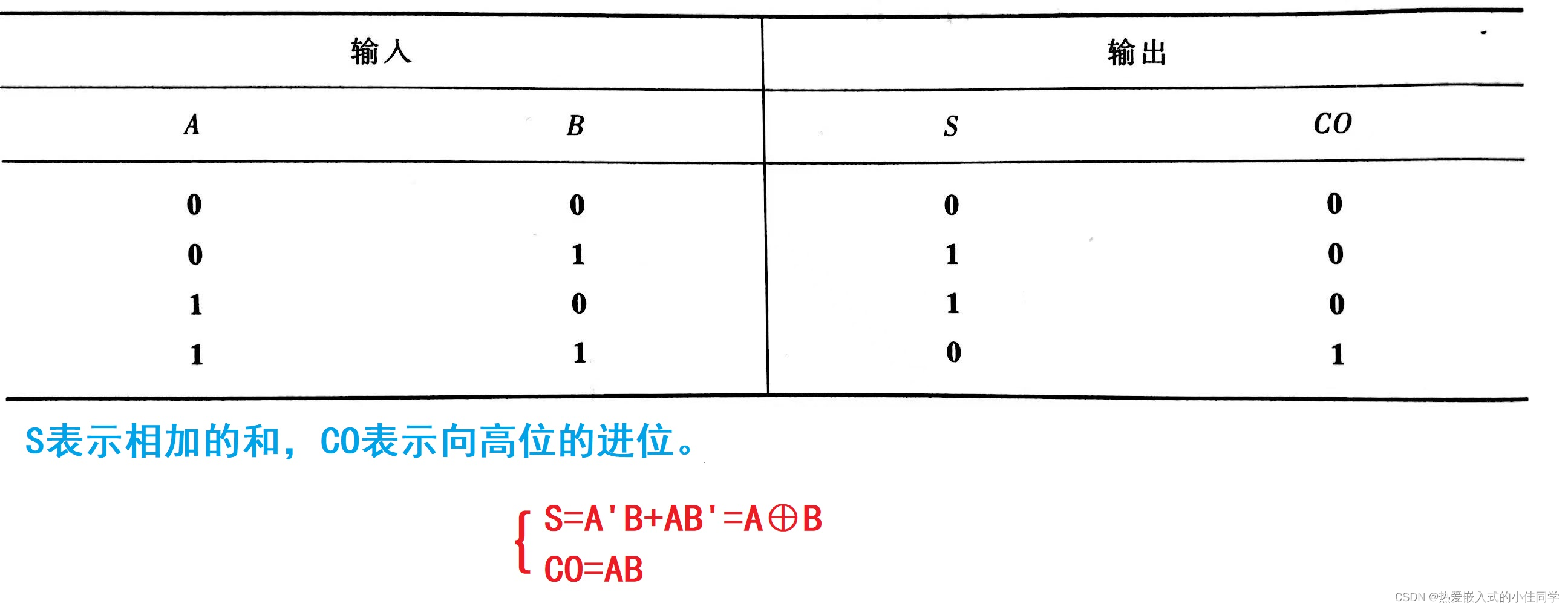

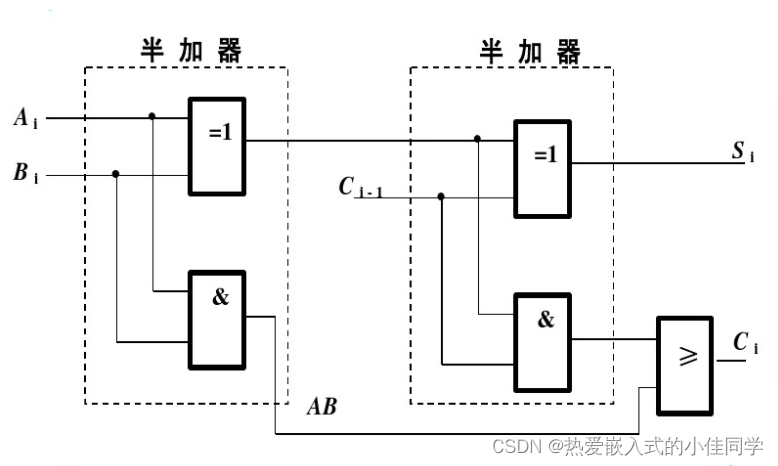

两个二进制数之间的算术运算无论是加、减、乘、除,目前在数字计算机中都是化作若干步加法运算进行的,因此,加法器是构成算术运算器的基本单元。 1位加法器(半加器Half Adder) 如果不考虑有来自低位的进位将两个1位二进制数相加,称为半加,实现半加运算的电路称为半加器。

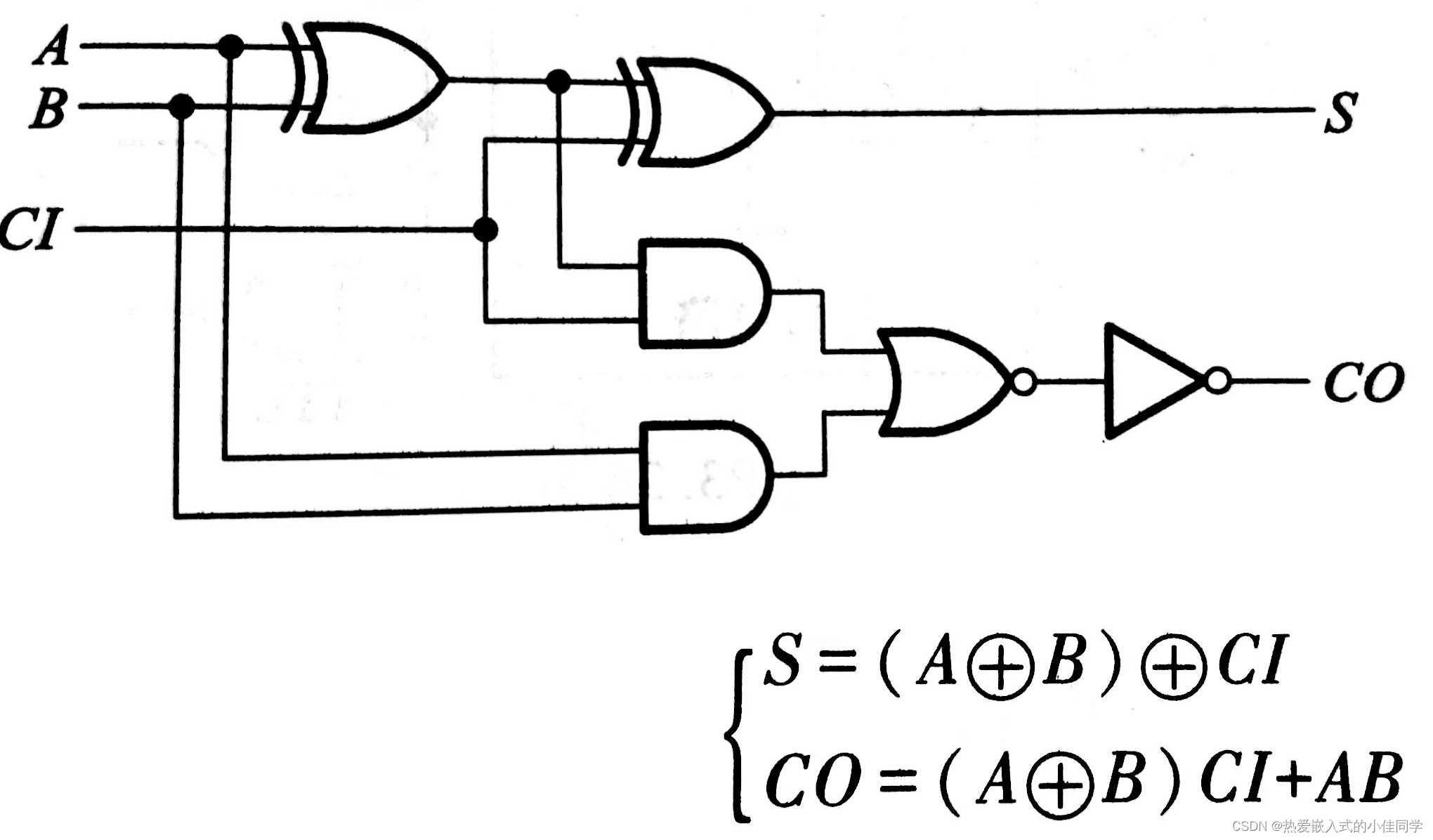

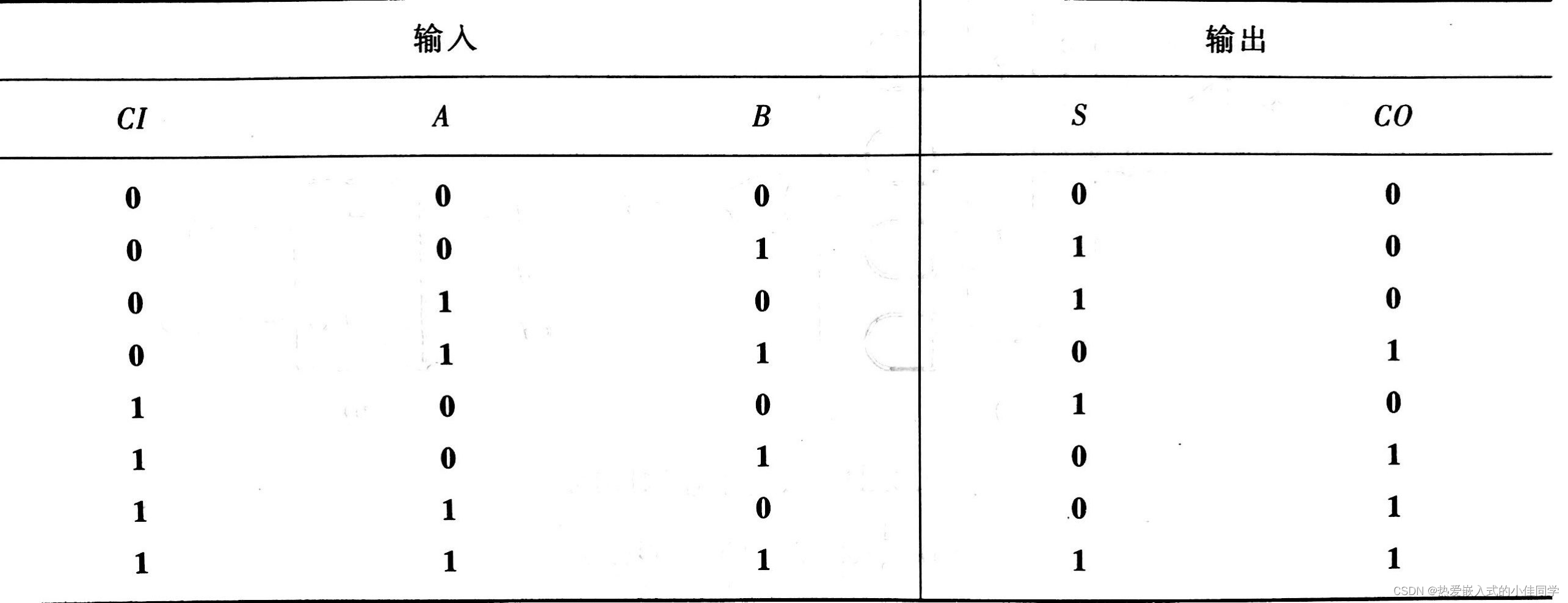

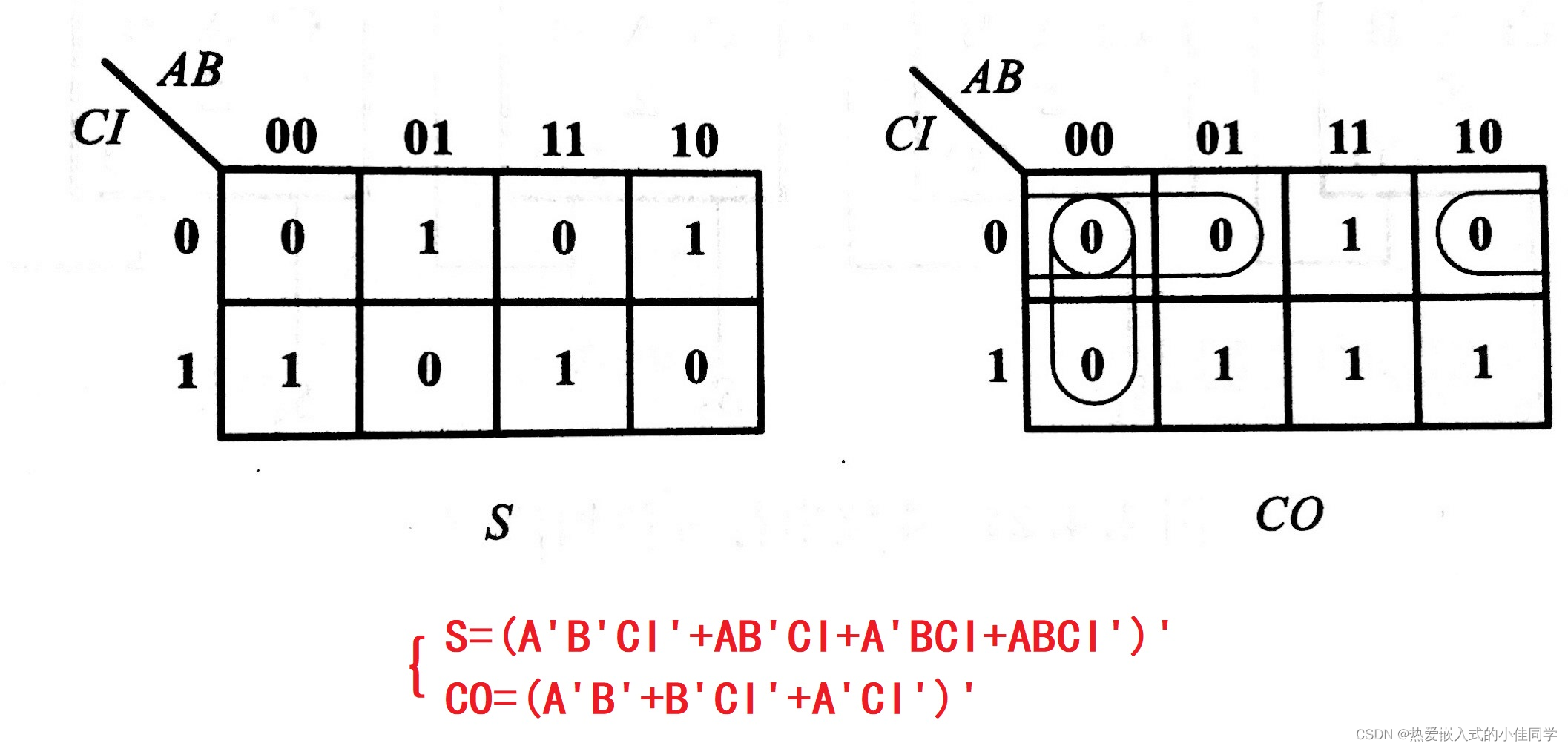

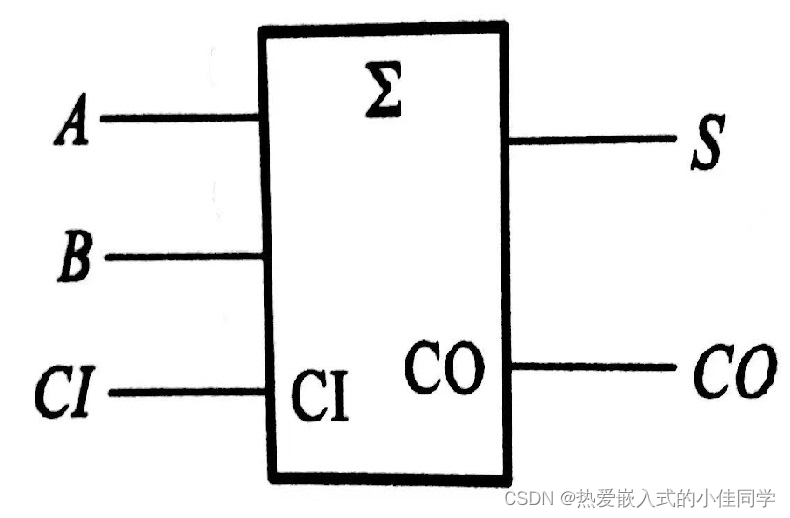

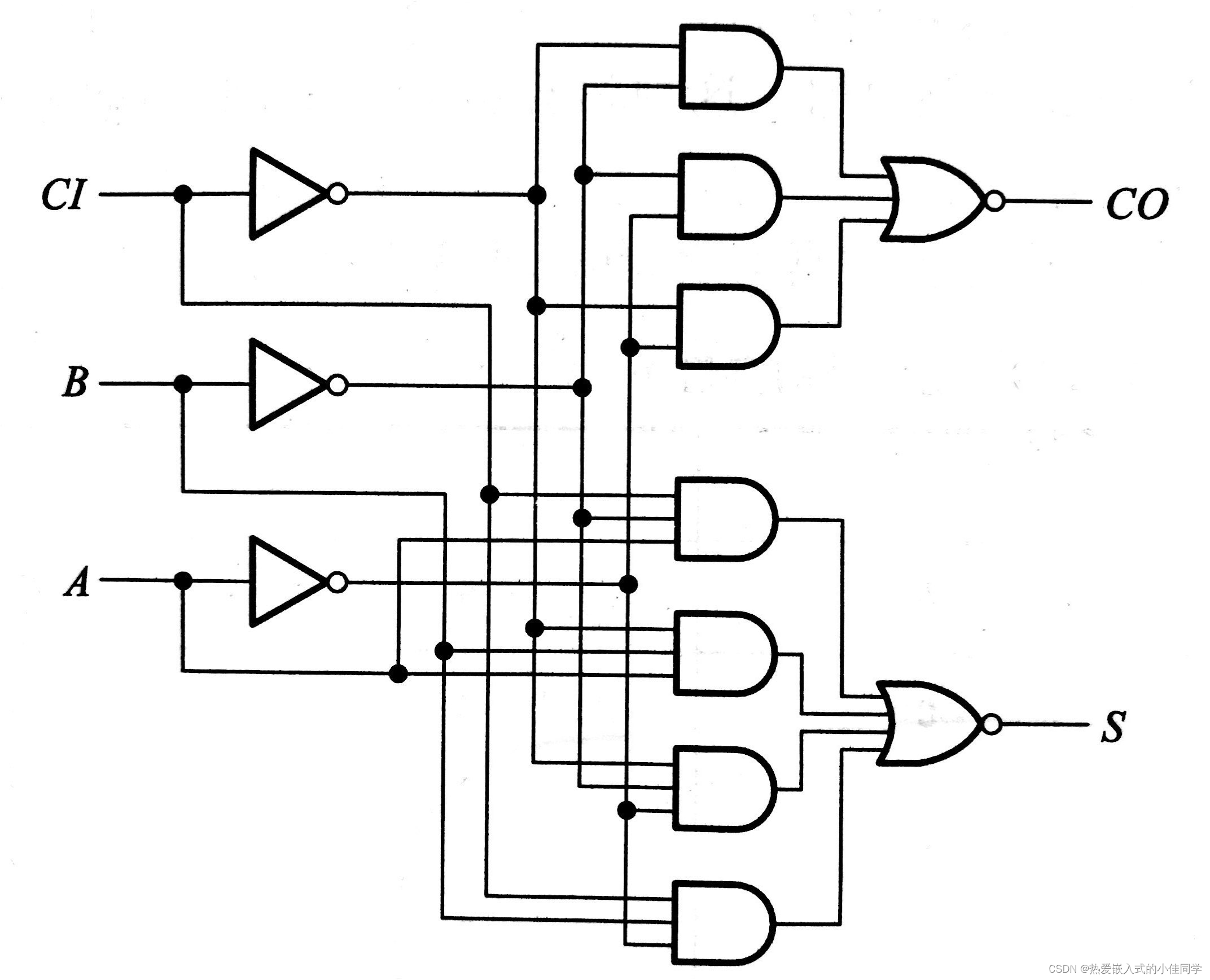

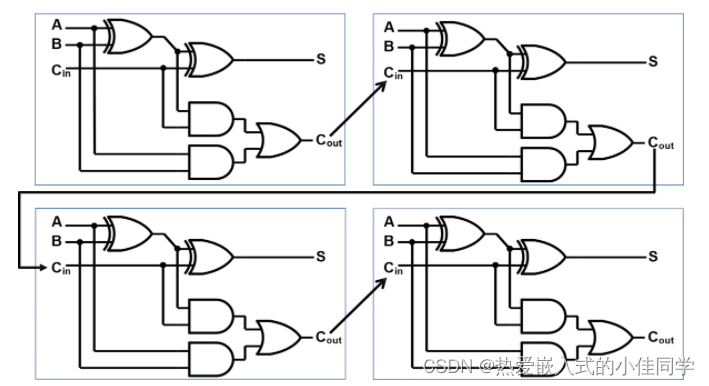

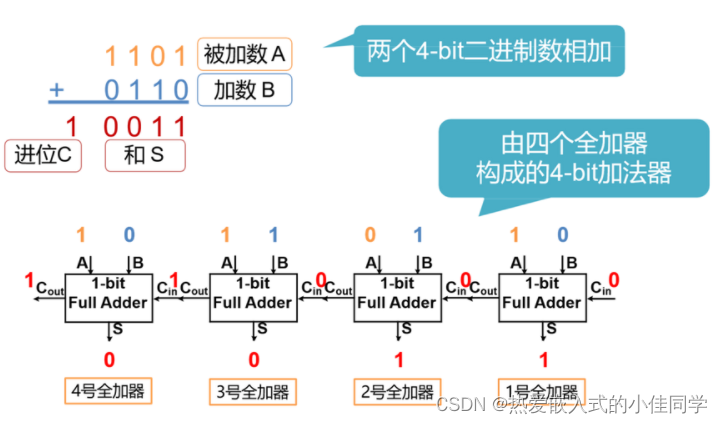

全加器(Full Adder) 在将两个多位二进制相加时,除了最低位以外,每一位都应该考虑来自低位的进位, 即将两个对应位的加数和来自低位的进位3个数相加,所用的电路称为全加电路。

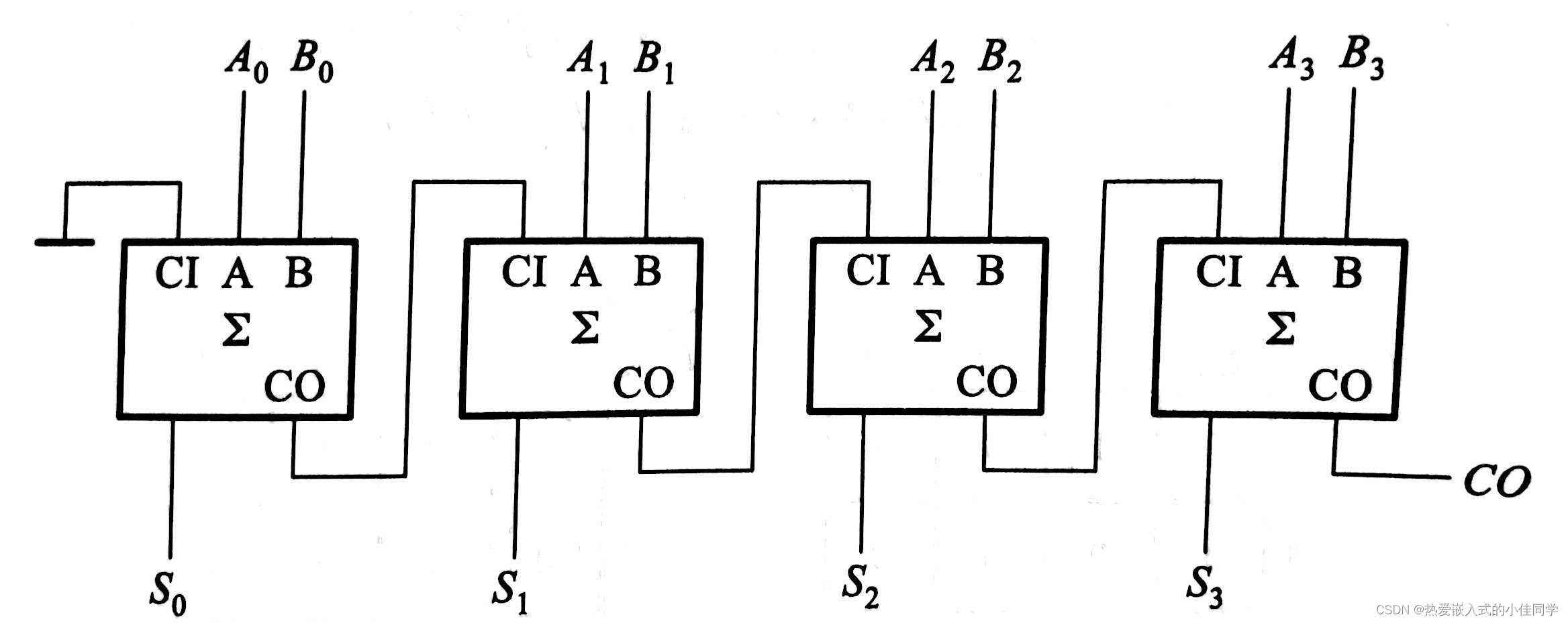

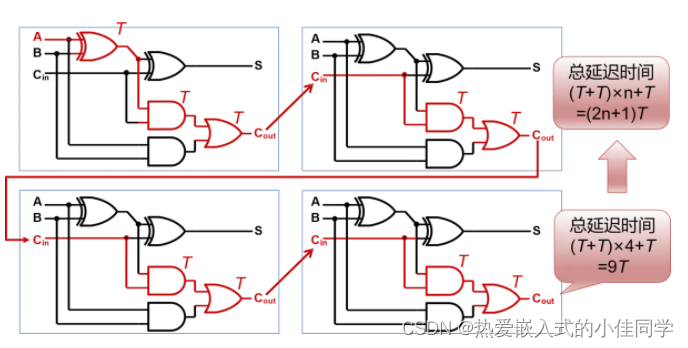

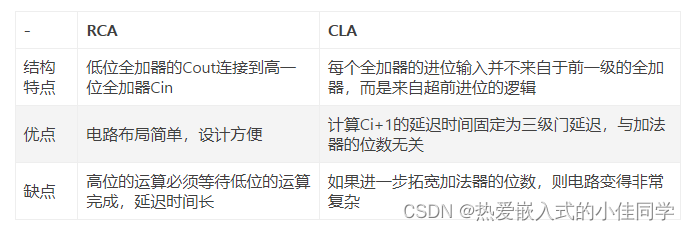

多位加法器 两个多位数相加时每一位都是带进位相加的,因而必须使用全加器,依次将低位全加器的进位输出端CO接到高位全加器的进位输入端CI得到全加器,因每一位的相加结果都必须等到低一位的进位以后才能建立,因此这种结构的电路也称为串行进位加法器(或称行波进位加法器)

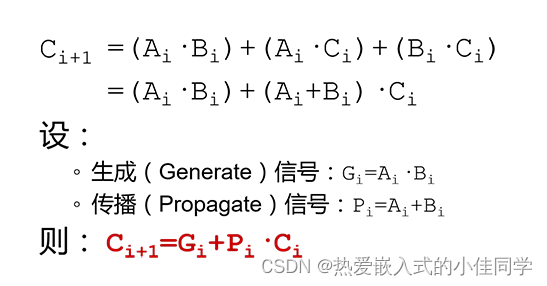

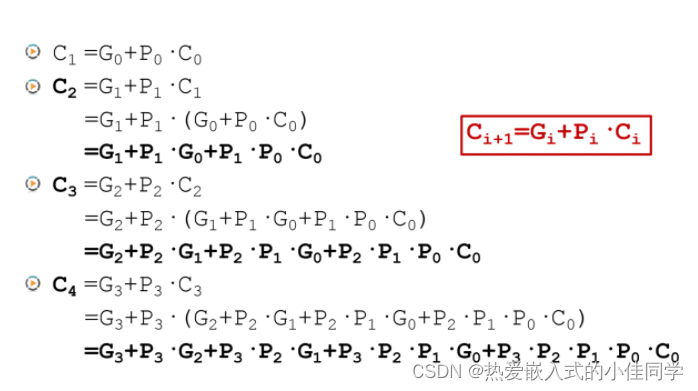

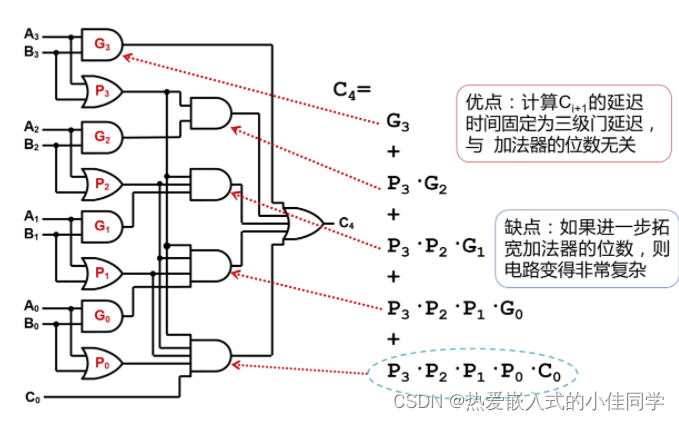

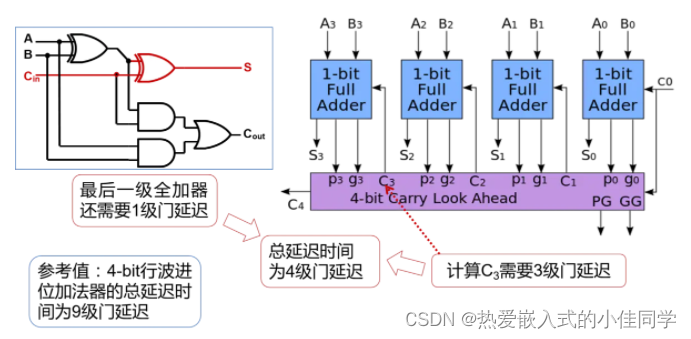

与串行进位加法器不同的是不需要等待低一位发送数据

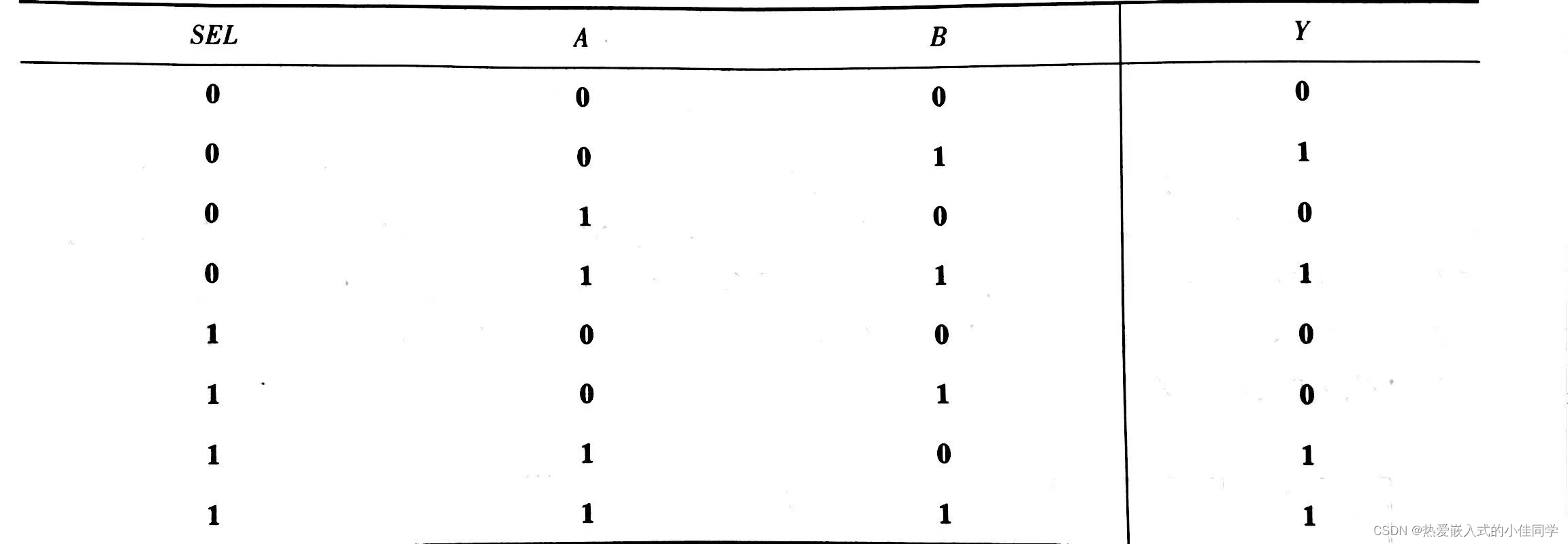

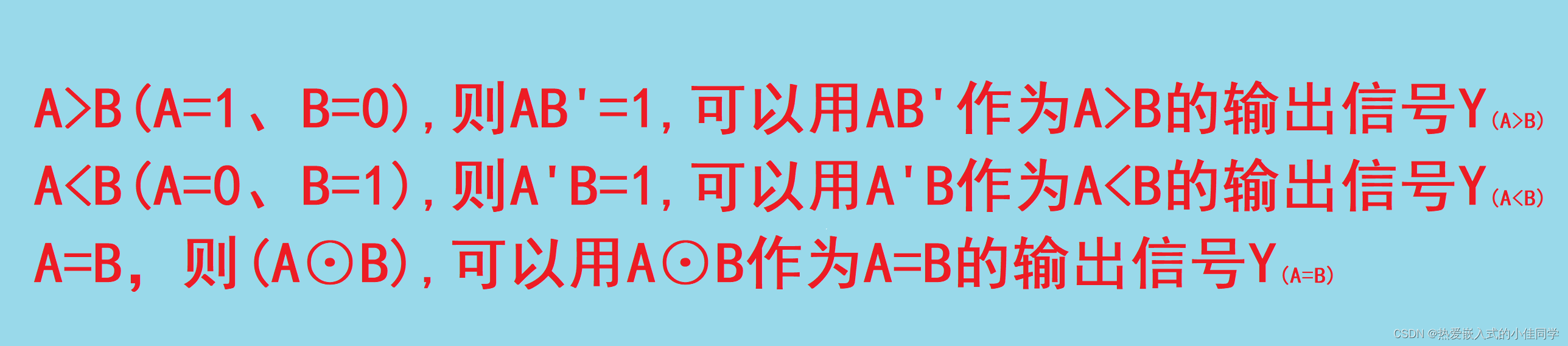

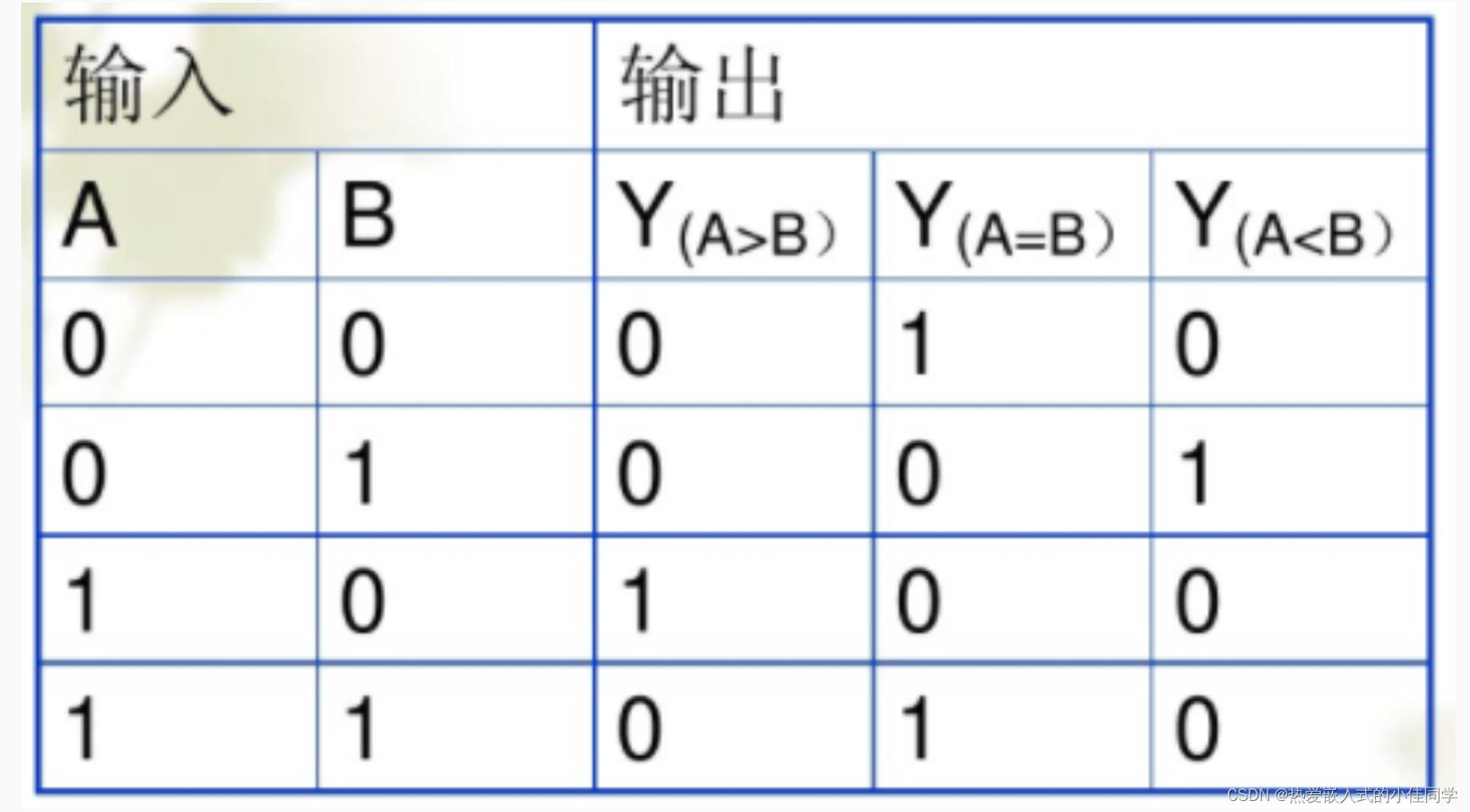

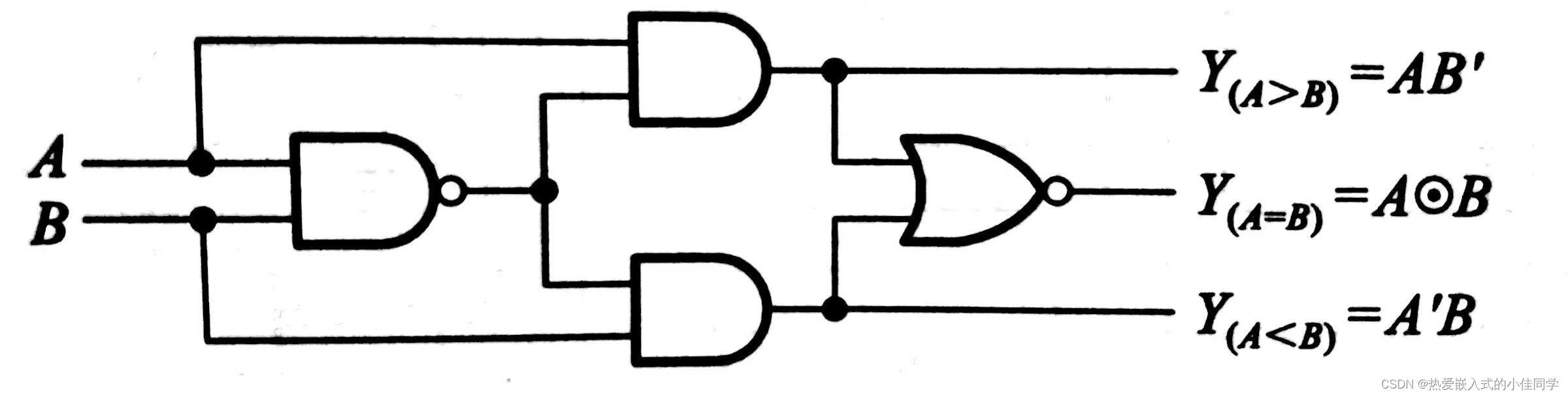

在数字电路中,经常需要对两个位数相同的二进制数进行比较,以判断它们的相对大小或者是否相等,用来实现这一功能的逻辑电路就成为数值比较器。 1.一位数值比较器

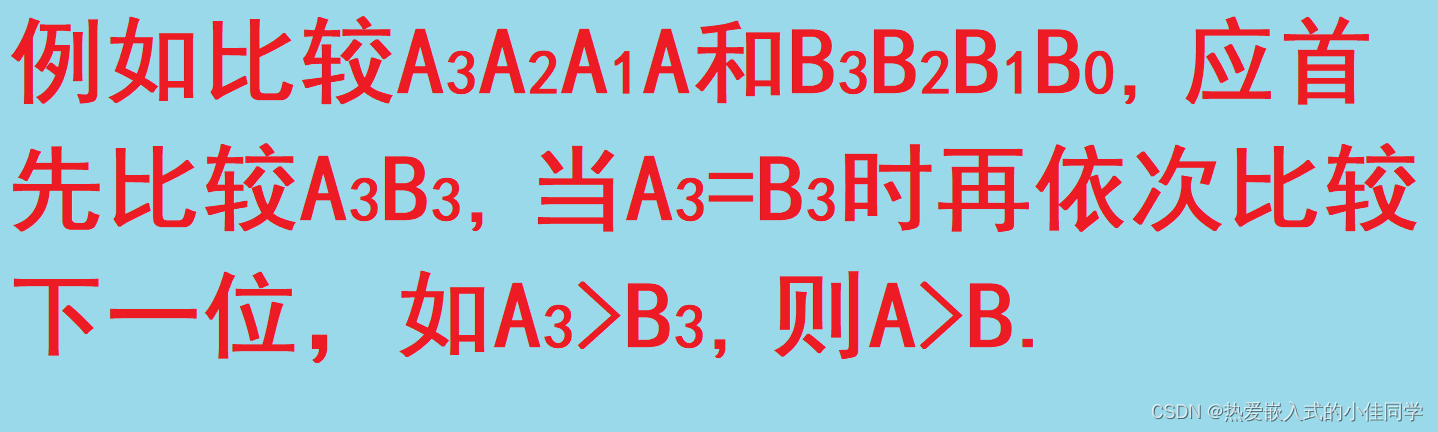

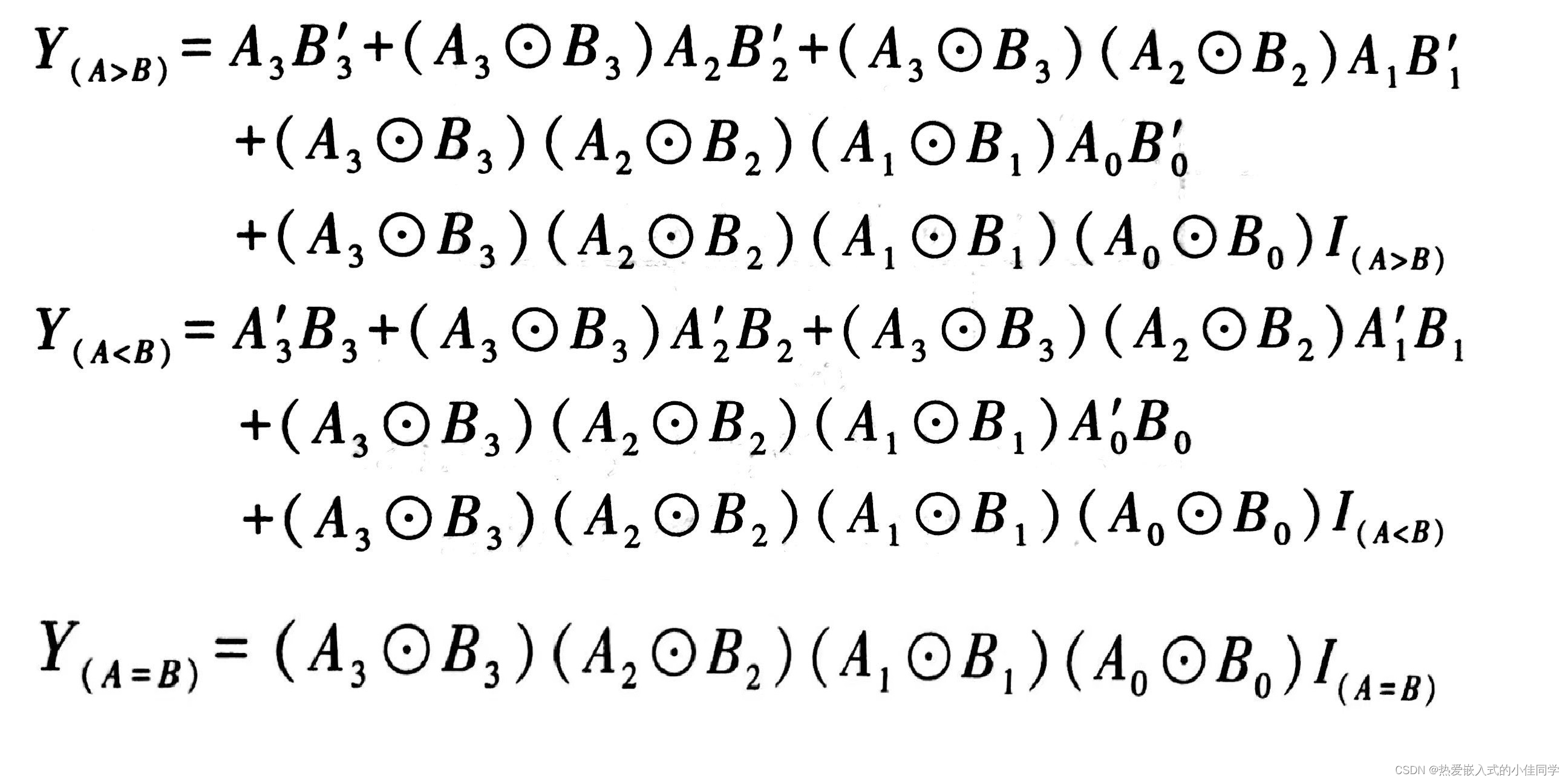

比较多位数大小时,必须自高而低的逐位比较,而且只有在高位相等时,才需要比较低位。

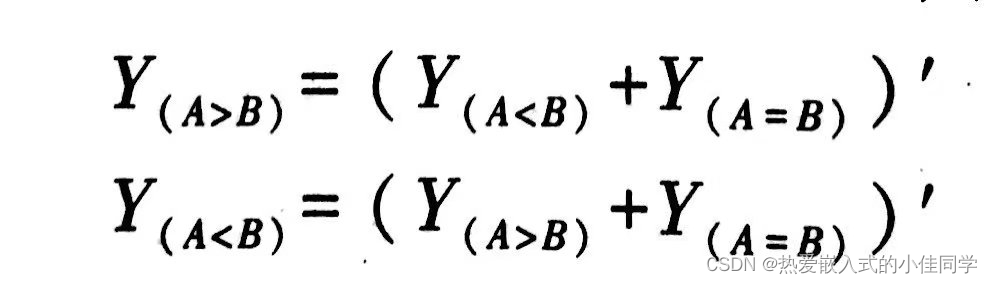

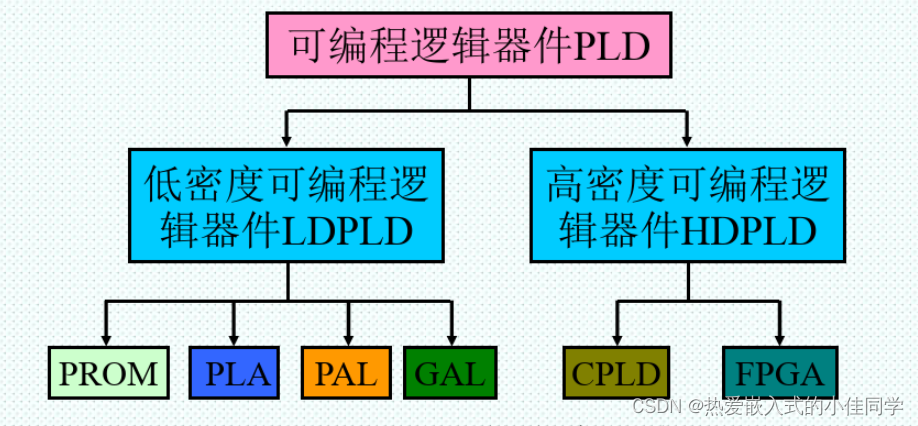

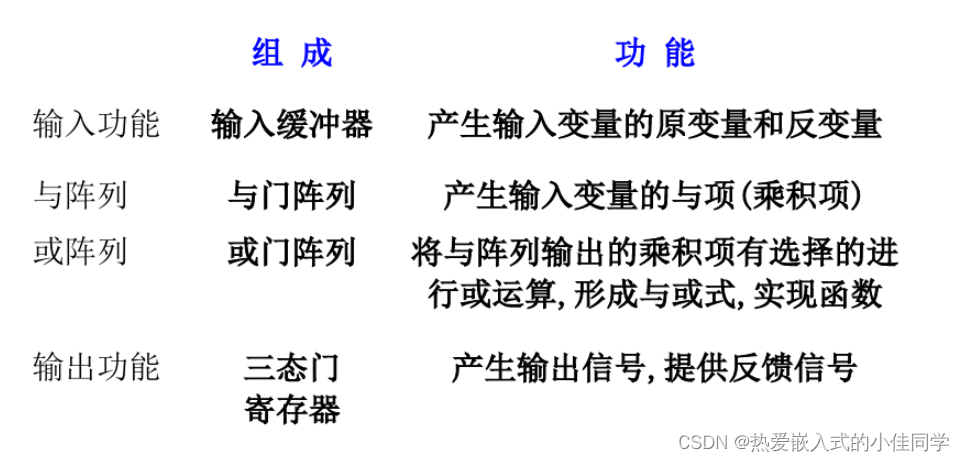

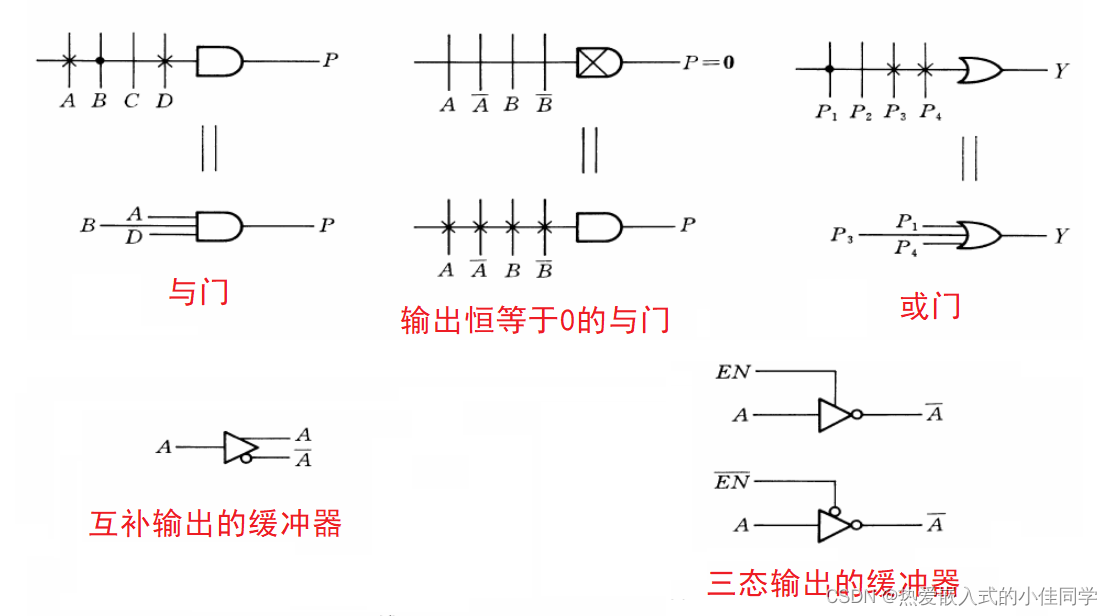

逻辑功能的特点将数字集成电路分类 通用集成电路专用集成电路ASIC(application-specific integrated circuit)可编程逻辑器件(Programmable Logic Device,简称PLD)PLD是做为一种通用集成电路产生的,他的逻辑功能按照用户对器件编程来确定

特点 提高了集成度加快了电子系统的设计速度高性能高可靠性成本低

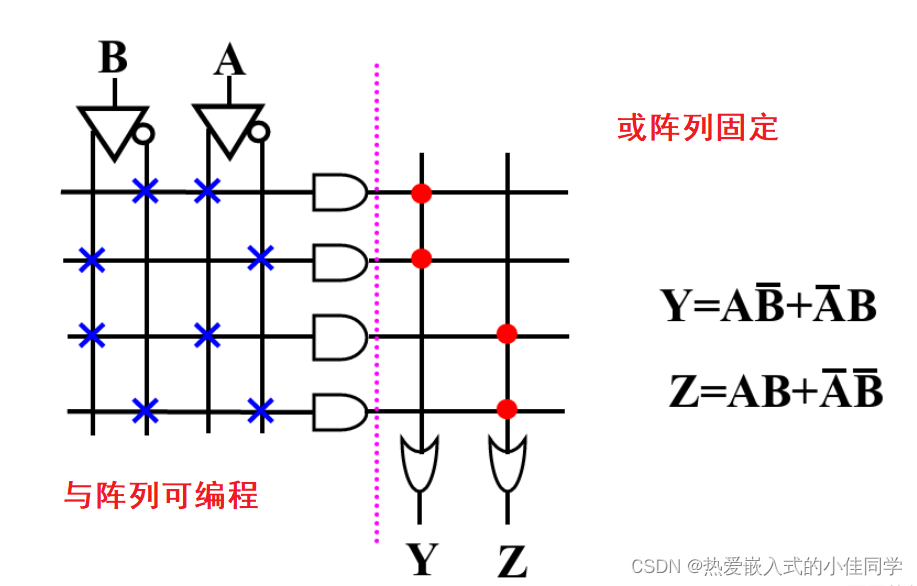

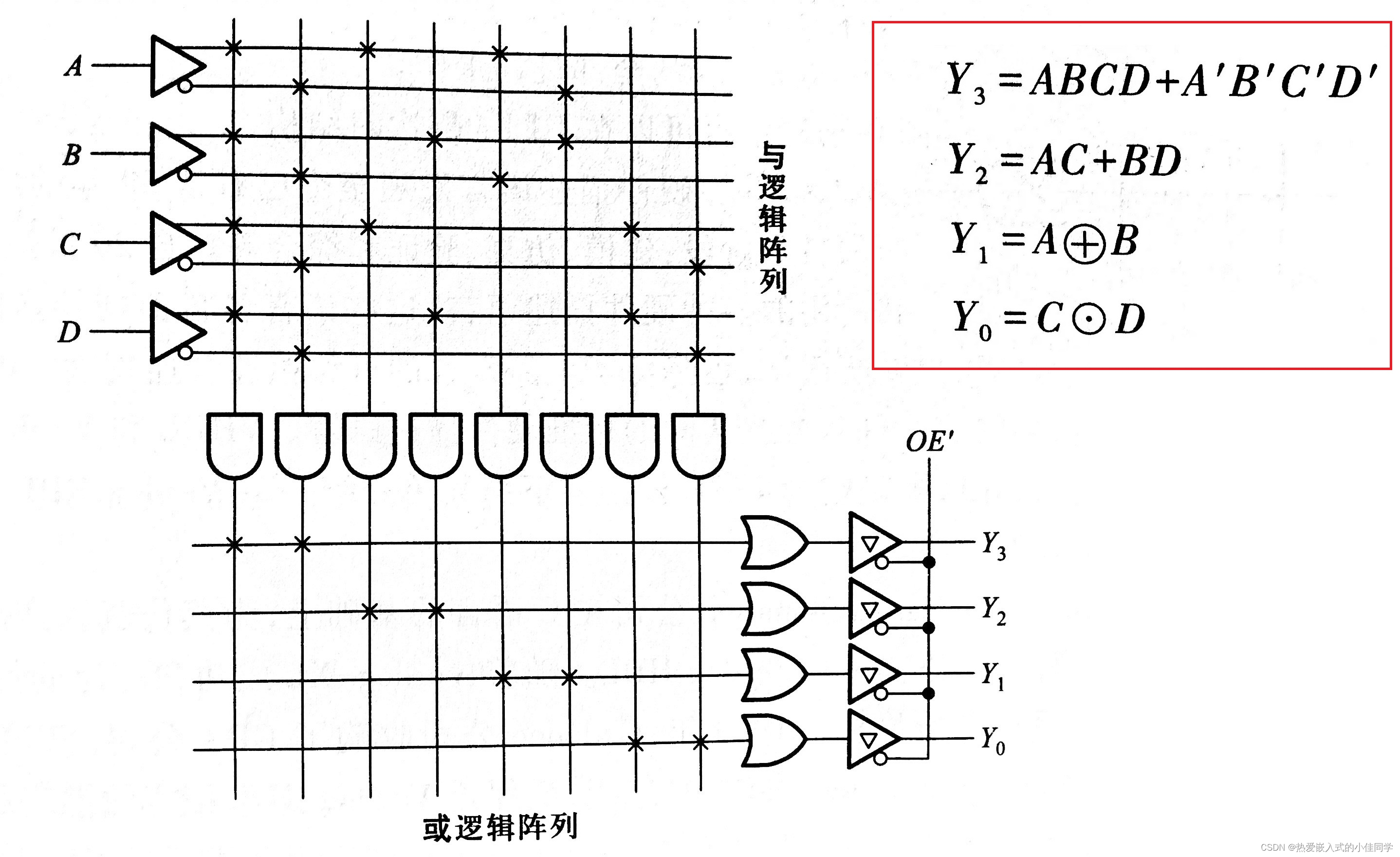

现场可编程逻辑阵列(Programmable Logic Array,简称为PLA)

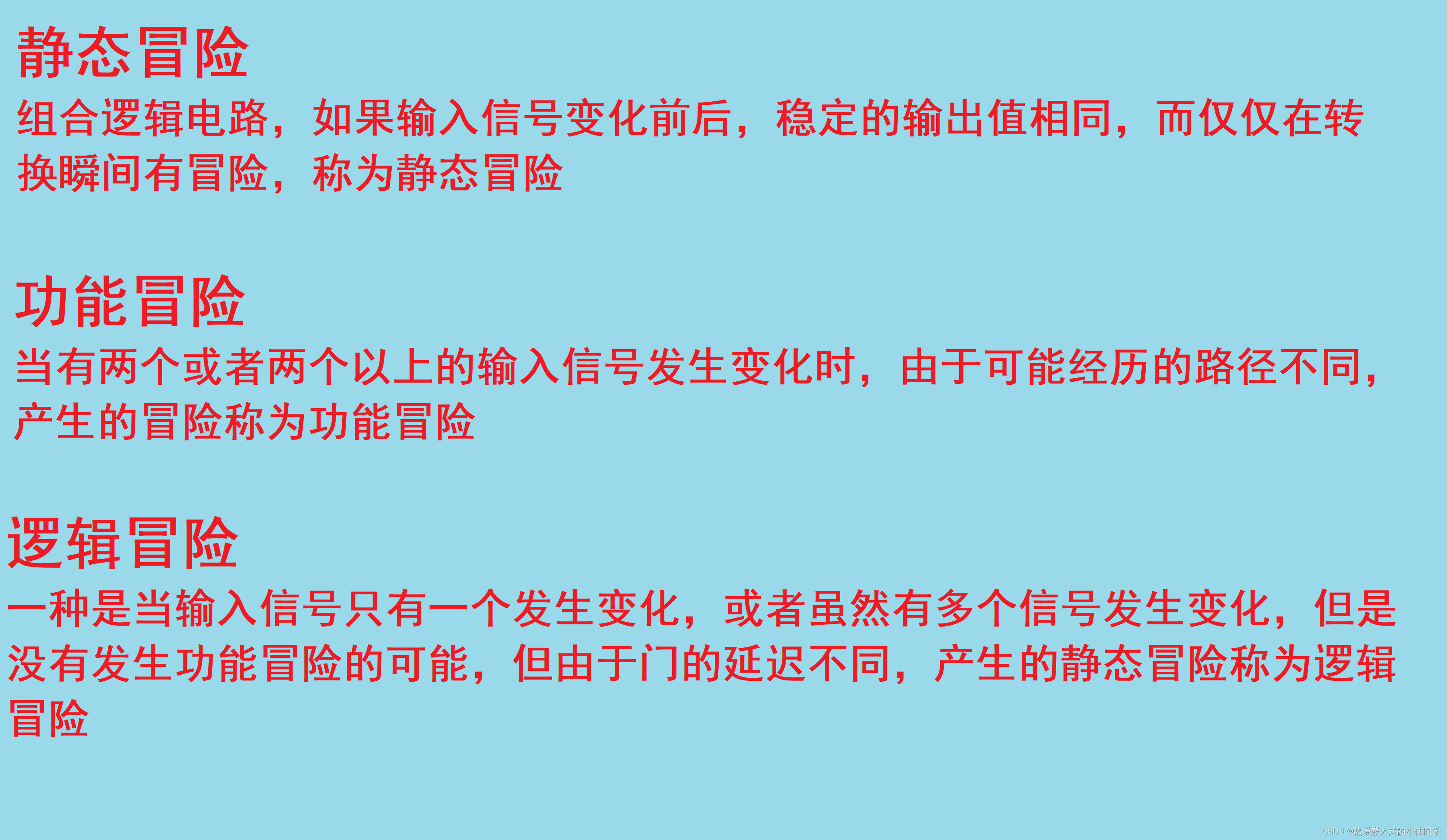

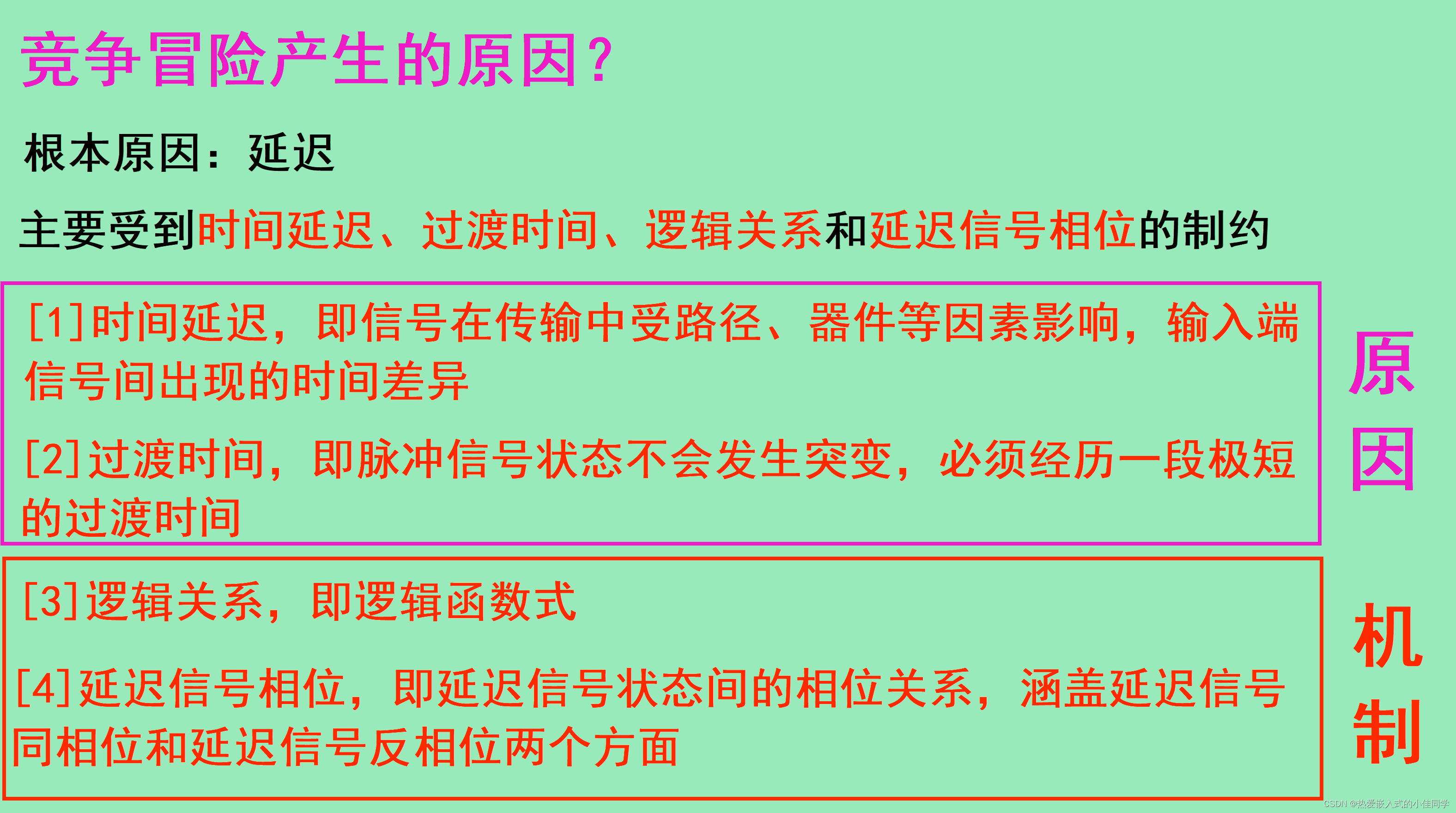

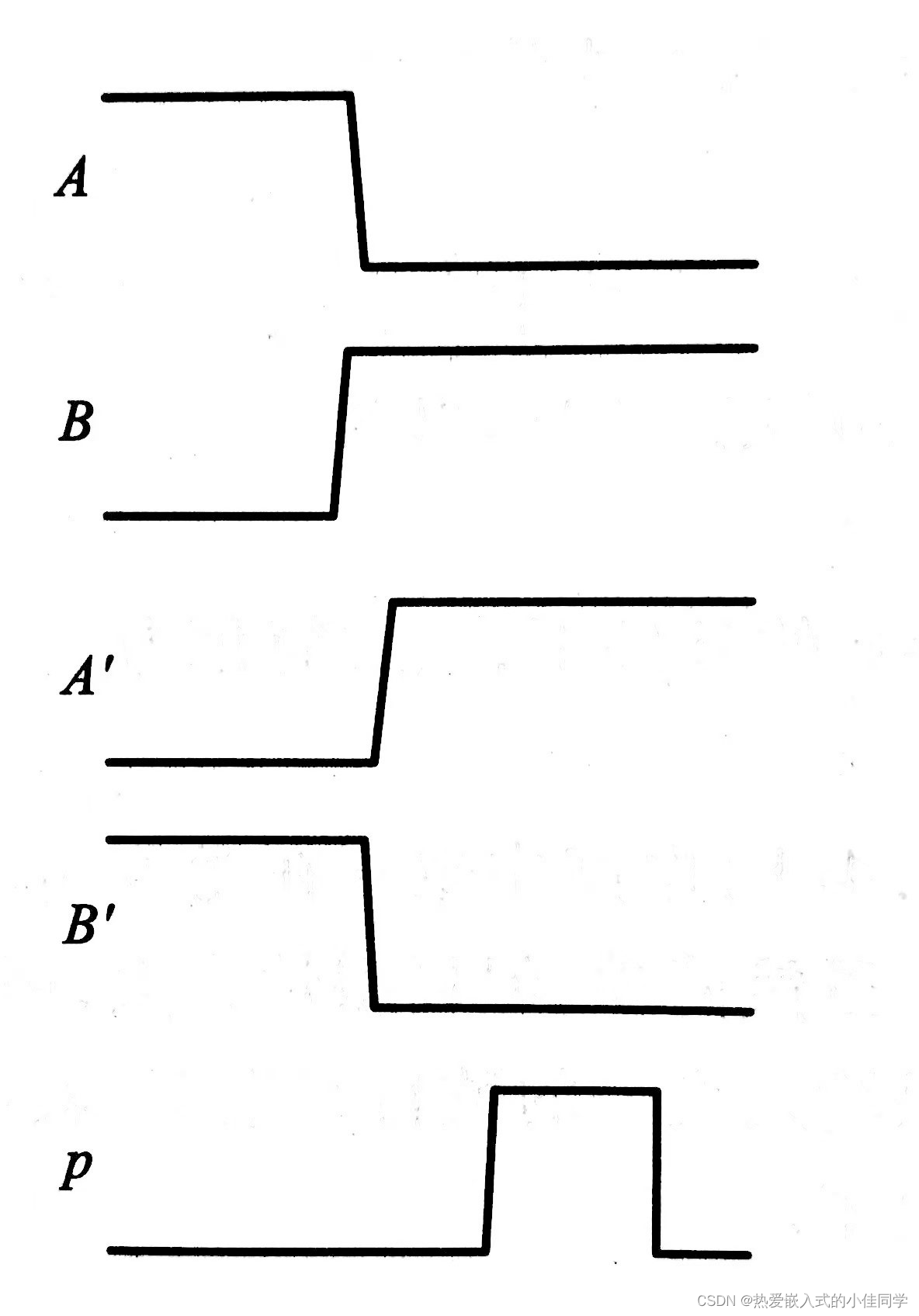

多路信号的电平值发生变化时,在信号变化的瞬间,组合逻辑的输出有先后顺序,往往导致出现一些不正确的尖峰脉冲信号,这些尖峰信号也称为"毛刺" 我们将门电路两个输入信号同时向相反的逻辑电平跳变的现象称为竞争。 由于竞争而在电路输出端可能产生尖峰脉冲的现象就称为竞争-冒险。 冒险 静态冒险 功能冒险逻辑冒险 动态冒险

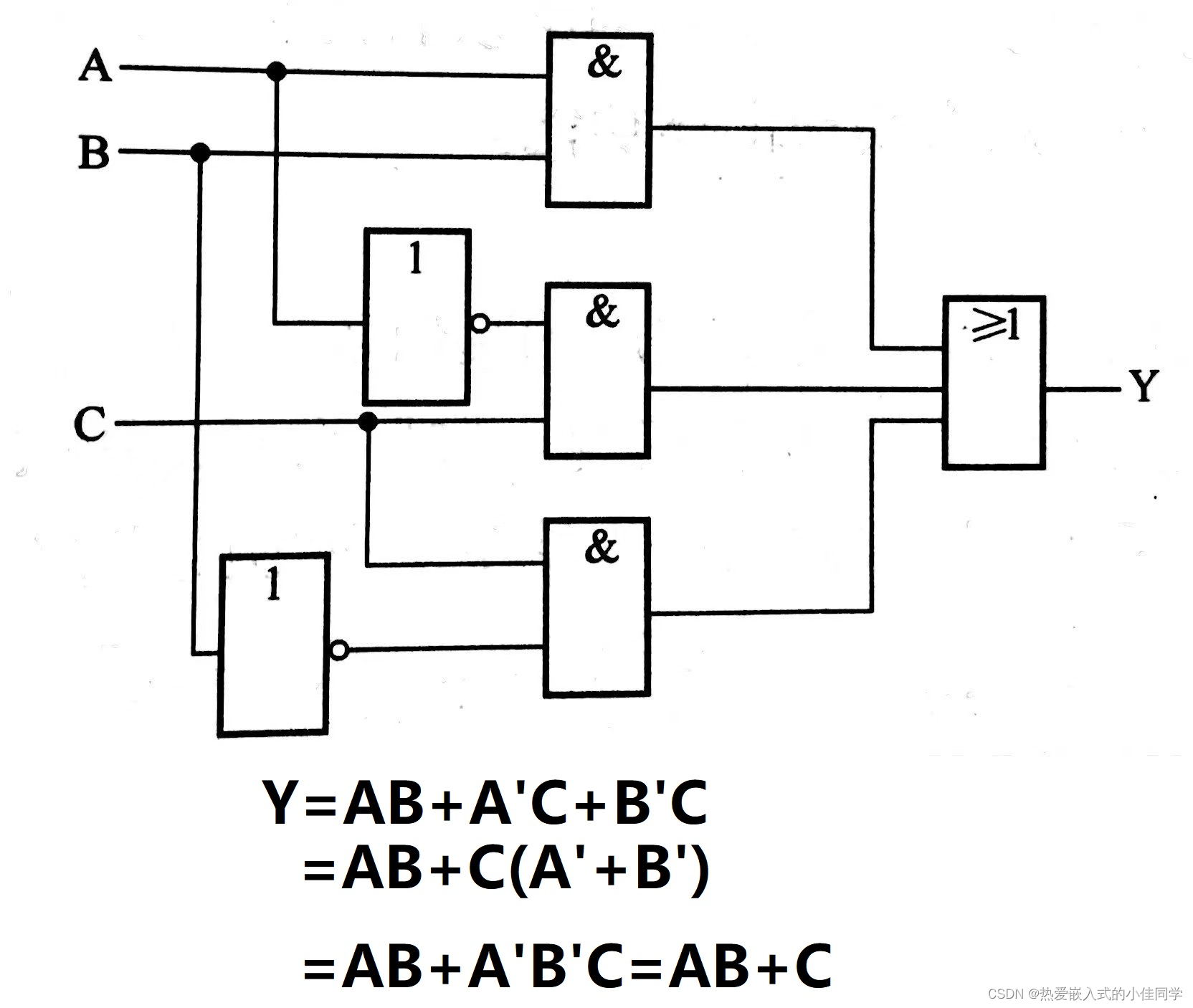

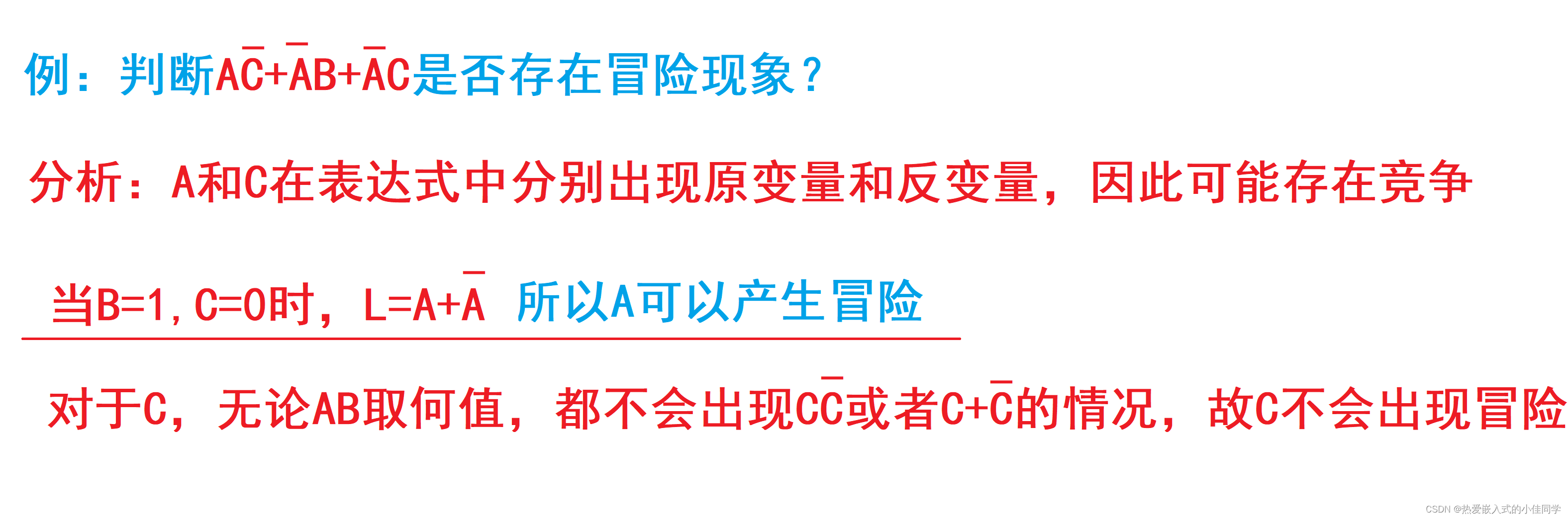

使对脉冲敏感的系统出现误动作 3.竞争-冒险的判别方法代数法:分析输入变量的取值情况,看是否存在某些输入变量的特定 取值使表达式出现Y=AA或者Y=AA'

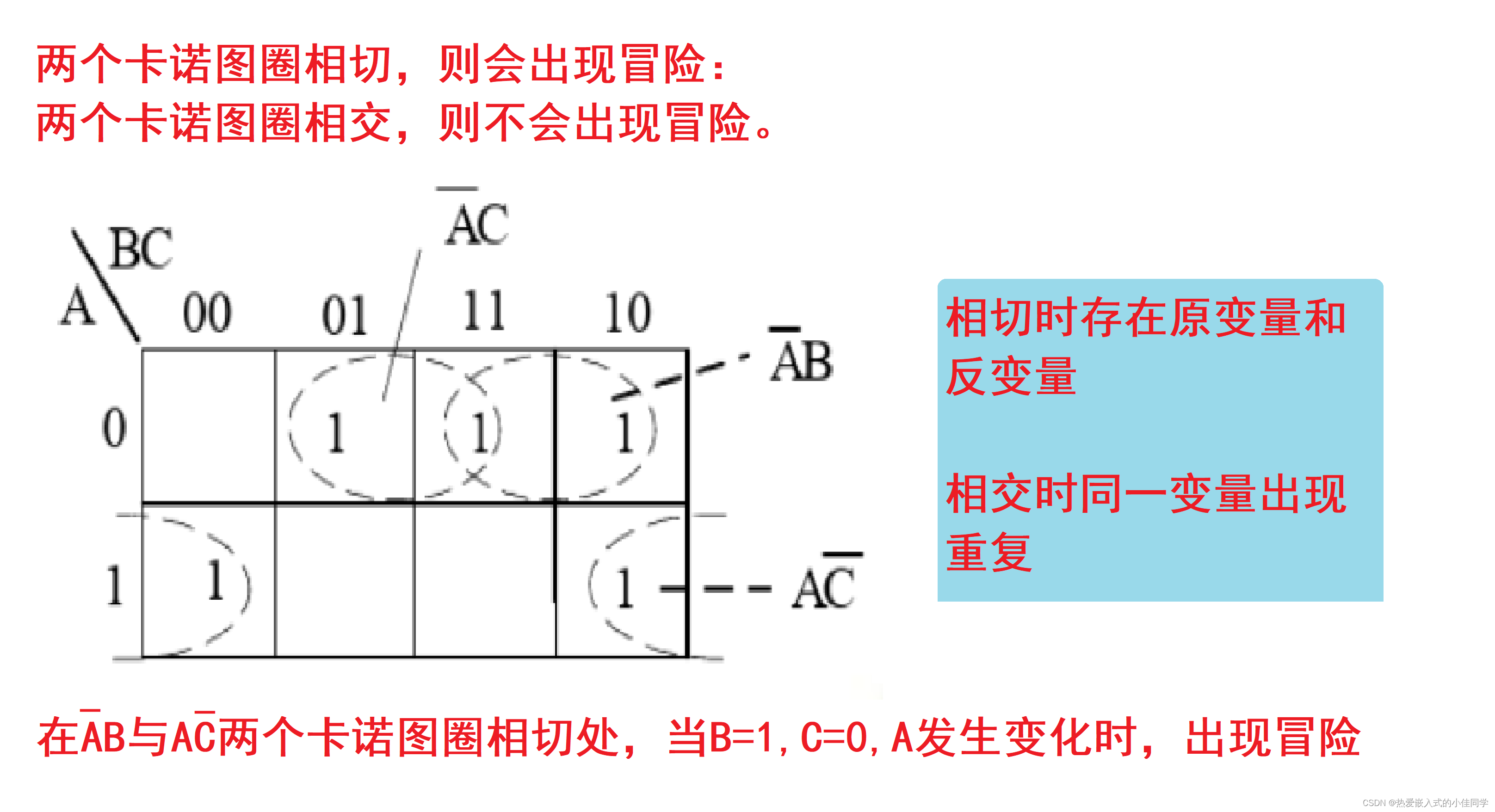

卡诺图法:由卡诺图上包围圈的相对位置,判别是否存在冒险的现象

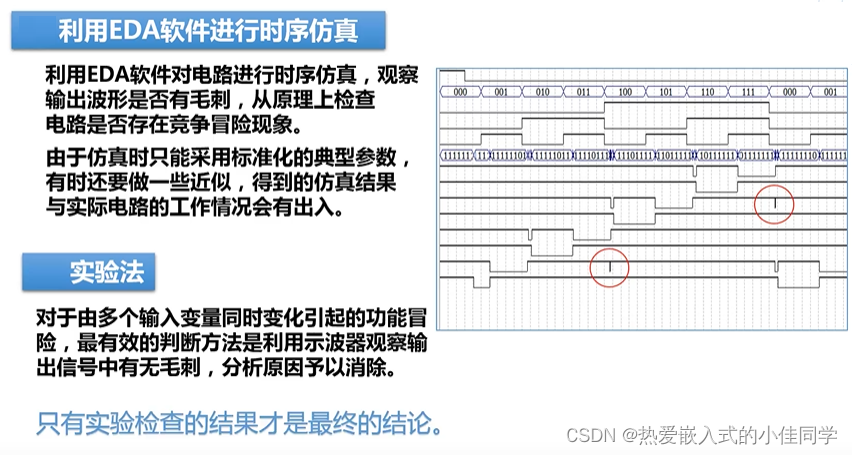

利用EDA软件进行时序仿真

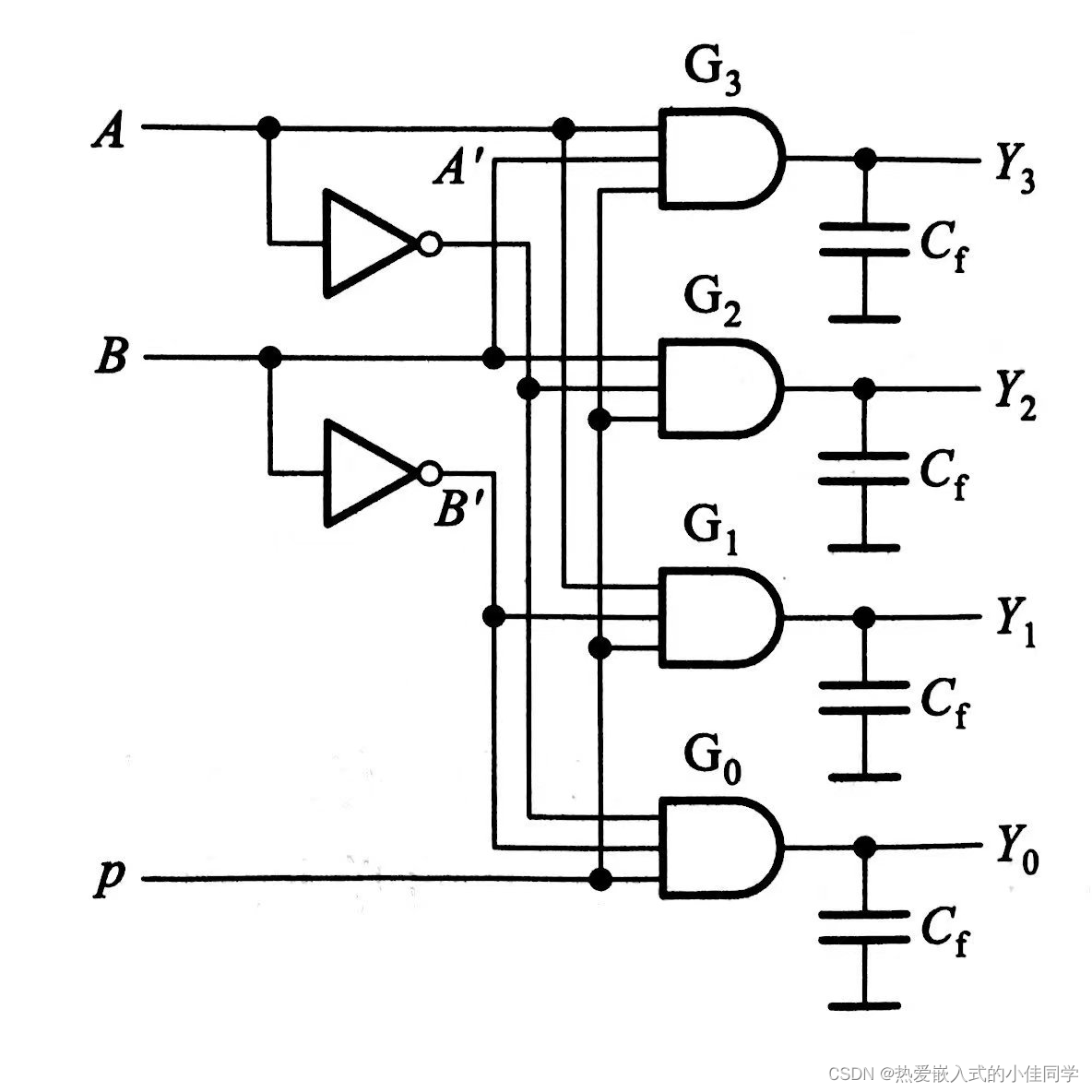

接入滤波电容: 由于竞争冒险而产生的尖峰脉冲一般都很窄,所以只要再输出端并联一个很小的滤波电容Cf,就可以削弱尖峰脉冲的幅度至阈值电压以下。

引入选通脉冲: 因为冒险发生在输入信号的瞬间,因此可以采用选通脉冲,在输入信号发生变化的瞬间不输出。

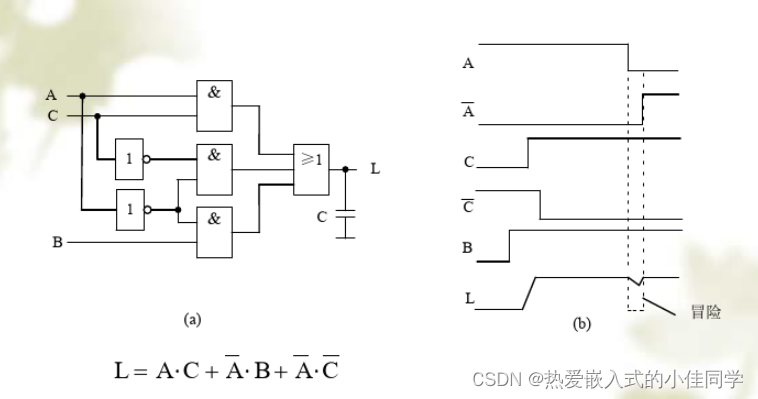

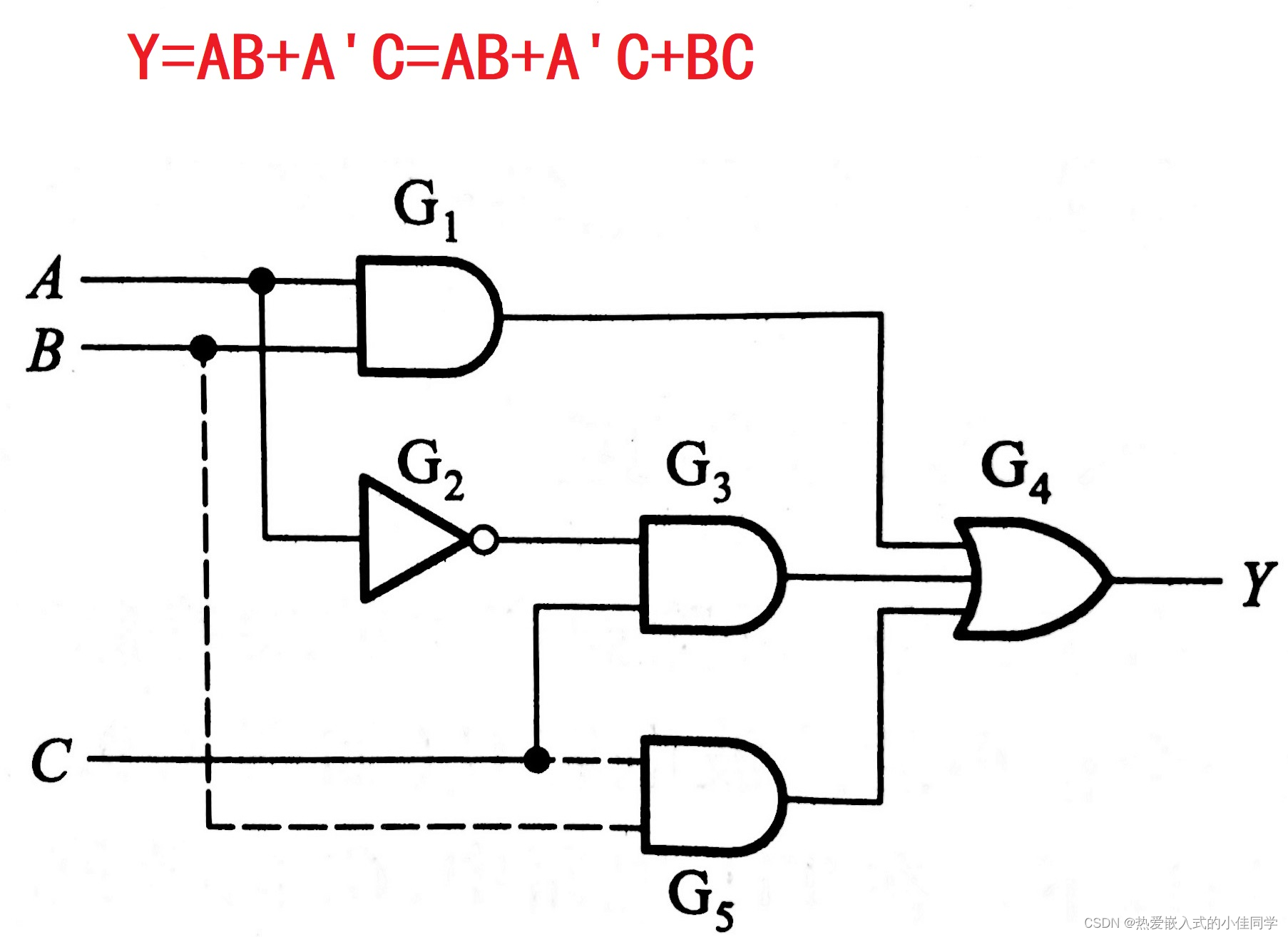

修改逻辑设计: 之所以产生冒险,是因为逻辑函数表达式中没有包含由不变变量组成的乘积项, 因此可以在逻辑函数表达式中增加所有的冗余项

|

【本文地址】

今日新闻 |

推荐新闻 |