基于FPGA的数字图像处理 |

您所在的位置:网站首页 › 在PAL制式中每帧等于多少秒 › 基于FPGA的数字图像处理 |

基于FPGA的数字图像处理

|

11.2.3 PAL

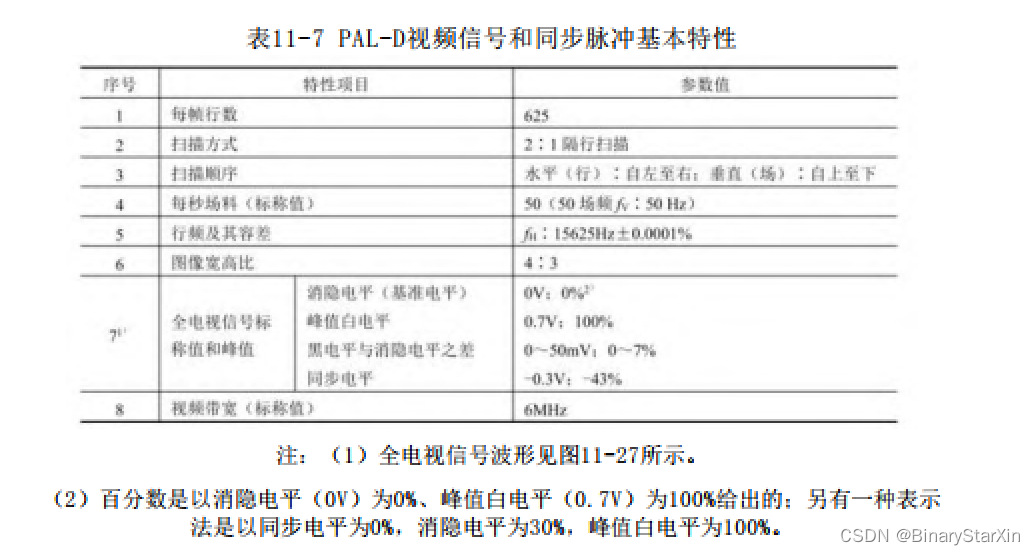

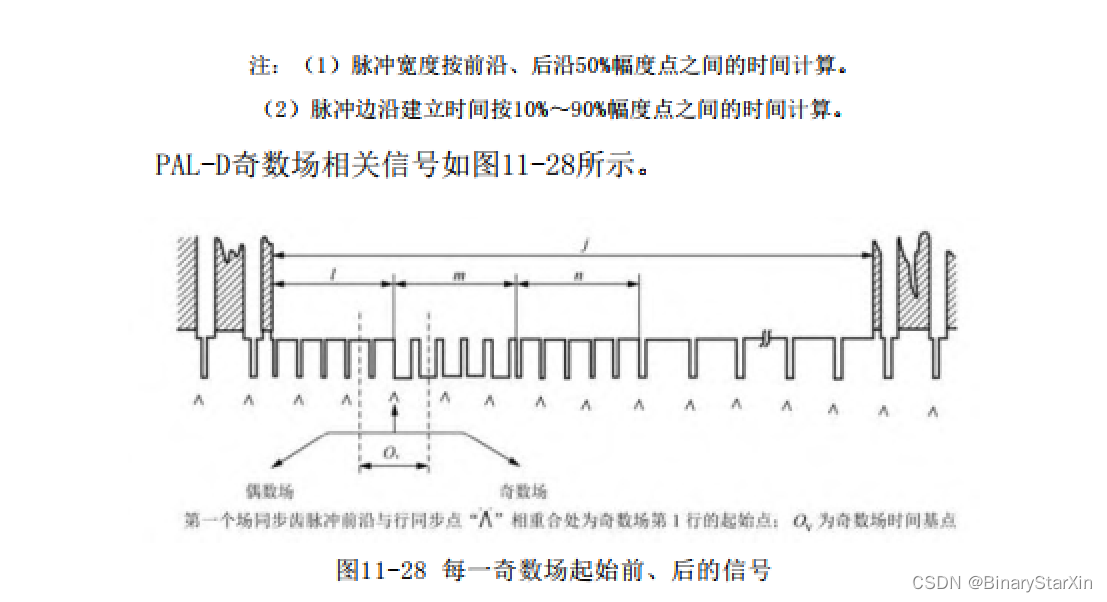

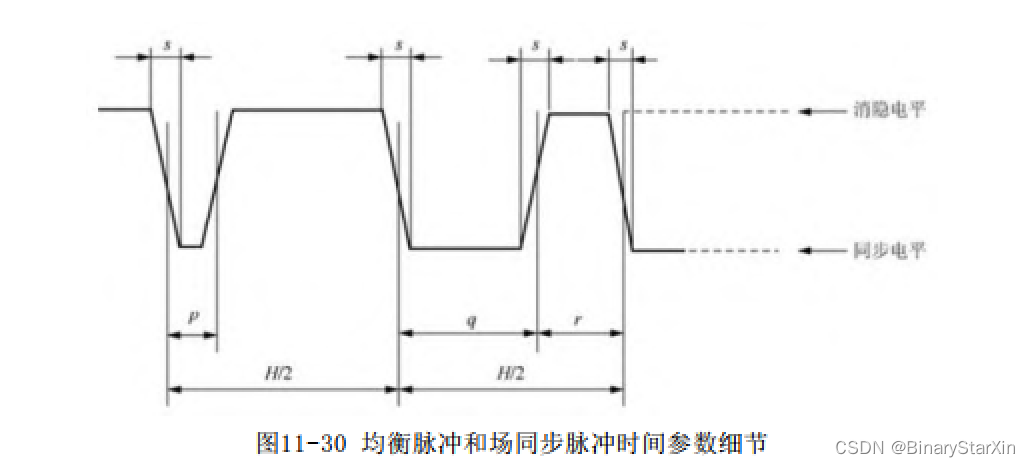

1.PAL简介PAL电视标准每秒25帧,电视扫描线为625线,奇场在前,偶场在 后,标准的数字化PAL电视标准分辨率为720×576,24比特的色彩位 深,画面的宽高比为4∶3,PAL电视标准用于中国、欧洲等国家和地 区,供电频率为50Hz,场频为每秒50场,帧频为每秒25帧,扫描线为 625行,其中,帧正程575行,帧逆程50行。采用隔行扫描方式,每场 扫描312.5行,场正程287.5行,逆程25行。场周期为20ms。行频为 15625Hz。图像信号带宽分别为4.2MHz、5.5MHz、5.6MHz等。 PAL制式中根据不同的参数细节,又可以进一步划分为G、I、D等 制式,其中PAL-D制是中国大陆采用的制式。接下来我们将重点介绍 PAL-D制式标准。 2.PAL-D制标准 1)视频信号和同步脉冲基本特性 PAL-D视频信号和同步脉冲基本特性如表11-7所示。

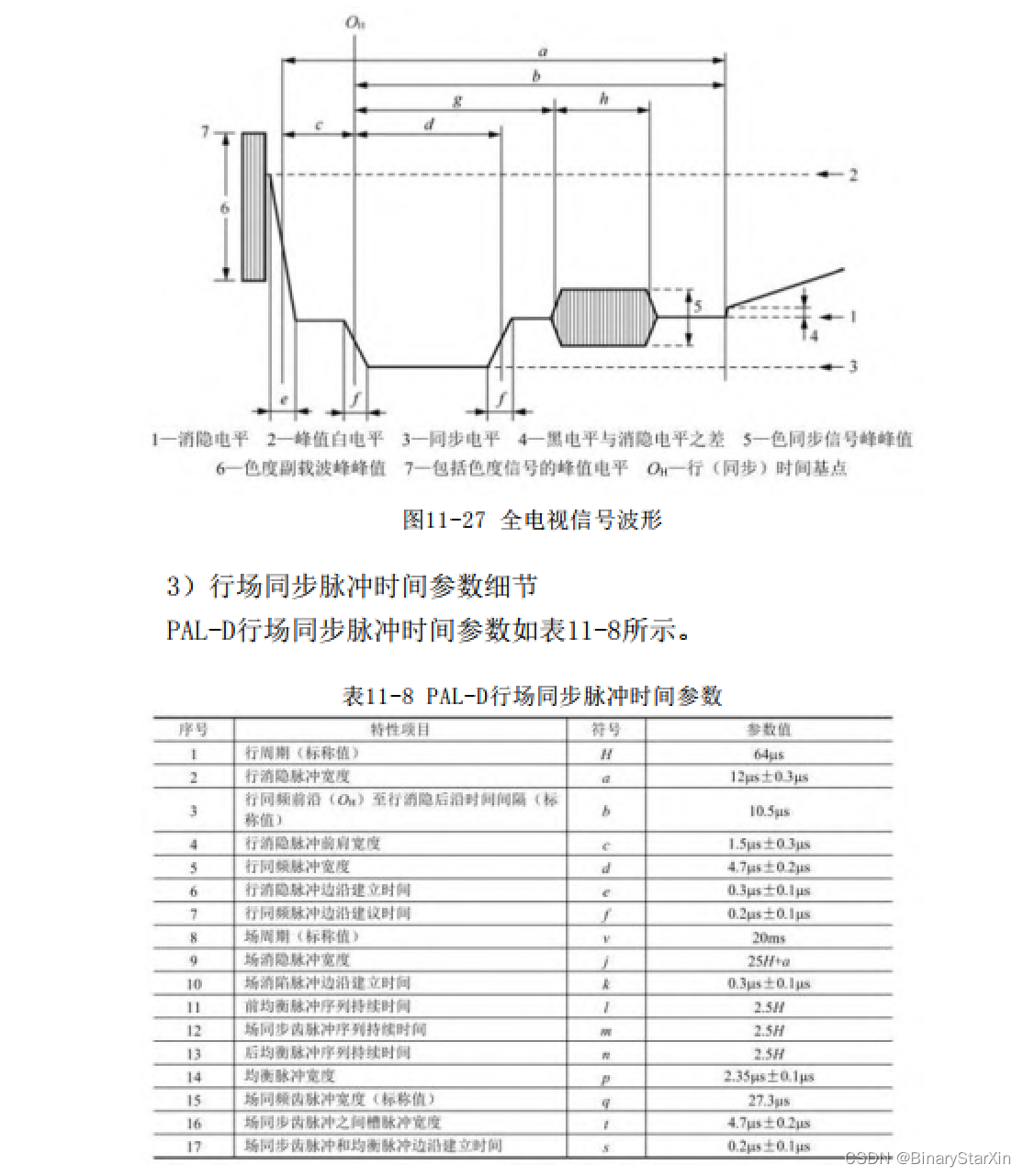

2)全电视信号波形 全电视信号波形如图11-27所示。

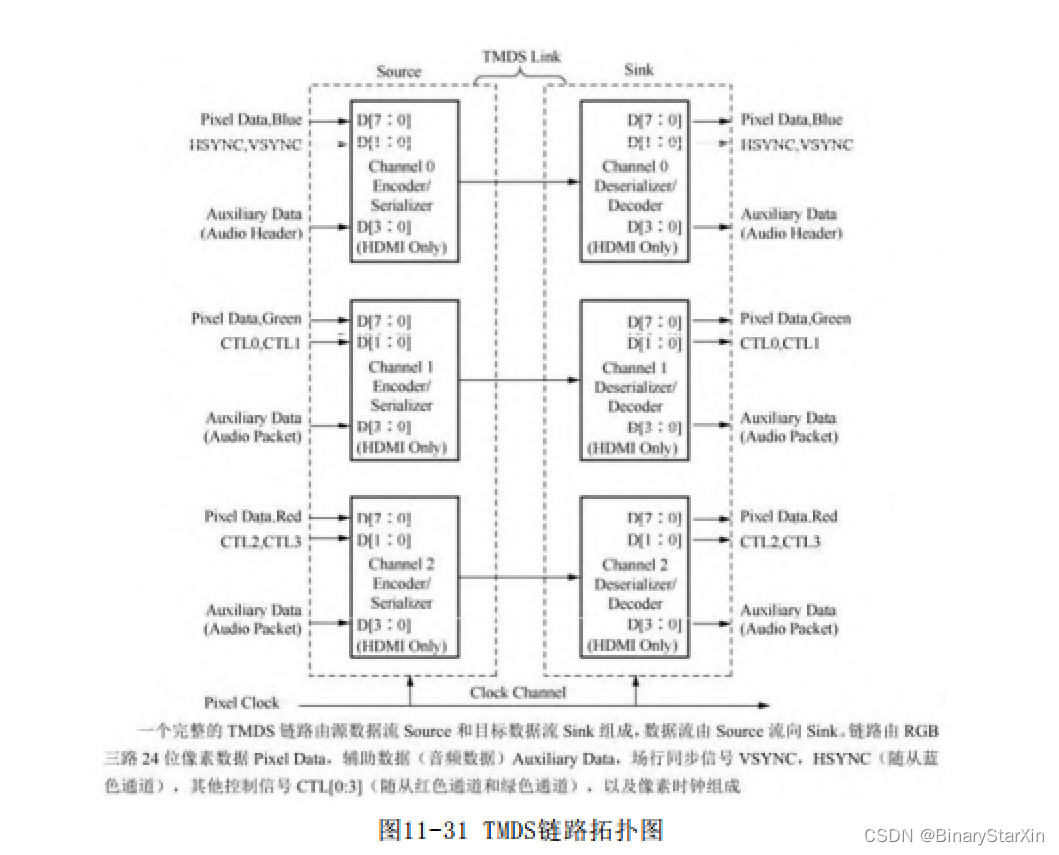

3.PAL与FPGA的接口 和VGA接口一样的是,PAL接口是模拟显示接口,不能直接与FPGA 相连,需要首先与一个视频编码器相连(上一节介绍的ADV7123即可满 足这个要求)。 4.Verilog设计实例 以下是一个满足PAL-D标准的Verilog设计实例: ** Input file : ** Component name : pal_d_sync.v ** Author : ZhengXiaoliang ** Company : WHUT ** Description : pal-d standard timing generator ********************************************************* ********** */ 'timescale 1ps/1psmodule pal_d_sync( reset_l, clk, //显示时钟 sync, //输出行同步信号 blank, //输出黑电平信号 vsync, //输出场同步信号 odd_even_flag //输出场奇偶信号 ); parameter CLK_FREQ = 13.5; parameter DW = 8; parameter VALID_HLEN = 640; //视频宽度 parameter VALID_VLEN = 512; //视频高度 input reset_l; input clk; output sync; output reg blank; output reg vsync; output reg odd_even_flag; //关键的时序参数 parameter H_TOTAL = 864; parameter H_SYNC = 63; parameter H_BP = 76; parameter H_FP = 23; parameter H_ACT = 702; parameter H_HALF = 432; parameter H_SYNC_HALF = 32; parameter H_START = H_SYNC + H_BP + 30;parameter H_END = H_START + VALID_HLEN; parameter V_TOTAL = 625; parameter V_HALF = 313; parameter V_START = 38; parameter V_END = V_START + ((VALID_VLEN >> 1)); parameter H_MAX = ((H_TOTAL - 1)); parameter V_MAX = V_TOTAL; reg [9:0] h_cnt; reg [9:0] v_cnt; reg normal_sync; reg v_sync; reg v_sync1; reg v_sync2; reg v_sync3; //horizon counter always @(posedge clk or negedge reset_l) if (((~(reset_l))) == 1'b1) h_cnt <= {10{1'b0}}; else begin if (h_cnt == H_MAX) h_cnt <= #1 {10{1'b0}}; else h_cnt <= #1 h_cnt + 10'b0000000001; end //vertical counter always @(posedge clk or negedge reset_l)if (((~(reset_l))) == 1'b1) v_cnt <= 10'b0000000000; else begin if (h_cnt == H_MAX) begin if (v_cnt == V_MAX) v_cnt <= #1 10'b0000000001; else v_cnt <= #1 v_cnt + 10'b0000000001; end end always @(posedge clk or negedge reset_l) if (((~(reset_l))) == 1'b1) normal_sync <= 1'b1; else begin if ((v_cnt >= 10'b0000000110 & v_cnt <= 10'b0100110110) |(v_cnt >= 10'b0100111111 & v_cnt <= 10'b1001101110)) begin if (h_cnt == 10'b0000000000) normal_sync <= #1 1'b0; else if (h_cnt == ((H_SYNC - 1))) normal_sync <= #1 1'b1; end elsenormal_sync <= #1 1'b1; end always @(posedge clk or negedge reset_l) if (((~(reset_l))) == 1'b1) v_sync <= 1'b1; else begin if (v_cnt == 10'b0000000100 | v_cnt == 10'b0000000101 | v_cnt== 10'b0100110111 | v_cnt == 10'b0100111000 | v_cnt == 10'b0100111100 | v_cnt== 10'b0100111101 | v_cnt == 10'b1001110000 | v_cnt == 10'b1001110001) begin if (h_cnt == 10'b0000000000 | h_cnt == ((H_HALF - 1))) v_sync <= #1 1'b0; else if (h_cnt == ((H_SYNC_HALF - 1)) | h_cnt == ((H_HALF+ H_SYNC_HALF - 1))) v_sync <= #1 1'b1; end else v_sync <= #1 1'b1; end always @(posedge clk or negedge reset_l) if (((~(reset_l))) == 1'b1) v_sync1 <= 1'b1; elsebegin if (v_cnt == 10'b0000000001 | v_cnt == 10'b0000000010 | v_cnt== 10'b0100111010 | v_cnt == 10'b0100111011) begin if (h_cnt == 10'b0000000000 | h_cnt == ((H_HALF - 1))) v_sync1 <= #1 1'b0; else if (h_cnt == ((H_HALF - H_SYNC -1)) | h_cnt == ((H_TOTAL- H_SYNC - 1))) v_sync1 <= #1 1'b1; end else v_sync1 <= #1 1'b1; end always @(posedge clk or negedge reset_l) if (((~(reset_l))) == 1'b1) v_sync2 <= 1'b1; else begin if (v_cnt == 10'b1001101111) begin if (h_cnt == 10'b0000000000 | h_cnt == ((H_HALF - 1))) v_sync2 <= #1 1'b0; else if (h_cnt == ((H_SYNC - 1)) | h_cnt == ((H_HALF +H_SYNC_HALF - 1)))v_sync2 <= #1 1'b1; end else if (v_cnt == 10'b0000000011) begin if (h_cnt == 10'b0000000000 | h_cnt == ((H_HALF - 1))) v_sync2 <= #1 1'b0; else if (h_cnt == ((H_HALF - H_SYNC - 1)) | h_cnt == ((H_HALF+ H_SYNC_HALF - 1))) v_sync2 <= #1 1'b1; end else if (v_cnt == 10'b0100111001) begin if (h_cnt == 10'b0000000000 | h_cnt == ((H_HALF - 1))) v_sync2 <= #1 1'b0; else if (h_cnt == ((H_SYNC_HALF - 1)) | h_cnt == ((H_TOTAL- H_SYNC - 1))) v_sync2 <= #1 1'b1; end else v_sync2 <= #1 1'b1; end always @(posedge clk or negedge reset_l) if (((~(reset_l))) == 1'b1) v_sync3 <= 1'b1; elsebegin if (v_cnt == 10'b0100111110) begin if (h_cnt == 10'b0000000000) v_sync3 <= #1 1'b0; else if (h_cnt == ((H_SYNC_HALF - 1))) v_sync3 <= #1 1'b1; end else v_sync3 <= #1 1'b1; end assign sync = normal_sync & v_sync1 & v_sync2 & v_sync3 & v_sync; always @(posedge clk or negedge reset_l) if (((~(reset_l))) == 1'b1) blank <= 1'b0; else begin if ((v_cnt >= V_START & v_cnt <= ((V_END - 1))) | (v_cnt >=((V_START + V_HALF)) & v_cnt <= ((V_END + V_HALF - 1)))) begin if (h_cnt == H_START) blank <= #1 1'b1; else if (h_cnt == H_END) blank <= #1 1'b0; endelse blank <= 1'b0; end always @(posedge clk or negedge reset_l) if (((~(reset_l))) == 1'b1) begin vsync <= 1'b1; odd_even_flag <= 1'b0; end else begin if ((v_cnt <= 10'b0000000101 | v_cnt >= 10'b1001101111)) vsync <= #1 1'b1; else vsync <= #1 1'b0; if (v_cnt <= 10'b0100111001 & v_cnt >= 10'b0000000101) odd_even_flag <= #1 1'b0; else odd_even_flag <= #1 1'b1; end endmoduleVGA信号和PAL信号均为模拟信号,对噪声相对比较敏感,在较高 的分辨率下,像素时钟频率更高,噪声问题也就越严重。数字视频接 口则可以克服这一局限性。 11.2.4 DVI/HDMI1.DVI简介 DVI的英文全名为Digital Visual Interface,中文称为“数字视 频接口”。它是一种数字视频接口标准,设计的目的是用来传输未经 压缩的数字化视频。目前广泛应用于LCD、数字投影机等显示设备上。 此标准由显示业界数家领导厂商所组成的论坛——“数字显示工作小 组(Digital Display Working Group,DDWG)”制定。DVI接口可以 发送未压缩的数字视频数据到显示设备。 DVI的数据格式来自于半导体厂商Silicon Image公司所发展的 PanelLink技术(此技术最早应用于笔记本电脑),并使用了最小化转 移 差 动 信 号 ( Transition Minimized Differential Signaling , TMDS)技术来确保高速串列数据发送的稳定性。一个“单通道” (Single Link)DVI通道包括了四条双绞缆线(红、绿、蓝和时钟频 率信号)。 单通道DVI最大可发送的分辨率为2.6百万像素,每秒钟更新60 次。新版的DVI规格中提供一组额外的DVI链接通道,当两组链接一起 使用时可以提供额外的发送带宽,称为双通道(Dual-link DVI)运作 模式。DVI规格中规定以165MHz的带宽为界,当显示模式需求低于此带 宽时应只使用单通道运作,以上则应自动切换为双通道。另外第二组 链接也可作为发送超过24位的像素色彩数据使用。 2.HDMI简介 伴随着数字高清影音技术的发展,DVI接口也开始逐渐暴露出种种 问题,甚至在一定程度上成为数字影像技术进步的瓶颈。DVI标准并不 支持音频信号的传输,同时,出于兼容性考虑,DVI预留了不少引脚来 支持模拟视频,因此接口体积较大。HDMI不仅可以满足1080p的分辨率,还能支持DVD Audio等数字音 频格式,支持八声道96kHz或立体声192kHz数码音频传送,可以传送无 压缩的音频信号及视频信号。 和DVI接口一致,HDMI在物理层也采用TMDS标准。 3.TMDS链路 首先我们给出TMDS的链路拓扑图,如图11-31所示。 4个通道的串行数据组成了DVI或HDMI的传输通道。对于DVI接口来 讲,视频数据为RGB4∶4∶4格式;HDMI默认情况下也采用RGB4∶4∶4 颜色空间,但是也可以采用YCrCb4∶4∶4格式或者YCrCb4∶2∶2格 式。第4个通道则传输像素时钟信号。 对于24色彩深度的视频流,每个色彩通道由8位数据组成。TMDS将 每个8位输入数据转换成一个10位的二进制序列,编码原则是使得高低 电平之间的转换次数最少,同时也使得直流分量在长时间跨度上趋于 平稳。编码后的信号在一个差分端口上传输即可。由于进行了串行化 处理,传输二进制位的时钟频率是像素时钟的10倍。又由于时钟频率 的范围可以很宽(取决于分辨率和刷新率),所以同时也通过另一个 通道来传输像素时钟。 此外,出于同步化的需要,保留了4个10位的编码字,在消隐时间 内进行传输。这些控制信号自然有场同步信号VSYNC和行同步信号 HSYNC而具体传输哪一个编码字,则由一对控制信号决定。控制信号一 般为0,但是在蓝色通道内,控制信号由水平和垂直方向上的同步信号 构成。此外还有用于字边界等同步控制信号。

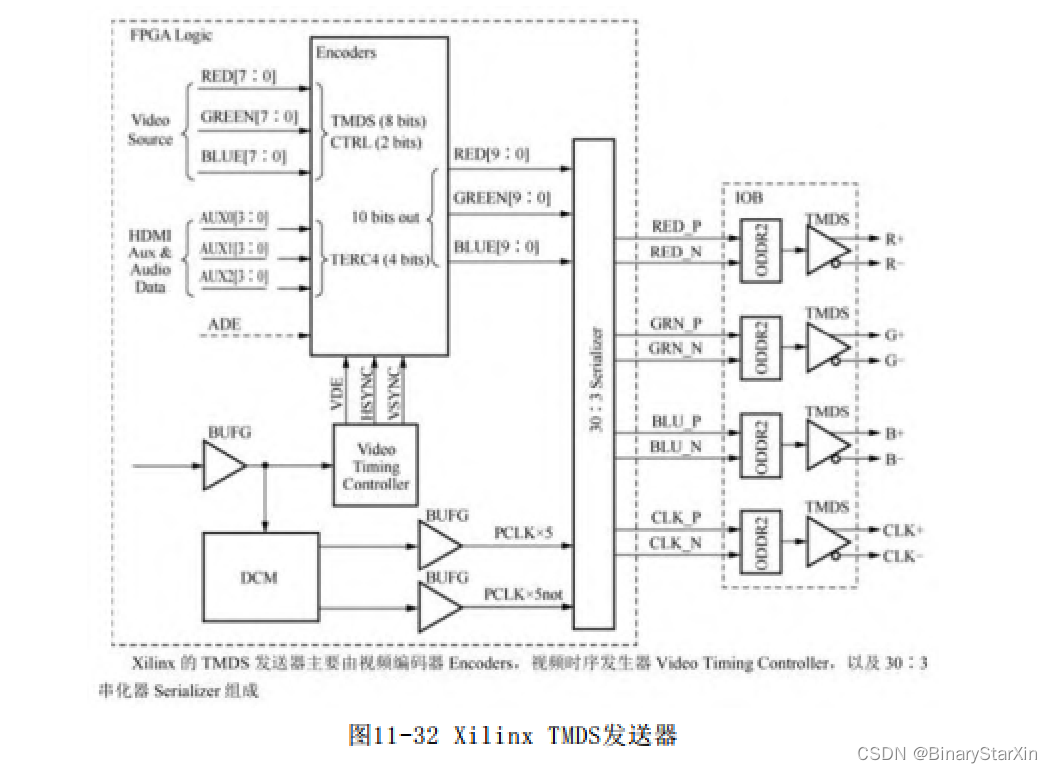

对于DVI传输,视频消隐时间仅被用来传输控制信号。而由于HDMI 同时包括音频通道,因此,在消隐时间内,HDMI也同时传输音频信 号,同时HDMI也传输辅助数据。这些复制数据包括帧信息和其他的描 述性的数据包。这也是DVI和HDMI协议的主要区别。 4.DVI/HDMI的FPGA实现 DVI和HDMI的编解码实现主要有两个方面的工作:视频8b/10b编码 和10∶1串行化输出。目前市场上也有很多DVI和HDMI的编解码芯片, 可以在一定程度上降低FPGA的设计复杂度和资源消耗。然而带来的问 题也是显而易见的:成本的提升和设计体积的增加。目前的FPGA很好地提供了对DVI和HDMI的接口支持。Xinlinx的 Spartan 3A系列之后的FPGA均支持满足TMDS标准的IO电气标准,最高 速率等级器件的数据传输带宽可高达1080 Mb/s,完全满足高清视频传 输的需求。FPGA内部的SERDERS串行化编解码模块则也可以很容易地实 现并串转换。 5.TMDS视频输出 通过TMDS接口的视频输出器需要至少包括两个方面的内容: 8b/10b编码器和并串转换器。 视频编码器将来自于待显示视频流的三通道8bit像素数据,辅助 数据,音频数据以及行场同步信号编码称为10bit格式。并串转换器则 将其转换为串行数据输出。串行化的比例为10∶1。一个采用Xilinx的 TMDS发送器的框图如图11-32所示。

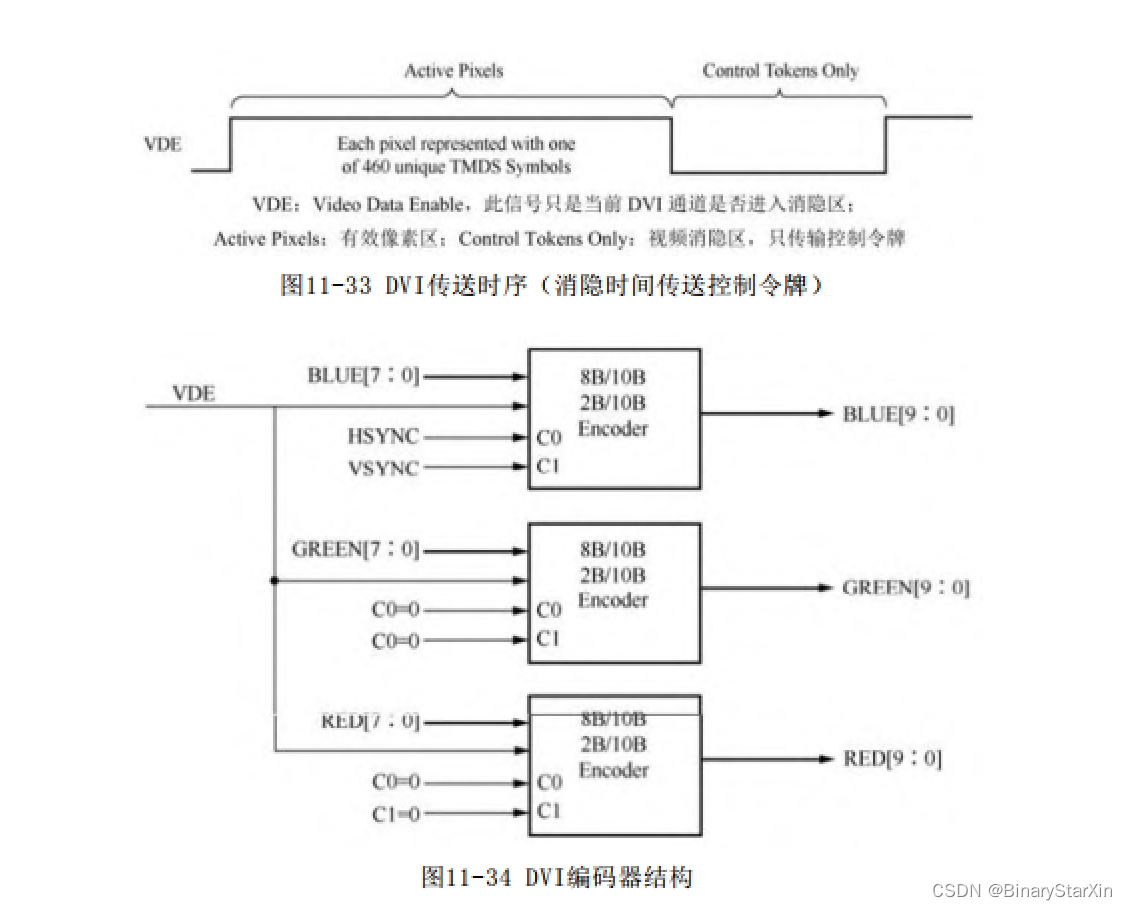

上述电路的实现需要Xilinx FPGA的双倍速率数据输出寄存器 ODDR2和TMDS差分输出缓冲器的硬件支持。 6.DVI编码器 输入的视频有效信号VDE(Video Data Enable)决定了视频的有 效区域和消隐区间,正如前面所述,控制信号只在消隐区间传递。其 编码时序和编码结构如图11-33和图11-34所示。

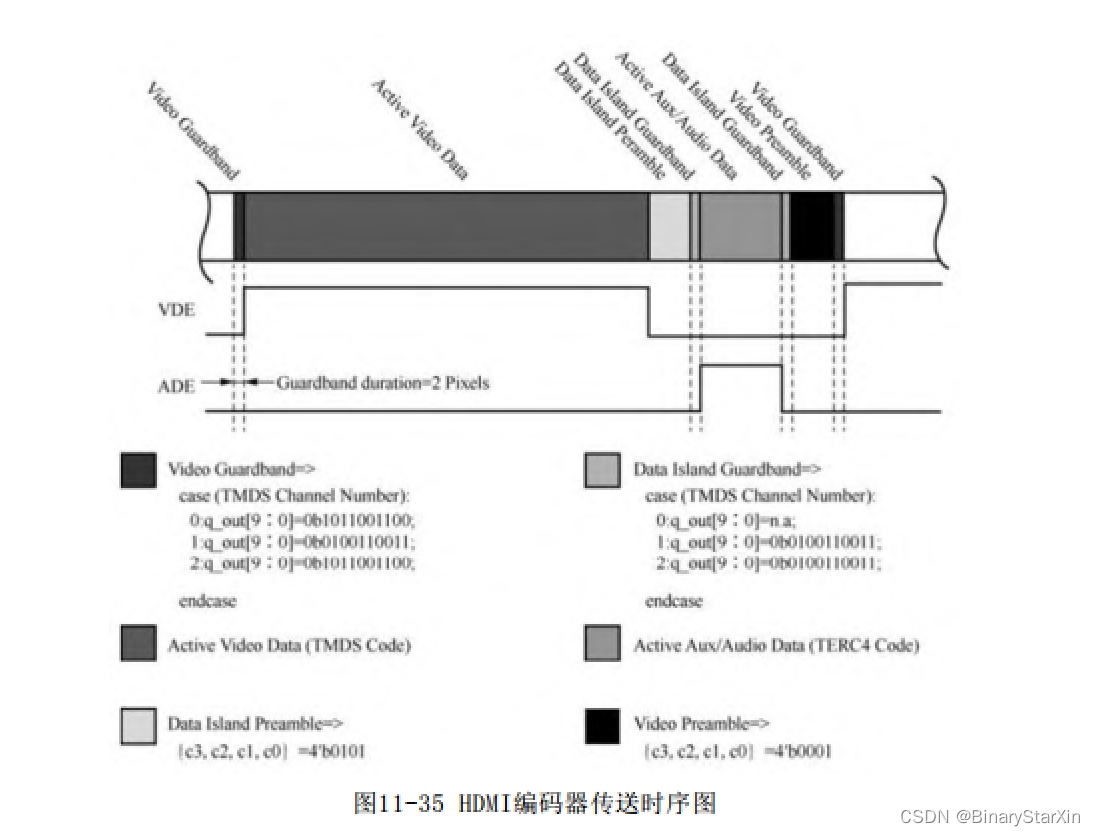

其编码主要包括3通道的8bitRGB通道数据,以及控制信号HSYNC, VSYNC,控制信号C0,C1。对于DVI接口,控制信号C0和C1并没有用 到,因此编码为0。HSYNC和VSYNC信号被编码到蓝色通道的消隐区间 内,而C0和C1信号被分别编码到绿色和红色通道的消隐时间内。 输入的8位视频信号按照TMDS标准中规定的编码算法进行编码 (8b/10b),每个8位的像素值被转换为从0到460的唯一一个10位的数 据。4 个 不 同 的 控 制 数 据 包 被 编 码 为 ( 2b/10b 编 码 ) : 10'b1101010100,10'b0010101011,10'b0101010100,10'b1010101011, 保证了每两个编码之间都有至少7个电平状态翻转。 7.HDMI编码器 HDMI编码器除了对DVI的相关信号进行编码,还需要对音频信号和 一些附加的控制信号(InfoFrames)进行编码。图11-35展示了一个完 整的HDMI视频流的结构图。主要包括以下8段数据: (1)控制数据包前导码:Data Island Preamble。数据包前导码 指示接下来的数据为控制数据包,包括辅助数据和音频数据。这个前 导码包括8个连续的相同控制令牌,并且只在绿色通道和红色通道有 效。

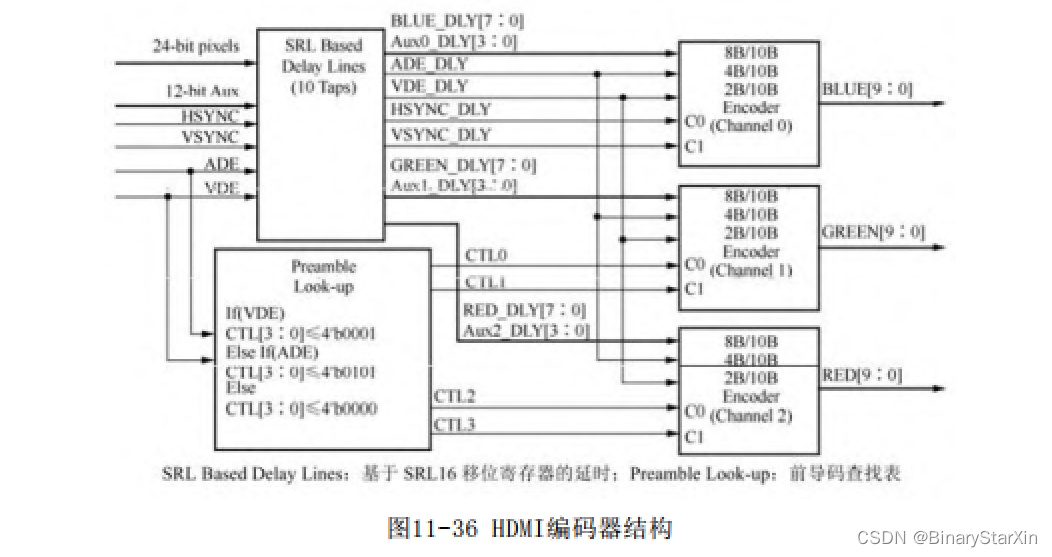

( 2 ) 控 制 数 据 包 隔 离 带 ( 前 ) : Data Island Guardband(Leading)。收发器的一种同步方式——在控制数据包前导 码和控制数据包之间的2个像素宽的隔离像素。 (3)有效的控制数据:Active Aux/Audio Data,包括音频数据 和辅助控制数据。音频数据编码方式为10bit TERC4(TMDS降错码)。 TERC4编码方式包括16个特定的4b/10b编码,只在绿色通道和红色通道 进行传输。 ( 4 ) 控 制 数 据 包 隔 离 带 ( 后 ) : Data Island Guardband(Trailing)。收发器的一种同步方式——在控制数据包和视频前导码之间的2个像素宽的隔离像素。 (5)有效视频前导码:Video Preamble。数据包前导码指示接下 来的数据为有效的视频数据包。这个前导码包括8个连续的相同控制令 牌,并且只在绿色通道和红色通道有效。 (6)视频隔离带(前):Video Guardband(Leading)。收发器的 一种同步方式——在视频前导码和视频数据之间的2个像素宽的隔离像 素。 (7)有效视频数据:Active Video Data。视频数据采用和DVI相 同的8b/10b编码方式。 (8)视频隔离带(后):Video Guardband(Leading)。收发器 的一种同步方式:在有效视频数据和控制数据前导码之间的2个像素宽 的隔离像素。 控制令牌同样是通过HDMI编码器来控制的,控制令牌有以下作 用: (1)在蓝色通道提供场行同步信息。 (2)指示控制数据包前导码消音区间的起始时刻。 (3)在绿色和红色通道输出保留的控制令牌{C0,C1}。 (4)指示控制包的{C0,C1}状态。 (5)在绿色和红外通道输出控制数据前导码。 和DVI编码器类似,场行同步信号HSYNC和VSYNC在蓝色通道区间被 传送。和DVI编码器不同的是HDMI的编码器利用另外两个通道,即红色 通道和绿色通道传输控制令牌。 在视频流从消隐区域到达有效视频区域之前,必须首先传送至少8 个视频前导码再跟随两个视频起始隔离带。同样,对于辅助数据或是 音频数据,在传送之前也必须加上响应的前导码和隔离带。 为了能在正确的时刻传送视频数据和控制数据,必须检测视频消 隐转换时刻及辅助数据转换时刻。这个可以通过在视频数据/音频数据和控制总线之间加上特定的延时来实现。图11-36展示了HDMI的编码结 构图。

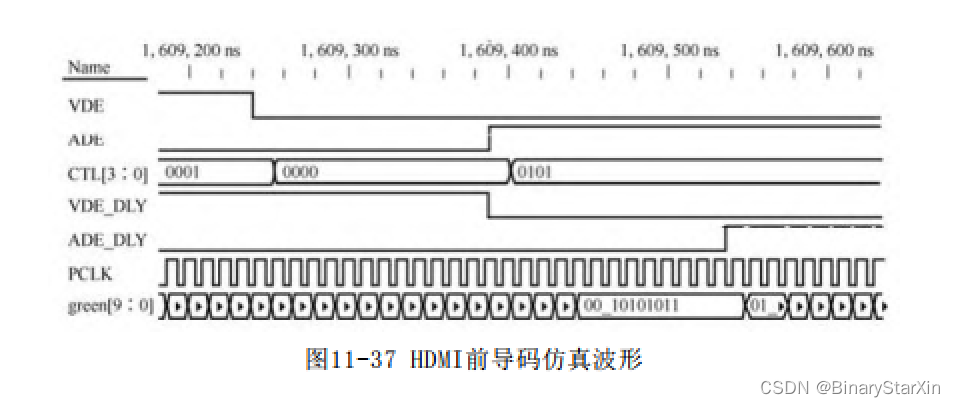

视频时序产生器将会生产24位的视频数据,12位的辅助控制数 据,2位的场行同步控制信号,1位视频有效信号VDE,1位辅助有效信 号ADE,共40位输入数据。编码器首先利用Xilinx的SRL16移位寄存器 将其延迟10个tap(这其中包括8个连续的前导码和2个内部的输出潜伏 期)。 不 经 过 移 位 寄 存 器 延 迟 的 控 制 信 号 查 找 表 则 会 预 先 提 供 video/blank/auxiliary等信号的时序转换信号。 图11-37的仿真波形展示了一个绿色通道内的前导码的产生。在数 据隔离带到来之前,8个连续的前导码首先传送。

|

【本文地址】

今日新闻 |

推荐新闻 |