logisim计组实验九 存储系统设计 |

您所在的位置:网站首页 › 双向映射实验原理 › logisim计组实验九 存储系统设计 |

logisim计组实验九 存储系统设计

|

原理:点这里 本章节均已通过测试~有问题请留言 电路文件已经托管至Github,欢迎star:点这里 文章目录 字库电路电路 MIPS RAM设计原理和要求电路图测试 MIPS寄存器文件设计电路测试 Cache映射机制与逻辑实现直接相连映射电路和讲解测试 字库电路 电路字库文件在16点阵字库文件分拆中 电路图 然后注意字库是按顺序放入 我还傻傻写了个均分的程序… MIPS RAM设计 原理和要求

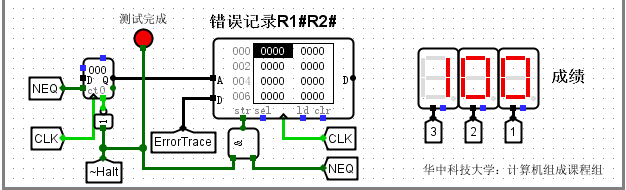

在这里挣扎了很长时间,教材和课程都过于不详细,朋友们帮忙去mooc上评论一下希望老师提供答案吧。也可能因为我太笨了 str信号区

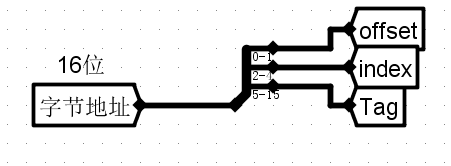

这个电路实现起来比较麻烦,不过幸好Cache行是可以复用的。 首先,字节地址的分配是这样的:

命中率稳定在了0.8 |

【本文地址】

今日新闻 |

推荐新闻 |

补充: Addr在字访问时忽略最低两位;半字访问时忽略最低位,倒数第二位为片选;字节访问时,第二位进行片选。 这里的难点是如何进行Din分割,和str信号的选取。 首先要理解片选信号和存储单元的关系。 为了避免存储单元中的数据被覆盖,所以要根据Mode和低二位决定4个存储器哪一个需要去存储。 以最低位存储器的str信号来说,字访问的时候str必须高电平;1字节访问的时候当片选信号为0才进行访问;2字节访问的时候,片选信号为0时进行访问。

补充: Addr在字访问时忽略最低两位;半字访问时忽略最低位,倒数第二位为片选;字节访问时,第二位进行片选。 这里的难点是如何进行Din分割,和str信号的选取。 首先要理解片选信号和存储单元的关系。 为了避免存储单元中的数据被覆盖,所以要根据Mode和低二位决定4个存储器哪一个需要去存储。 以最低位存储器的str信号来说,字访问的时候str必须高电平;1字节访问的时候当片选信号为0才进行访问;2字节访问的时候,片选信号为0时进行访问。 其它区域

其它区域

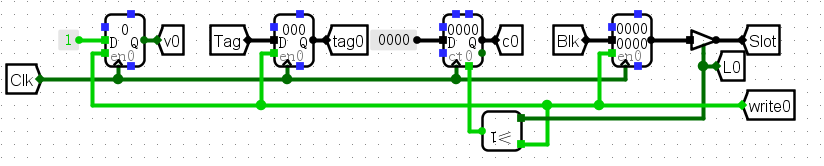

index就是槽号。 加入一个判断Cache行是否已被写入的多路选择器:

index就是槽号。 加入一个判断Cache行是否已被写入的多路选择器:  判断是否需要写入的解复用器,当数据块准备好并且Miss(没有命中)时需要进行写入:

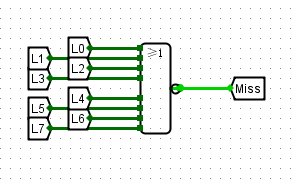

判断是否需要写入的解复用器,当数据块准备好并且Miss(没有命中)时需要进行写入:  或非门,用于判断是否命中:

或非门,用于判断是否命中:  解复用器和比较器,找出相应的Cache行

解复用器和比较器,找出相应的Cache行  Cache行,使用了三个寄存器和一个计时器,使能端为1时进行数据读入。 当命中时,L为1,三态门选通,进行数据的写出。

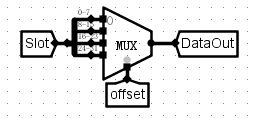

Cache行,使用了三个寄存器和一个计时器,使能端为1时进行数据读入。 当命中时,L为1,三态门选通,进行数据的写出。  Cache行偏移,得到数据。

Cache行偏移,得到数据。