FPGA入门 |

您所在的位置:网站首页 › verilog32位加法器 › FPGA入门 |

FPGA入门

|

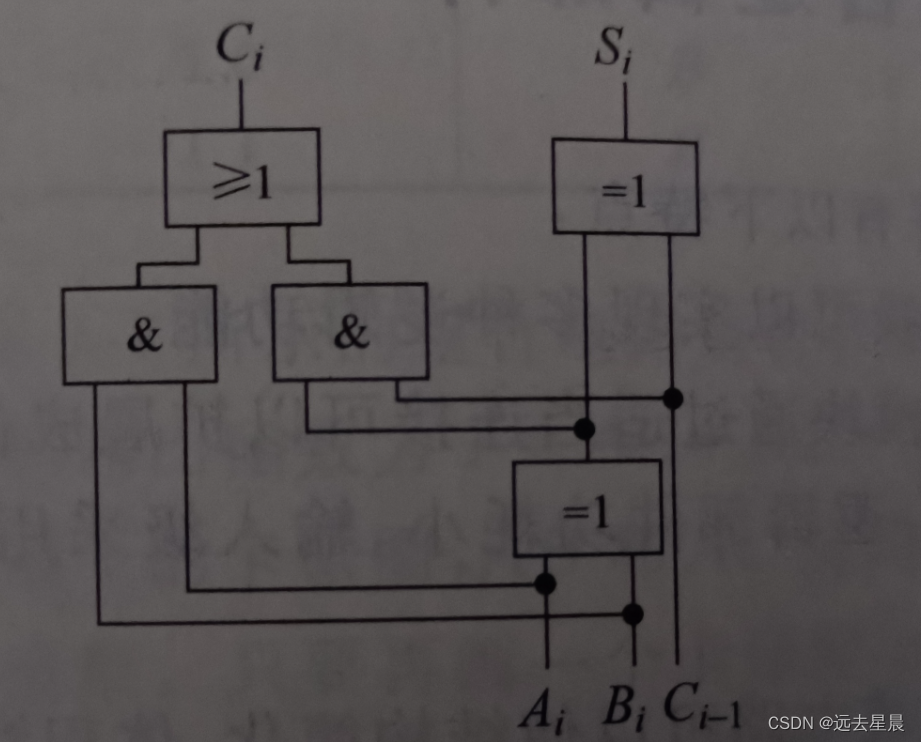

1、目的

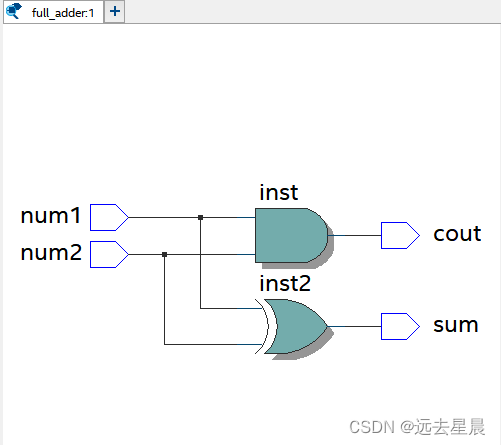

1、基于Quartus件完成一个1位全加器的设计,分别采用:1)原理图输入 以及 2)Verilog编程 这两种设计方法。 2、在此基础上,用原理图以及Verilog 编程两种方式,完成4位全加器的设计,对比二者生成的 RTL差别;使用modelsim验证逻辑设计的正确性。 2、了解全加器: 1 1位全加器的真值表:num1和num2是加数,cin是低位进位,cout是高位进位(我将其理解为溢出),sum是本位和 num1num 2cincoutsum0000000101010010111010001101101101011111 2 输出公式:sum=num1⊕num2⊕cin cout=(num1⊕num2)* cin+num1* num2=(num1&num2)∣(num1&cin)∣(num2&cin) 3 原理图:

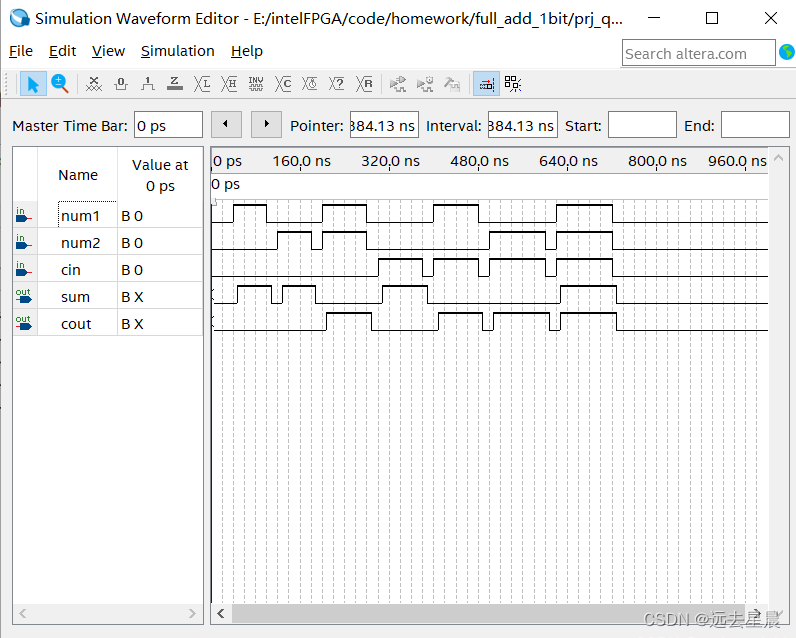

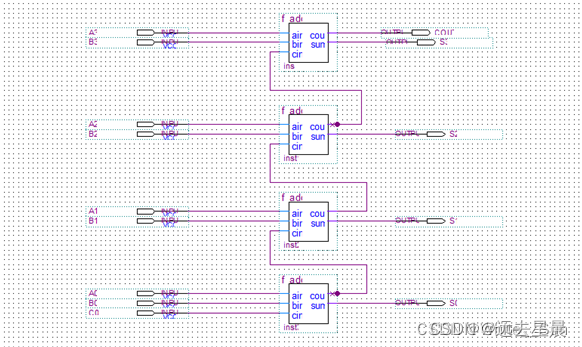

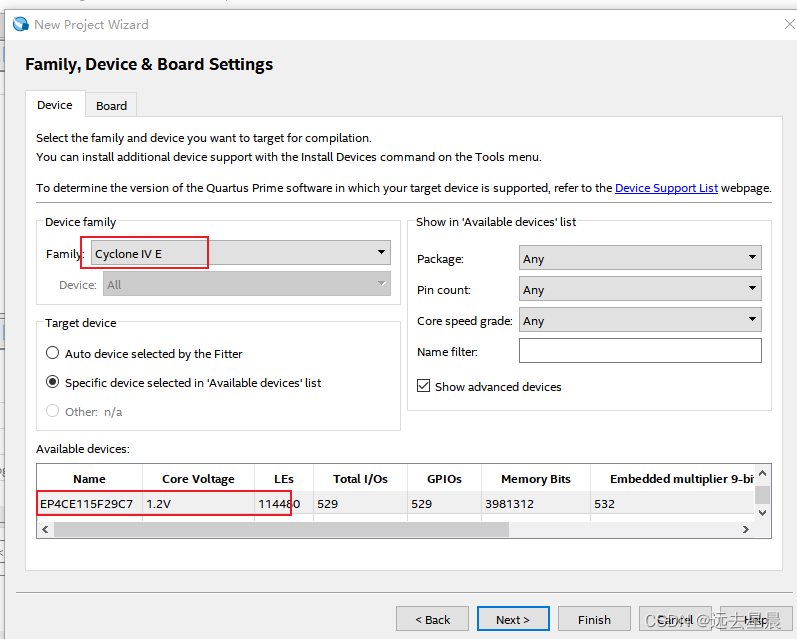

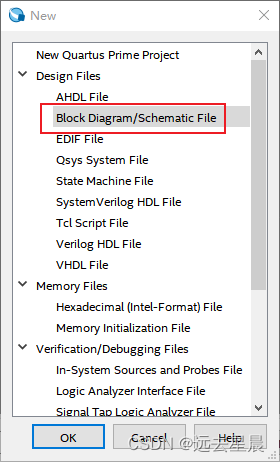

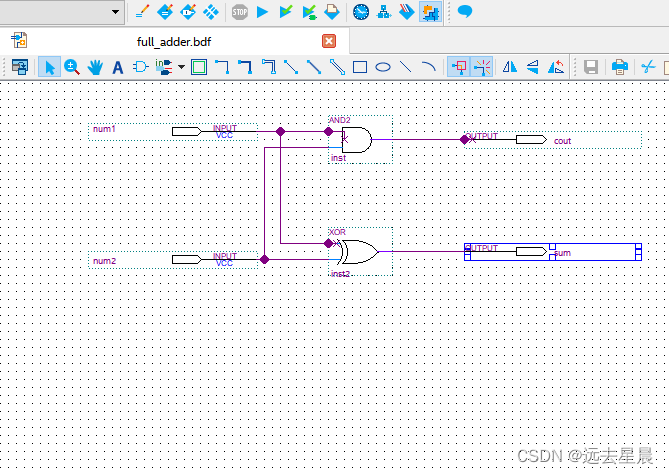

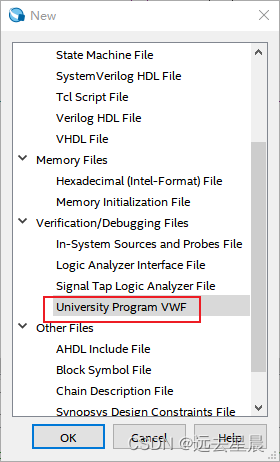

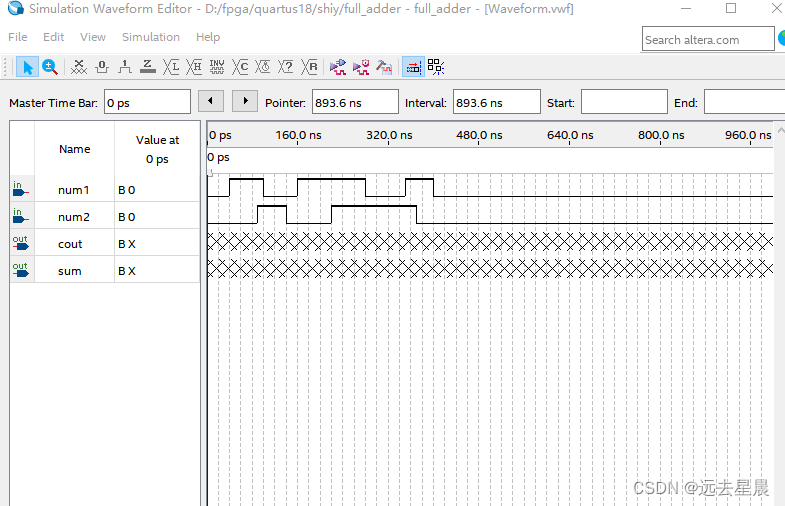

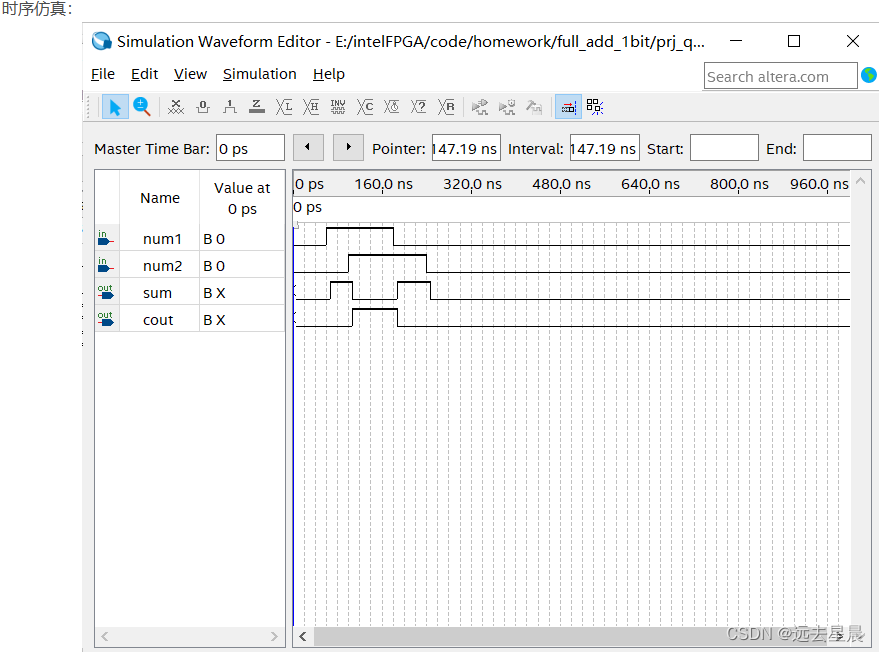

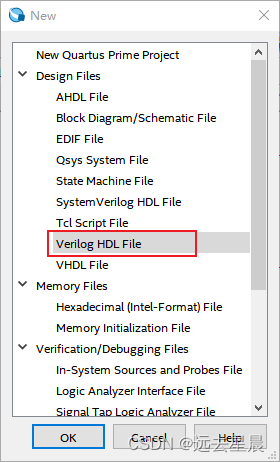

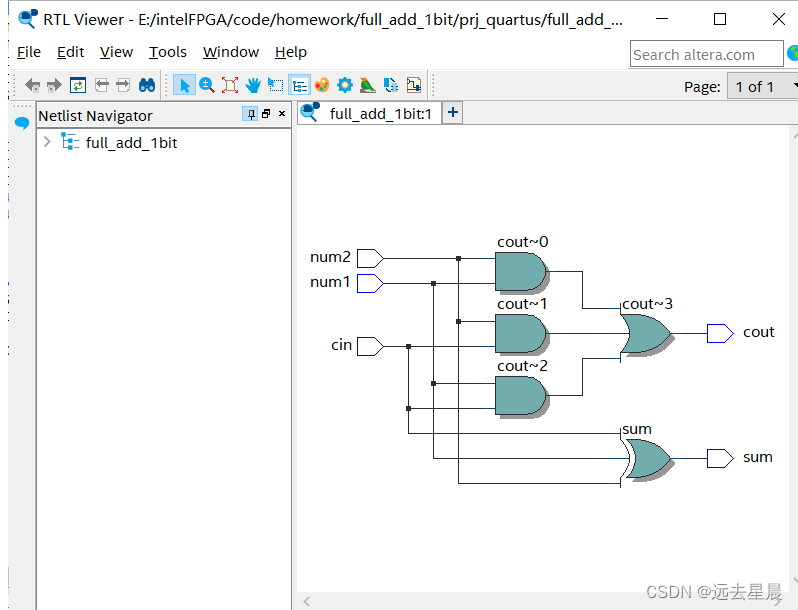

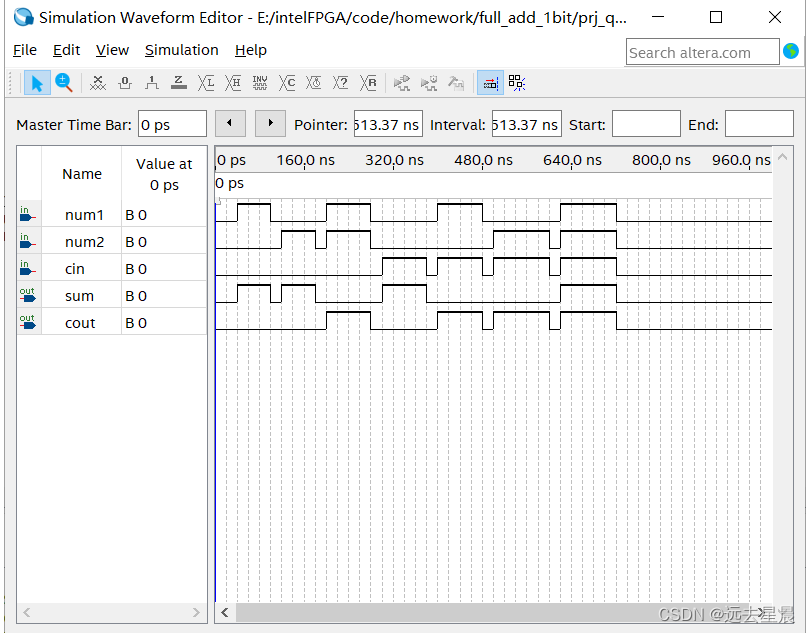

然后在出现的界面下先Next,填写工程的路径和名称,我这里创建的项目名称为full_add_1bit;然后接着Next,直到出现下面界面并进行相应操作。接着一路Next,直到Finish,完成工程的创建。 点击File->New之后会显示如下界面,然后选择被方框框住的选项 双击器件可以修改器件名称,为了之后的试验,将两个input分别修改为num1和num2,and2的输出为cout,xor的输出为sum。绘制出来的原理图如下图所示 保存文件(ctrl+s),并编译 等待编译完成之后就可以通过Tool->Netlist Viewers->RTL Viewer,来查看电路图 创建一个向量波形文件,File->New,然后选择“University Program VWF” 之后会进入到界面,然后按照步骤进入到信号添加界面 然后先选择Node Finder这个选项,然后再点击List,之后点击’>>',然后点击两次OK,就可以回到上面的那个界面,并且,此时信号也添加成功了。 添加成功之后的界面: 编辑好之后先保存这个文件,然后点击功能仿真按钮(左边),结果: 时序仿真: 先创建一个verilog文件: 先将之前创建的电路图文件从项目中删除,也就是.bdf文件删除,否则会有报错。记得要把新建的verilog文件设置为顶层文件 然后进行编译,当编译完成之后就可以进行电路图的查看了。通过tool->Netlist Viewers->RTL Viewer进行查看 创建一个vwf文件,然后接下来的操作和之前的相同,就不再过多赘述。这里就直接给出仿真结果 功能仿真结果:

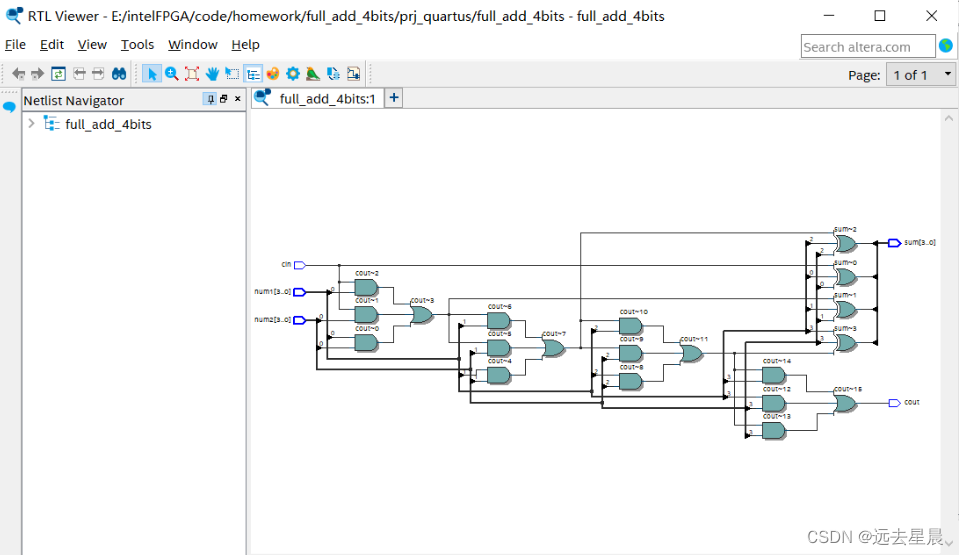

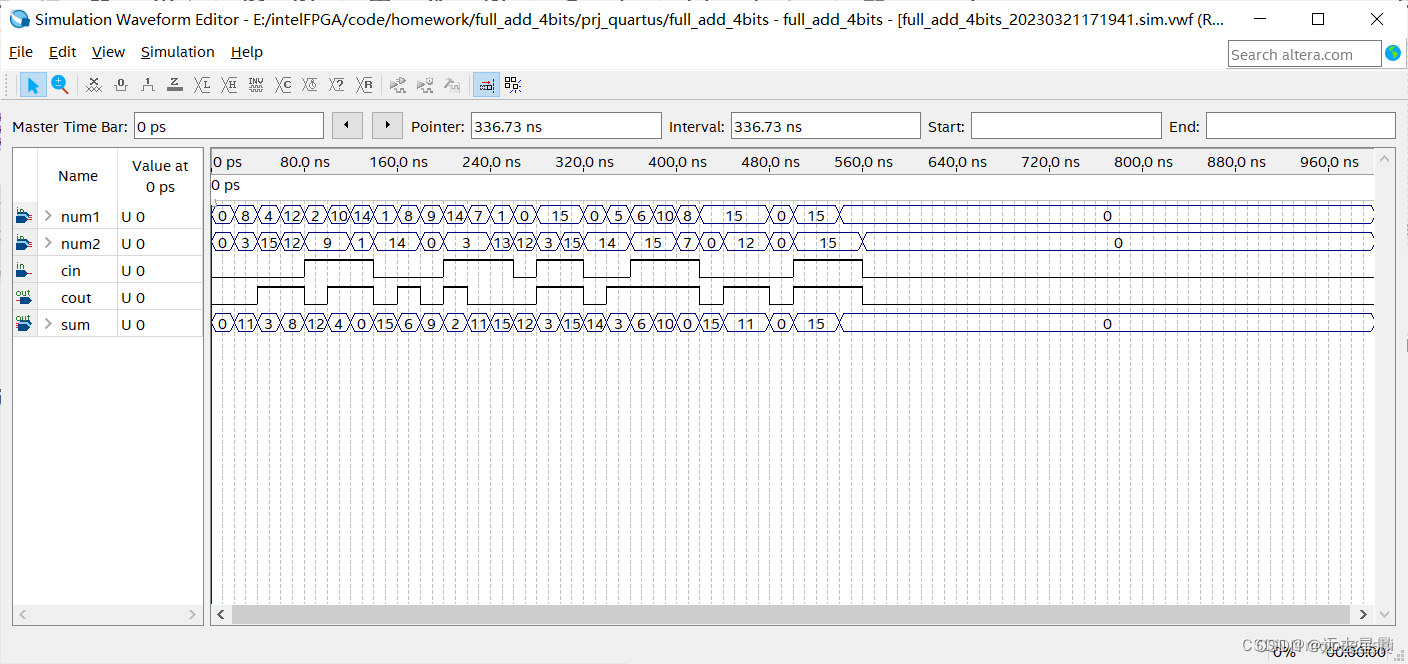

实际上四位全加器和一位全加器的差别并不是很大。我们以一个例子来解释,比如说:这里有两个数,分别是num1=0011,num2=1110。我们算的时候是从最后一位开始一直向前加: num1的最后一位是1,num2的最后一位是0,两个相加得到01,所以sum的最后一位是1,没有进位; num1的倒数第二位是1,num2的倒数第二位是1,没有低位进位,相加得10,所以sum的倒数第二位是0,向前进位为1; num1的第二位是0,num2的第二位是1,低位进位为1,所以相加得10,sum的第二位为0,向前进位为1; num1的第一位是0,num2的第一位是1,低位进位为1,所以相加得10,sum的第一位为0,向前进位为1; 所以,通过上面的步骤,我们可以得到sum=0001,向前进位cout=1。 1 创建文件,编写代码先创建一个verilog文件,并将下面代码复制到文件中 module four ( num1, num2, cin, cout, sum ); input [3:0] num1; input [3:0] num2; input cin; output cout; output [3:0] sum; reg cout; reg [3:0] sum; reg add; always @(num1 or num2 or cin) begin // 第一位 sum[0] = (num1[0] ^ num2[0]) ^ cin; cout = (num1[0] & num2[0]) | (num2[0] & cin) | (num1[0] & cin); add = cout; // 第二位 sum[1] = (num1[1] ^ num2[1]) ^ add; cout = (num1[1] & num2[1]) | (num2[1] & add) | (num1[1] & add); add = cout; // 第三位 sum[2] = (num1[2] ^ num2[2]) ^ add; cout = (num1[2] & num2[2]) | (num2[2] & add) | (num1[2] & add); add = cout; // 第四位 sum[3] = (num1[3] ^ num2[3]) ^ add; cout = (num1[3] & num2[3]) | (num2[3] & add) | (num1[3] & add); add = cout; end endmodule 2 查看电路将verilog文件设置为顶层文件之后再进行操作

本次实验还是比较简单的,让我们对quartus代码的编写和仿真实现和全加器的原理更加熟悉。为之后的学习打下一定的基础。 参考文章:https://blog.csdn.net/molongqishi/article/details/129678242 |

【本文地址】

今日新闻 |

推荐新闻 |

添加代码:

添加代码:

时序仿真结果:

时序仿真结果: