Testbench编写指南(1)基本组成与示例 |

您所在的位置:网站首页 › testbench实例化 › Testbench编写指南(1)基本组成与示例 |

Testbench编写指南(1)基本组成与示例

|

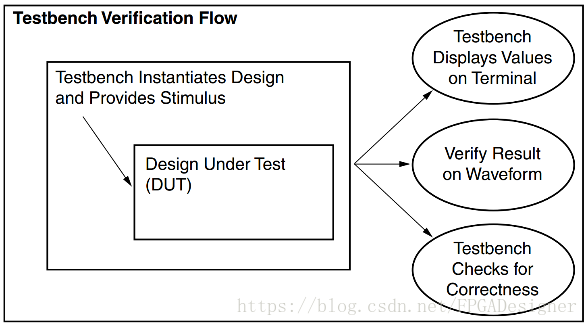

对于小型设计来说,最好的测试方式便是使用TestBench和HDL仿真器来验证其正确性。一般TestBench需要包含这些部分:实例化待测试设计、使用测试向量激励设计、将结果输出到终端或波形窗口便于可视化观察、比较实际结果和预期结果。下面是一个标准的HDL验证流程: 使用系统时钟的设计在TestBench中必须要生成时钟信号,该功能实现起来也非常简单,示例代码如下: parameter ClockPeriod = 10; //方法1 initial begin forever clock = #(ClockPeriod/2) ~ Clock; end //方法2 initial begin always #(ClockPeriod/2) Clock = ~Clock; end 生成测试激励只有给设计激励数据,才能得到验证结果。提供激励的方法有两种,绝对时间激励以仿真时刻0为基准,给信号赋值,示例如下: initial begin reset = 1; load = 0; count = 0; #100 reset = 0; #20 load = 1; #20 count = 1; end‘#’用于指定等待的延迟时间,之后才会执行下一个激励。相对时间激励给信号一个初始值,直到某一事件发生后才触发激励赋值,示例如下: always @ (posedge clk) tb_cnt |

【本文地址】

今日新闻 |

推荐新闻 |

TestBench可以用VHDL或Verilog、SystemVerilog编写,本文以Verilog HDL为例。FPGA设计必须采用Verilog中可综合的部分子集,但TestBench没有限制,任何行为级语法都可以使用。本文将先介绍TestBench中基本的组成部分。

TestBench可以用VHDL或Verilog、SystemVerilog编写,本文以Verilog HDL为例。FPGA设计必须采用Verilog中可综合的部分子集,但TestBench没有限制,任何行为级语法都可以使用。本文将先介绍TestBench中基本的组成部分。