如何编写一个高效的Testbench? |

您所在的位置:网站首页 › testbench主要功能 › 如何编写一个高效的Testbench? |

如何编写一个高效的Testbench?

|

文章目录 写在前面 概述 介绍 构建testbenches 产生时钟信号 提供激励 显示结果 简单的testbenches 自动化验证 编写testbenches的指导方针 高级testbenches技术 用任务(Tasks)分解测试激励 控制仿真中的双向信号 有用的Verilog概念 force和release assign和deassign timescale 读取Memory初始化文件 编码风格 缩进 文件命令 信号命名 注释 设计架构 结论 写在前面在FPGA的开发过程中,验证是一个必不可少的环节,其所占时间有时候甚至还要大于RTL级的开发时间。对于大型设计,设计公司通常都有一整套完整且规范的设计流程。而对于小型设计,我们设计者则可以自己编写一个testbench对设计进行一个简单的功能验证。本文将告诉你:对于小型设计,要如何编写一个高效率的testbench。 本文主要翻译自Xilinx《XAPP199,Writing Efficient Testbenches》,浅蓝色字体为本人理解。 概述本文是为刚接触HDL验证流程和没有丰富的Testbenches编写经验的逻辑设计师编写的。Testbenches是验证HDL设计的主要手段。本文提供了布局和构建高效Testbenches的指导大纲。它还提供了一种算法来为设计开发一个自检的Testbenches。 介绍由于设计规模和复杂性的增加,数字化设计验证已经成为一项越来越困难和艰巨的任务。为了解决这一挑战,验证工程师使用了一些验证工具和方法。对于大型的、数百万门电路级的设计,工程师通常使用一套正式的验证工具。然而,对于较小的设计,设计工程师通常发现带有testbenches的HDL仿真工具是一种最有效的测试模式。 Testbenches已经成为验证HLL(High-Level Language,高级语言)设计的标准方法。通常,Testbenches会实现以下任务: 实例化被测模块(DUT)通过对模型应用测试向量来激励DUT输出结果到终端或波形窗口进行目视检查可以选择将实际结果与预期结果进行比较通常,testbenches是用行业标准的VHDL或Verilog硬件描述语言编写的。Testbenches调用被测模块,然后编写测试激励来激励它以观察期输出。复杂的testbenches会实现一些额外的功能----例如,它们包含用于确定设计的适当设计刺激或将实际结果与预期结果进行比较的逻辑。 本文描述了一个高效的testbenches架构,并提供了一个自检testbenches的示例----它自动地比较实际输出的结果和预期输出的结果。 图1显示了遵循上述步骤的标准HDL验证流程。

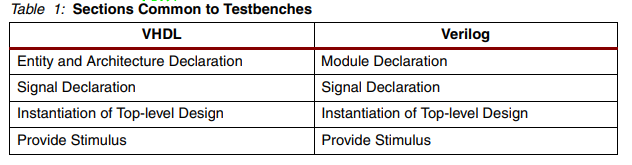

由于testbenches是用VHDL或Verilog编写的,因此testbenches验证过程可以跨平台和工具进行移植。此外,由于VHDL和Verilog是标准的非专有语言,所以在未来的设计中,用VHDL或Verilog编写的验证套件可以轻松地被复用。 testbenches通常包含一下部分:被测模块DUT,测试激励,测试结果比较。DUT是我们编写的RTL代码,也就是我们的功能模块;测试激励是要对DUT进行的测试输入,比如你的功能模块是一个加法器,那么你总得写个测试激励----要给2个加数赋值吧?结果比较模块的实现比较多样化:你可以直接观察波形,看看是不是自己想要的结果;也可以将结果与预期正确的结果自动做比较,如果无误就输出低电平,如果有误就输出高电平;也可以把所有的结果都保存下来,再用脚本自动比对,等等。 构建testbenchestestbenches可以用VHDL或Verilog编写。由于testbenches仅用于仿真,因此它们不受可综合过程中使用的RTL语言子集的语义约束的限制。因此,可以更通用地编写测试testbenches,这会使得它们更具可维护性。 所有的testbenches都包含表1中所示的基本部分。如上所述,testbenches通常还包含额外的功能,例如在终端上显示结果和错误检测功能。

下面的例子展示了一些在testbenches中经常使用的结构。 上面的结构是一个testbenches一定会具备的基本结构,testbenches的编写比较灵活,因为其内容不需要综合,也就是说不需要被映射到具体的电路实现,说白了,就是设计者随心所欲的写激励来作为输入,观察被测的功能模块能否在对应测试激励下,实现符合预期条件的输出。 产生时钟信号使用系统时钟来实现时序逻辑的设计必须生成一个时钟。时钟可以很容易地在Verilog源代码中实现。以下是时钟生成的例子: // Declare a clock period constant. Parameter ClockPeriod = 10; // Clock Generation method 1: initial begin forever Clock = #(ClockPeriod / 2) ~ Clock; end // Clock Generation method 2: initial begin always #(ClockPeriod / 2) Clock = ~Clock; end时钟信号一般使用always和Foever这两个循环来构建,方法很简单:每半个时钟周期,时钟信号翻转一次,这样就能实现周期性的占空比为50%的方波。 提供激励为了获得testbenches的验证结果,必须向被测模块提供测试刺激。在testbenches上使用并行块来提供必要的测试激励。可以采用两种方法:绝对时间激励和相对时间激励。在第一种方法中,仿真数值相对于仿真时间零指定。相比之下,相对时间激励提供初始值,然后等待事件再重新触发激励。根据设计人员的需要,这两种方法可以在一个testbenches中实现。 下面分别提供了绝对时间激励和相对时间激励的例子: (1)绝对时间激励 initial begin Reset = 1; Load = 0; Count_UpDn = 0; #100 Reset = 0; #20 Load = 1; #20 Count_UpDn = 1; end绝对时间激励使用#+时间来定义,比如#20就代表从仿真开始20个时间单位。 (2)相对时间激励 always @ (posedge clock) TB_Count |

【本文地址】

今日新闻 |

推荐新闻 |