IP核的创建(以PLL实验为例) |

您所在的位置:网站首页 › simulink锁相环pll用法 › IP核的创建(以PLL实验为例) |

IP核的创建(以PLL实验为例)

|

操作步骤: ① 启动 Quartus II 17.1 ,创建 ip_pll 工程。新建后的工程如图1所示。

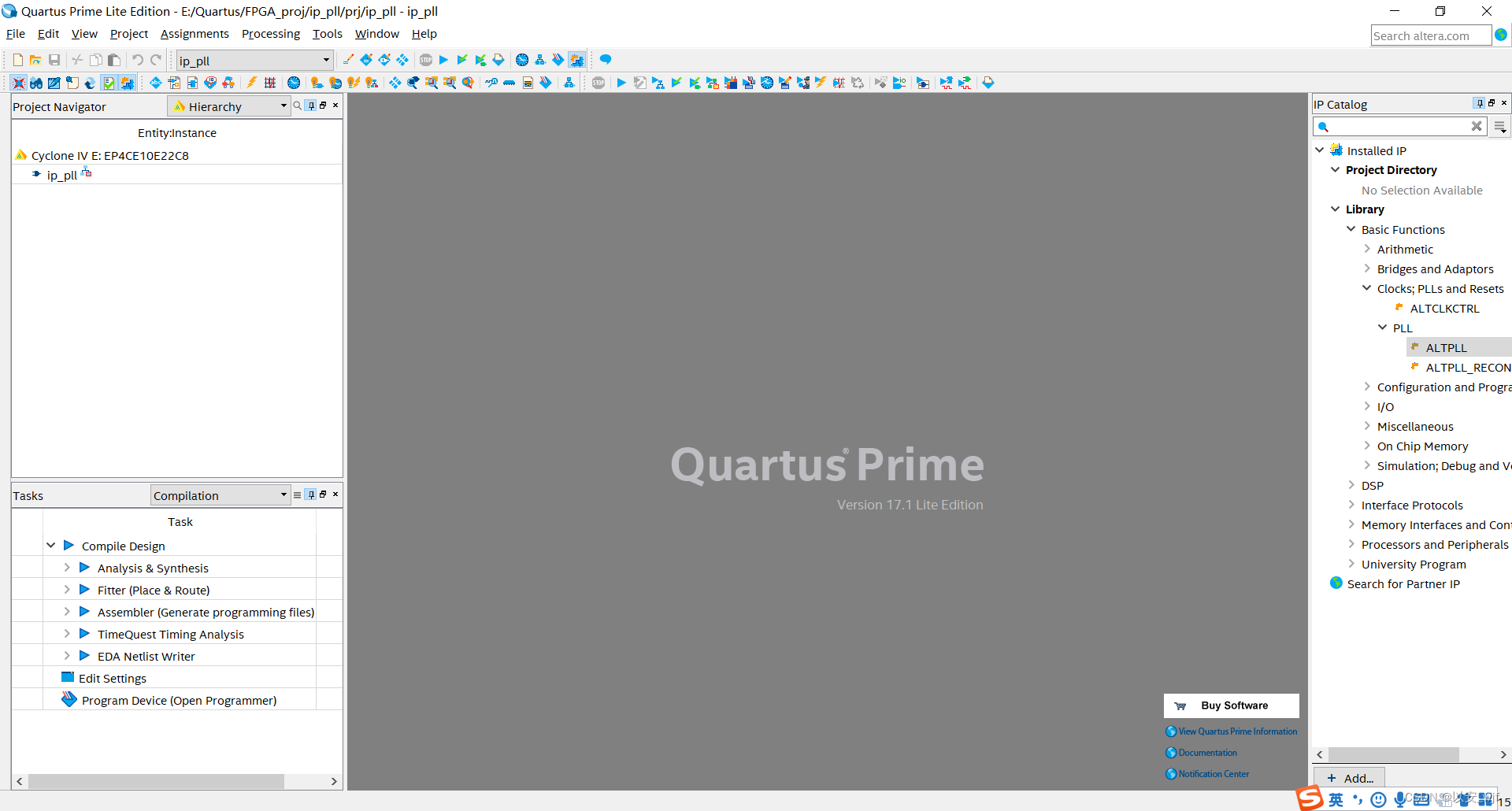

图1 工程新建完成界面 ② 工程创建好了之后,接下来就是创建 PLL IP 核。选择Tools→ IP Catalog,如图2所示。

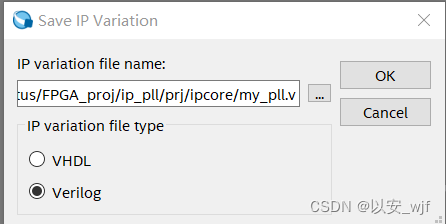

③ 此时右侧打开 IP Catalog 界面,依次单击 Library→Basic Functions→Clocks;PLLs and Reset→PLL→ATLPLL,找到锁相环所在位置。 ④ 双击ATLPLL,弹出如图3所示的 Save IP Variation 对话框.。为 IP 核选择保存的路径及名程,首先在工程所在路径prj文件夹下创建一个文件夹ipcore,用于存放工程中用到的 IP 核。这里我将IP核命名为my_pll,选中Verilog,单击OK按钮。此时系统会自动进入 PLL 的设置导向,如图4所示。

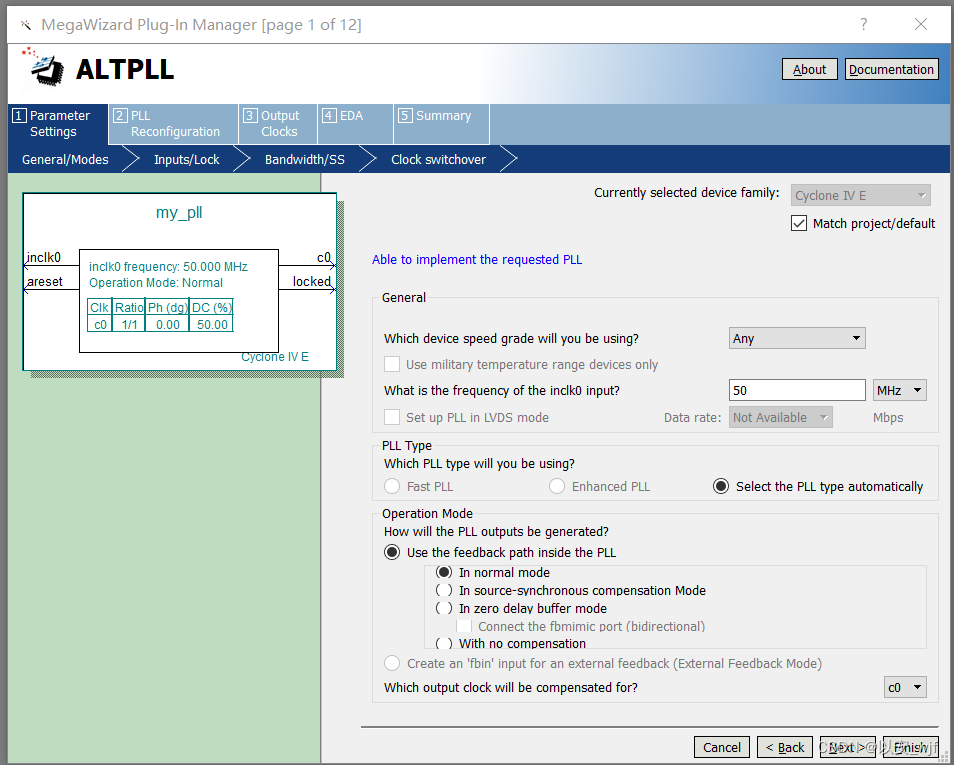

图3 图4 ⑤ 在图4中输入时钟频率(所用开发板的晶振时钟频率或外部时钟频率)。由于我用的开发板的晶振时钟频率为50MHz,因此,在图4所示界面中修改成50MHz,其他的默认不动,单击Next,进入图5所示界面。

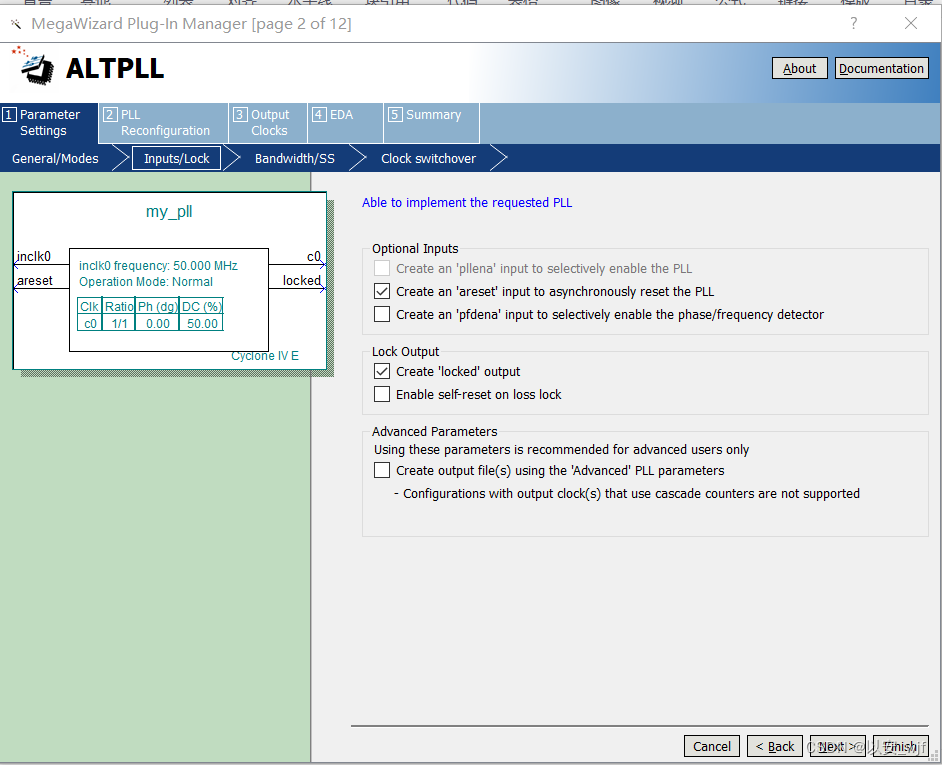

图5 ⑥ 图5中第一个打 √ 的是设置是否使用异步复位来复位锁相环,第二个打 √ 的是是否输入 LOCK 信号,LOCK信号拉高表示锁相环开始稳定输出时钟信号,在此保持默认(注意:如果没有打√,一定要记得勾选),连续单击Next,直至弹出图6所示的界面。

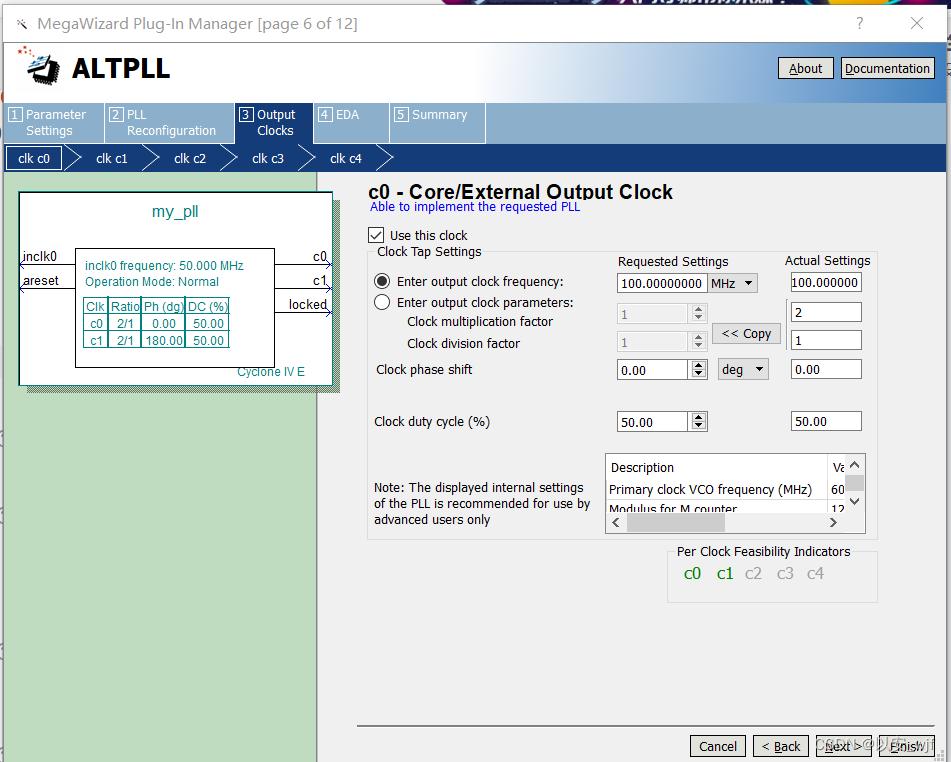

图6 第一个输出时钟c0的配置界面 ⑦ 图6是配置输出时钟的界面,设置第一个时钟频率。在Requested Settings 文本框中直接输入我们需要的时钟频率100MHz;在Clock phase shift 下拉列表框中输入时钟的相位偏移(调节相位),这里保持默认0即可;在Clock duty cycle(%)下拉列表框中设置时钟的占空比,时钟占空比一般为50%,这里保持默认50即可,然后单击Next,进入图7所示的界面。

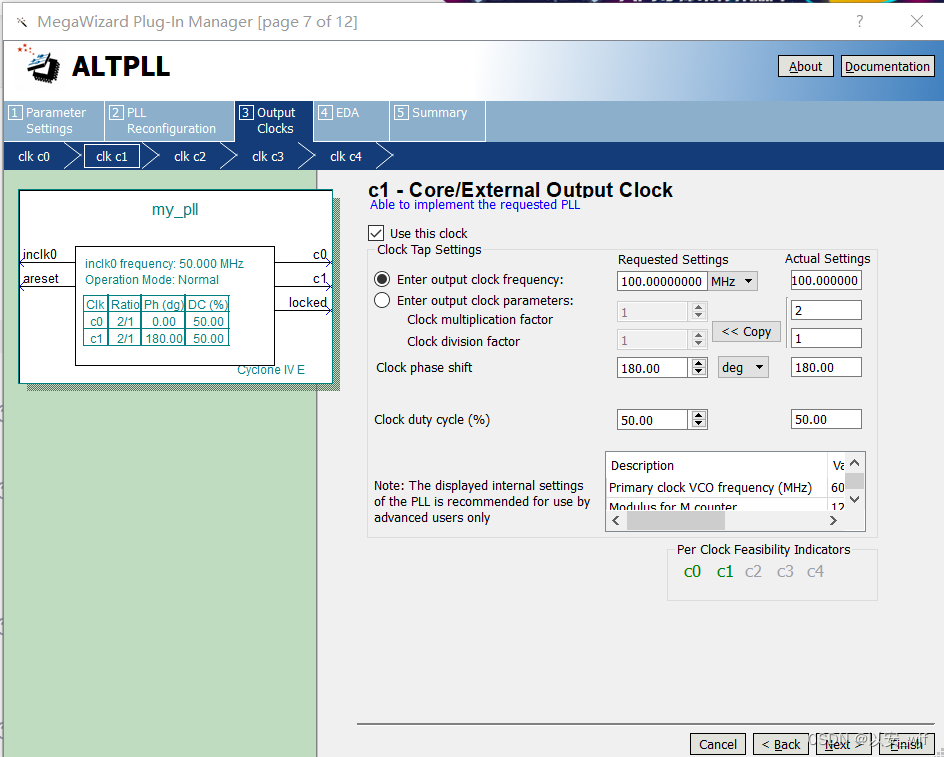

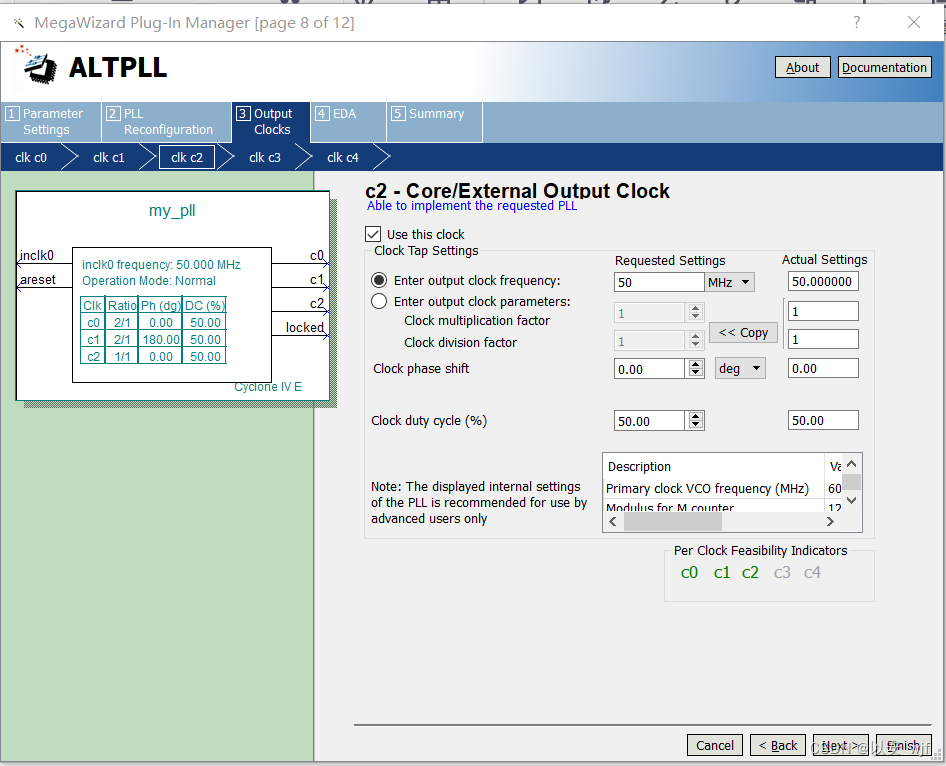

图7 第二个输出时钟c1的配置界面 ⑧ 在图7中设置第二个时钟频率,使能c1时钟信号,将c1时钟设置为100MHz,时钟相位设置为180(为了演示时钟相位的作用) ,然后单击Next,进入图8所示的界面,设置第三个时钟频率c2为50MHz,再单击Next,进入图9所示的界面,设置第四个时钟频率c3为25MHz。 图8 第三个输出时钟c2的配置界面

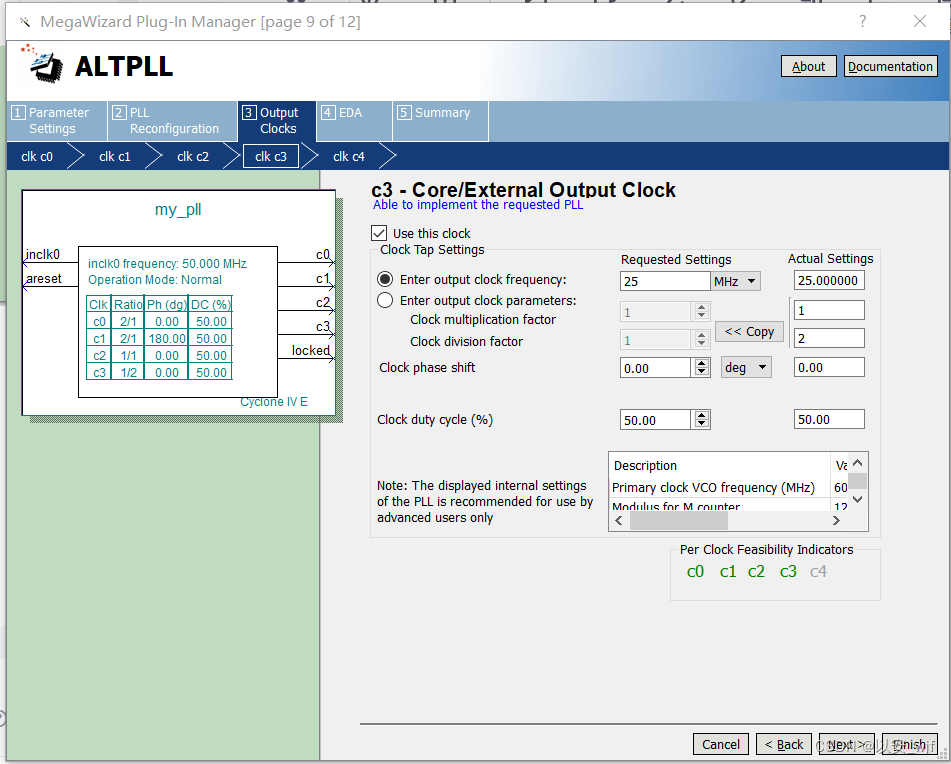

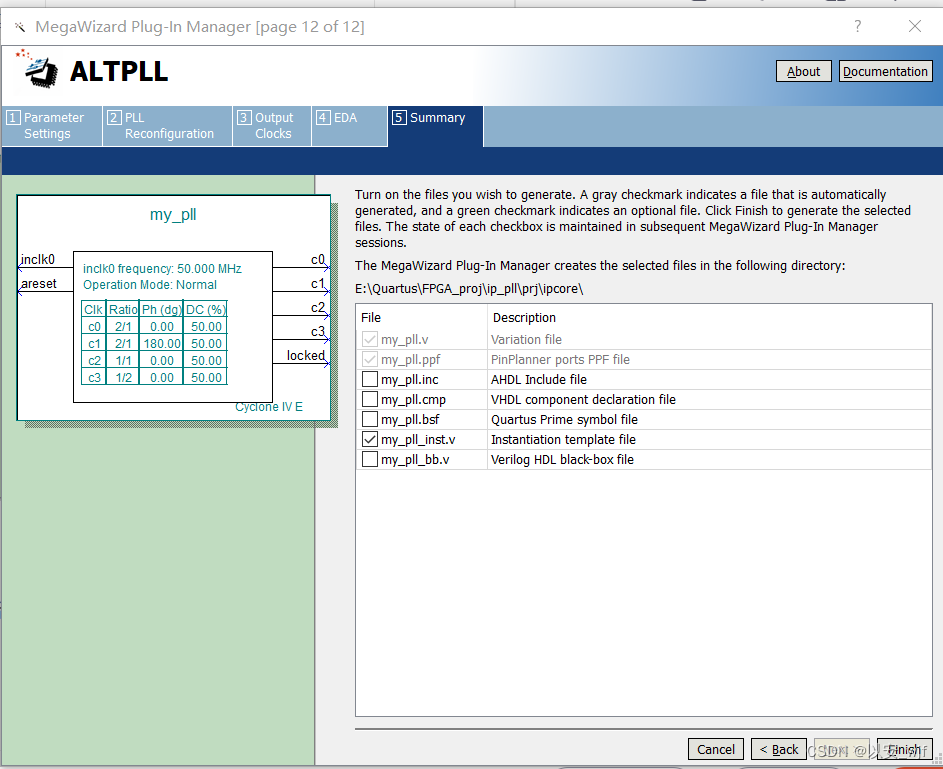

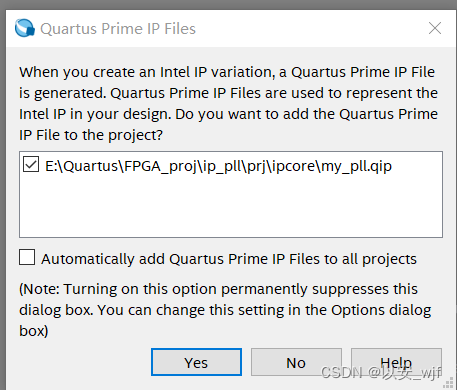

图9 第四个输出时钟c3的配置界面 ⑨ 单击Next,直至出现图10所示的界面,选中文件my_pll_inst.v(文件my_pll_inst.v是调用IP核的端口),单击Finish按钮完成整个IP核的创建。接下来Quartus II 软件会在ipcore文件下创建ALTPLL的IP核文件,然后询问我们是否添加至工程,单击Yes按钮,如图11所示。

图10

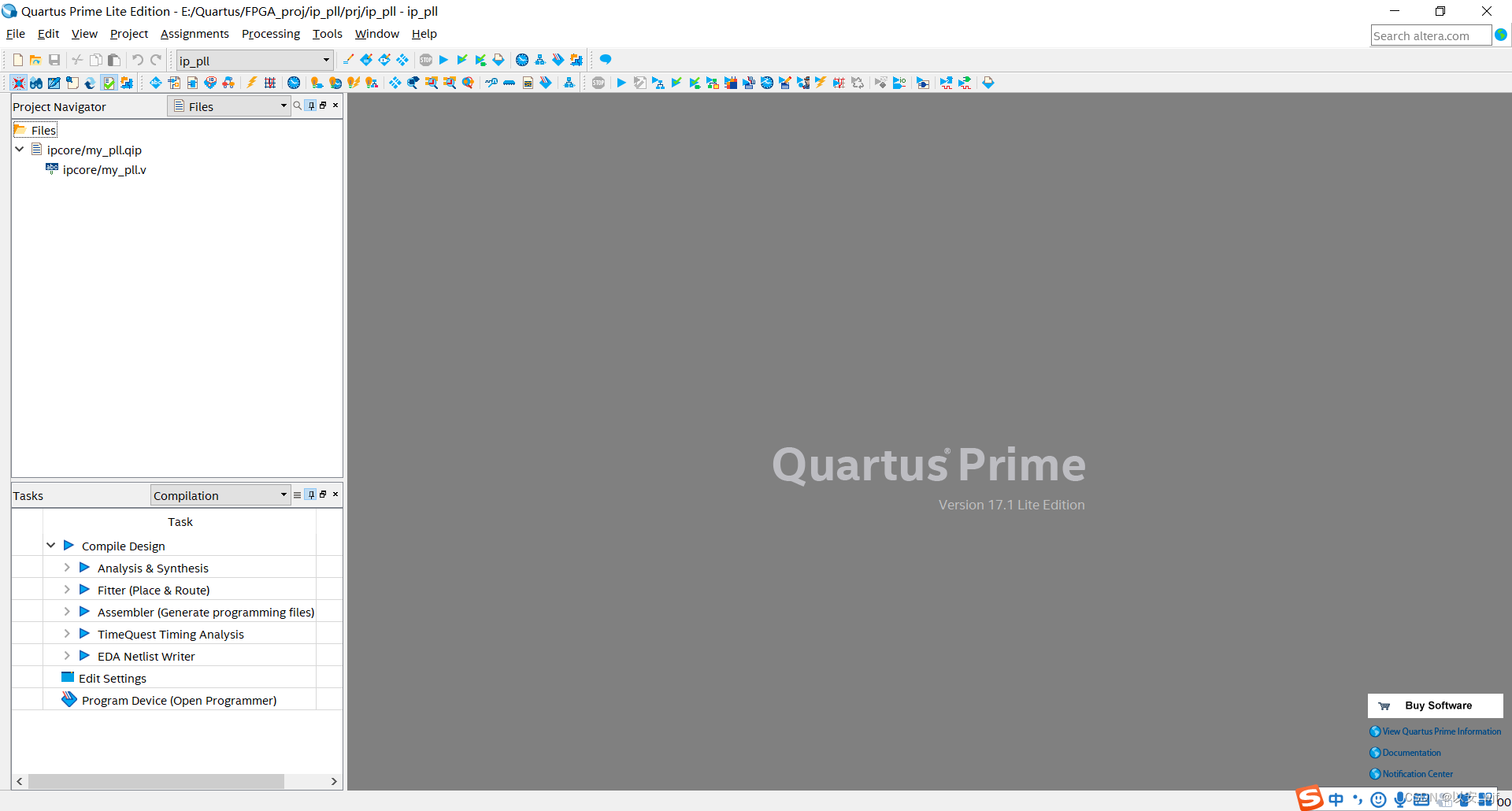

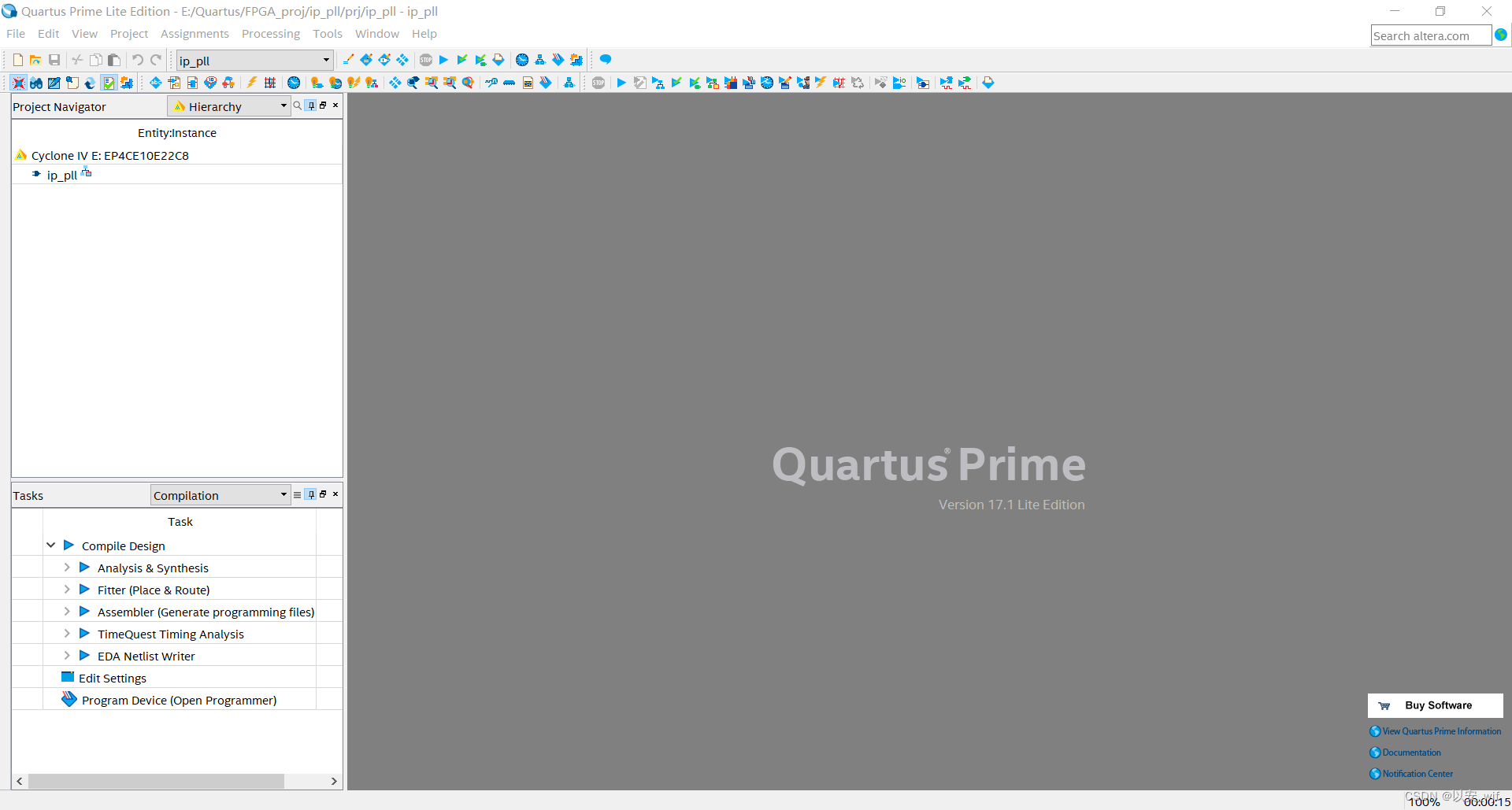

图11 ⑩ PLL IP 核添加到工程中的界面如图12左上角 Files 下所示。

图12 至此,ALTPLL IP 核的创建就完成啦!!! |

【本文地址】

今日新闻 |

推荐新闻 |

图2

图2