基于FPGA的DDS信号发生器的设计与实现 |

您所在的位置:网站首页 › fpga波形发生器原理图 › 基于FPGA的DDS信号发生器的设计与实现 |

基于FPGA的DDS信号发生器的设计与实现

|

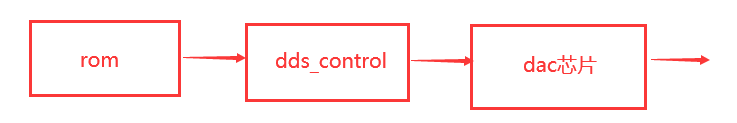

一、实现环境 软件:Quartus II 13.0 硬件:MP801 二、DDS基本原理 DDS(Direct Digital Synthesizer)即数字合成器,是一种新型的频率合成技术,具有相对带宽大,频率转换时间短,分辨率高和相位连续性好等优点。较容易实现频率、相位及幅度的数控调制,广泛应用于通信领域。DDS的实现示意图如下图所示:

1、将需要合成的信号的数据存储在rom中,合成待输出信号的方法请参考:https://www.cnblogs.com/qidaiymm/p/5692253.html 2、dds_control实现的功能是将存储在rom中的待合成的信号的数据按照一定的规则取出来: dds_control主要由相位累加和频率累加来实现,简单的说,通过控制相位累加和频率累加来实现从rom中取出不同时刻的数据。 (1)相位累加器位数为N位(24~32),相位累加器把正弦信号在相位上的精度定义为N位,其分辨率位1/2N ,决定一个波形的起始时刻在哪个点; (2)频率累加器用来控制每隔几个点从rom中取一个数据,决定一个波形的频率; (3)若DDS的时钟频率为Fclk ,频率控制字fword = 1,则输出频率为 Fout = Fclk/2N,这个频率相当于“基频”,若fword = B,则输出频率 Fout = B * Fclk/2N。因此理论上由以上三个参数就可以得出任意的 fo 输出频率,且可以得出频率分辨率由时钟频率和累加器的位数决定的结论。当参考时钟频率越高,累加器位数越高,输出频率分辨率就越高。 3、从FPGA中出来的信号都是数字信号(dds_control输出的信号都为数字信号),需要通过dac芯片来将数字信号转换为模拟信号,这样将dac芯片输出的信号接入到示波器中,才能看到波形; 4、举例说明频率控制和相位控制:

如上图所示,这个是一个由33个点构成的正弦波信号,(rom_addr,rom_data),纵坐标为存储在rom中的正弦波信号,横坐标为 dds_control 生成的地址信号。fre_acc = fre_acc + fword,当 fword = 1 时,fre_acc 则会将从 1 -33 全部地址取到(如 1、2、3、4、5、6......33),而将对应的纵坐标的点全部输出到DAC芯片,假设此时DAC芯片输出的正弦波信号频率为 f。那么,当 fword = 2,则每隔一个地址单位输出一个存储在rom中的正弦波数据(如1、3、5、7、9......33),此时DAC芯片输出的正弦波信号的频率则变为 2f。 相位累加器则是将整个波形按照一定的地址信号的位置向右平移来改变相位,体现在数值上则是加上每个地址信号加上一个pword。 三、工程实现 设计一个单通道的DDS信号发生器,根据改变FPGA开发板上的拨码开关来控制DAC输出的信号是正弦波、方波、三角波、锯齿波,通过按键来控制DAC芯片输出的信号的频率和相位。 1、RTL视图

2、按照RTL视图分析各个模块的代码 (1)select 模块: 拨码开关 sw0: 往上拨则输出 正弦波 key1 : 调节频率,有四个档位,每按一下换一个频率; sclk:系统时钟50MHz 拨码开关 sw1: 往上拨则输出 方波 key2:调节相位,有四个档位,每按一下换一个相位; s_rst_n:系统复位 拨码开关 sw2: 往上拨则输出 锯齿波 en :使能信号 拨码开关 sw3: 往上拨则输出 三角波 select 代码   1 // *********************************************************************************

2 // Project Name : select

3 // Email :

4 // Create Time : 2020/06/24 18:44

5 // Module Name : select.v

6 // editor : qing

7 // Version :

8 // *********************************************************************************

9

10 module select(

11 input sclk ,

12 input s_rst_n ,

13

14 input sw0 ,

15 input sw1 ,

16 input sw2 ,

17 input sw3 ,

18

19 input key1 ,

20 input key2 ,

21

22 output reg[ 3:0] rom_select ,

23 output reg[31:0] fword ,

24 output reg[31:0] pword

25 );

26

27 //========================================================================\

28 // =========== Define Parameter and Internal signals ===========

29 //========================================================================/

30

31 reg [3:0] cnt1 ;

32 reg [3:0] cnt2 ;

33

34 //=============================================================================

35 //**************************** Main Code *******************************

36 //=============================================================================

37

38 always @(posedge sclk or negedge s_rst_n) begin // cnt1

39 if(!s_rst_n)

40 cnt1

1 // *********************************************************************************

2 // Project Name : select

3 // Email :

4 // Create Time : 2020/06/24 18:44

5 // Module Name : select.v

6 // editor : qing

7 // Version :

8 // *********************************************************************************

9

10 module select(

11 input sclk ,

12 input s_rst_n ,

13

14 input sw0 ,

15 input sw1 ,

16 input sw2 ,

17 input sw3 ,

18

19 input key1 ,

20 input key2 ,

21

22 output reg[ 3:0] rom_select ,

23 output reg[31:0] fword ,

24 output reg[31:0] pword

25 );

26

27 //========================================================================\

28 // =========== Define Parameter and Internal signals ===========

29 //========================================================================/

30

31 reg [3:0] cnt1 ;

32 reg [3:0] cnt2 ;

33

34 //=============================================================================

35 //**************************** Main Code *******************************

36 //=============================================================================

37

38 always @(posedge sclk or negedge s_rst_n) begin // cnt1

39 if(!s_rst_n)

40 cnt1 |

【本文地址】

今日新闻 |

推荐新闻 |