FPGA数字信号处理(十二)滑动平均滤波器 |

您所在的位置:网站首页 › fpga数字滤波后波形不稳定 › FPGA数字信号处理(十二)滑动平均滤波器 |

FPGA数字信号处理(十二)滑动平均滤波器

|

上一篇介绍了数字通信系统中ASK解调技术的FPGA实现。在ASK解调系统中,需要对低通滤波器提取出的基带包络信号做判决输出,本文将介绍其中涉及到的判决门限问题,以及在FPGA中的实现方法。主要介绍了如何使用滑动平均滤波器求得信号均值。 判决门限由上一篇可知,LPF输出的基带包络信号包含有直流分量。2ASK信号只有2种电平状态,因此只需要将基带波形的直流分量作为判决门限即可。4ASK信号有4种电平状态:最大幅度的0、1/3、2/3、1倍,选取中间值1/6、1/2、5/6作为判决门限正确率最高。可见,无论是2ASK还是4ASK,都需要先获得直流分量。 本文将讲述ASK解调系统中判决门限的选择问题,以及FPGA的设计。由于ASK解调出的基带信号含有直流分量,因此需要这样处理。对于2FSK、BPSK这种不含直流分量的解调系统而言,判决门限直接选择0即可。 滑动平均在FPGA中,求取信号的直流分量即为求信号的均值,参与均值运算的数据越多,则计算准确度越高,消耗的资源也越大。 最方便实现的求均值方法便是滑动平均滤波器,之所以称之为滤波器是因为该算法本身有一种保留低频分量、滤除高频分量的特性。如3点滑动平均滤波器的输出y(n)=[x(n-2)+x(n-1)+x(n)]/3。滑动平均滤波器的频率响应与CIC滤波器的完全一致,系数都是1(CIC滤波器参考本系列16~19篇)。 上述示例x(n)的每个取样点权值相同,都为1/3。也可以为每个取样点选择不同的权值,即为所说的加权滑动平均滤波器,将在后面的文章中叙述。 FPGA设计在Vivado开发环境下完成256点滑动平均滤波器的设计。模块接口如下: `timescale 1ns / 1ps //-------------------------------------------------------- // ASK解调系统,符号判决模块 //-------------------------------------------------------- module gate ( input rst, input clk, input signed [13:0] din, //LPF输出的基带信号包络 output signed [13:0] mean //基带信号的直流分量 );使用一组256个寄存器移位存储基带信号数据,即求平均值时共选取256个数据进行运算。代码如下: //-------------------------------------------------------- // 256级寄存器移位缓存数据 //-------------------------------------------------------- reg [13:0] din_reg [255:0]; integer i, j; always @ (posedge clk or posedge rst) if (rst) //复位清0 for (i=0; i{8{din_reg[255][13]}},din_reg[255]}; assign mean = sum[21:8]; //右移8bit等效为÷256 endmodule这样便得到了基带信号的直流分量。对于2ASK解调,这个值可以直接作为判决门限;对于4ASK解调,还需要由直流分量(即1/2)得到1/6和5/6两个判决门限。这会涉及到常系数的乘除法,对于FPGA而言,这两种运算很消耗资源(尤其是除法),可以采用在https://blog.csdn.net/fpgadesigner/article/details/80710344 用过的移位相加的方法来代替。 仿真与工程下载将判决门限模块加入到ASK解调系统的工程中进行仿真。对2ASK信号解调的仿真效果如下图所示: 不过可以预料到的是,在初始阶段,当数据点数不足256个时(不够的值会采用默认值0填充),计算得到的直流分量会有相当大的误差,这在应用于解调系统时会造成一定的错误,具体情况可参考本系列第11篇的仿真。 |

【本文地址】

今日新闻 |

推荐新闻 |

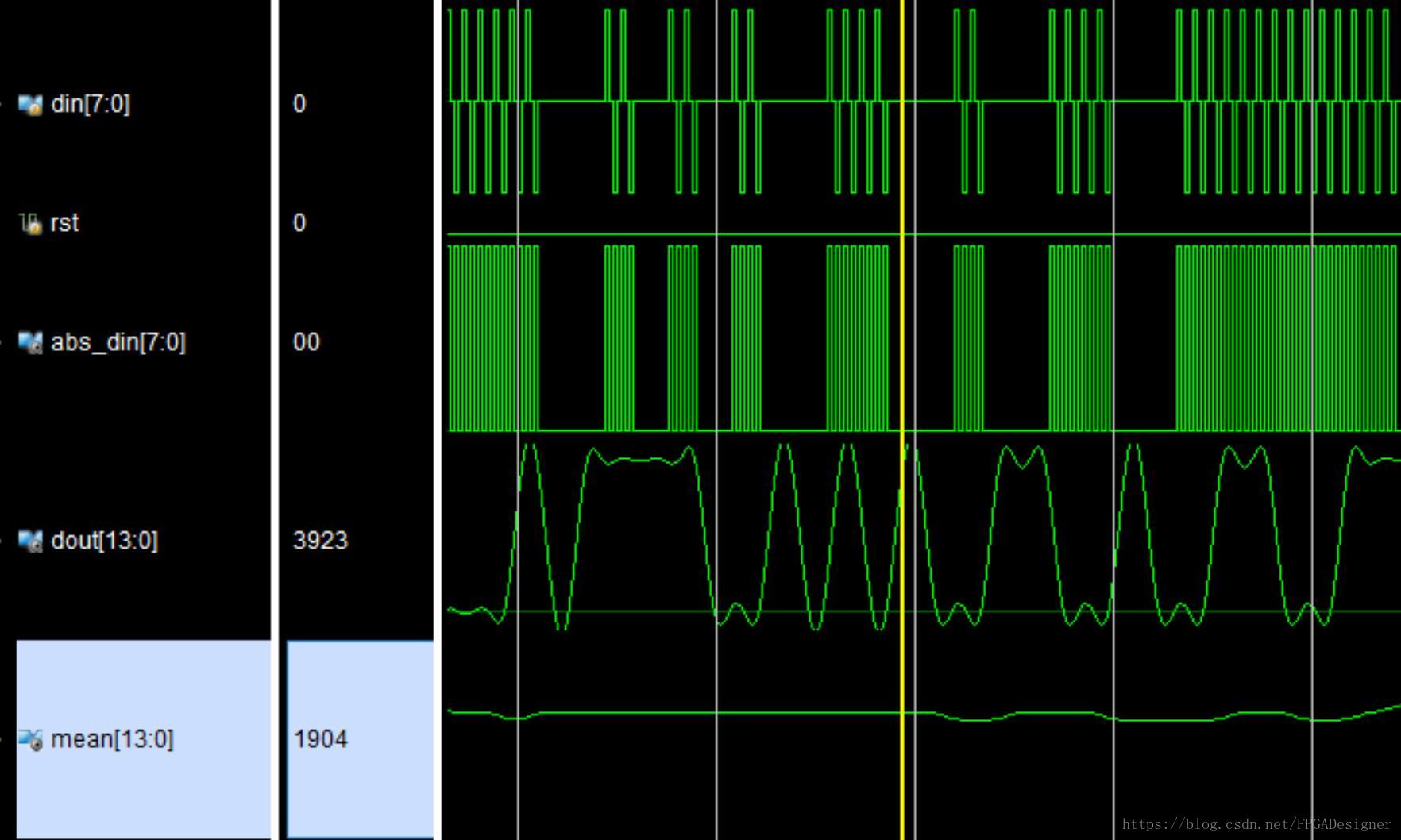

看到黄色标签处的基带信号最大值为3923,此时的直流分量为1904,可以作为判决门限。直流分量的值一直都比较稳定。4ASK信号解调的仿真效果如下图所示:

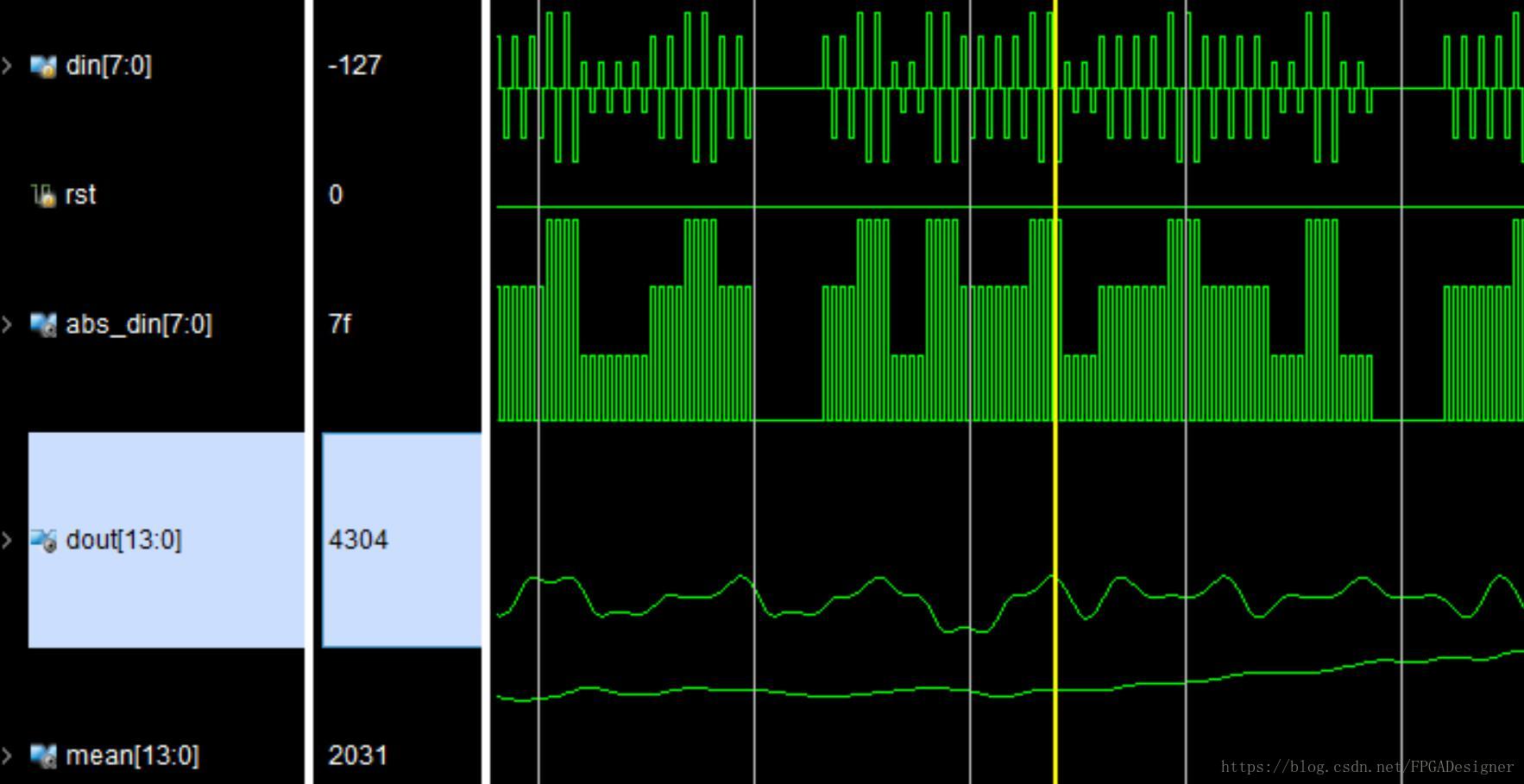

看到黄色标签处的基带信号最大值为3923,此时的直流分量为1904,可以作为判决门限。直流分量的值一直都比较稳定。4ASK信号解调的仿真效果如下图所示:  看到黄色标签处的基带信号最大值为4303,此时的直流分量为2031,可以作为判决门限。

看到黄色标签处的基带信号最大值为4303,此时的直流分量为2031,可以作为判决门限。