FPGA 的数字信号处理:Verilog 实现简单的 FIR 滤波器 |

您所在的位置:网站首页 › fir数字滤波器设计课程设计 › FPGA 的数字信号处理:Verilog 实现简单的 FIR 滤波器 |

FPGA 的数字信号处理:Verilog 实现简单的 FIR 滤波器

|

该项目介绍了如何使用 Verilog 实现具有预生成系数的简单 FIR 滤波器。  绪论

绪论

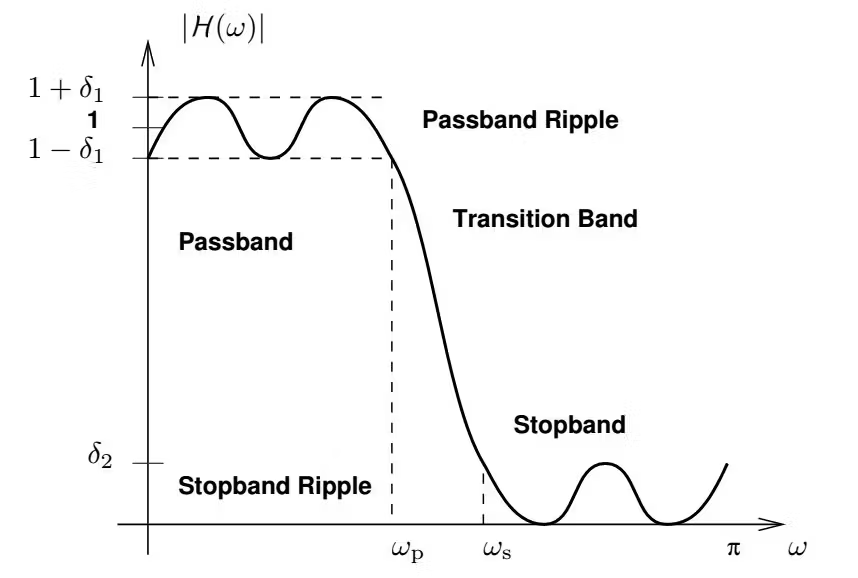

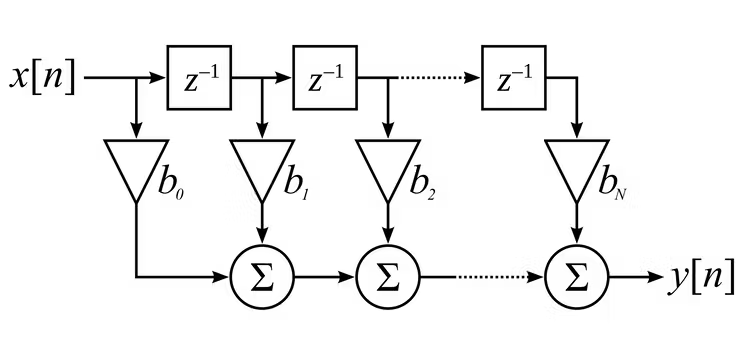

不起眼的 FIR 滤波器是 FPGA 数字信号处理中最基本的模块之一,因此了解如何将具有给定抽头数及其相应系数值的基本模块组合在一起非常重要。因此,在这个关于 FPGA 上 DSP 基础实用入门的教程中,将从一个简单的 15 抽头低通滤波器 FIR 开始,在 Matlab 中为其生成初始系数值,然后转换这些值用于编写 Verilog 模块。 有限脉冲响应或 FIR 滤波器定义为脉冲响应在特定时间段内稳定为零值的滤波器。脉冲响应稳定到零所花费的时间与滤波器阶数(抽头数)直接相关,滤波器阶数是 FIR 的基础传递函数多项式的阶数。FIR 的传递函数不包含反馈,因此如果输入一个值为 1 的脉冲,然后输入一串零值,输出将只是滤波器的系数值。 滤波器的作用基本都是用于信号调节,主要集中在选择滤除或允许通过哪些频率。最简单的例子之一是低通滤波器,它允许低于某个阈值(截止频率)的频率通过,同时大大衰减高于该阈值的频率,如下图所示。

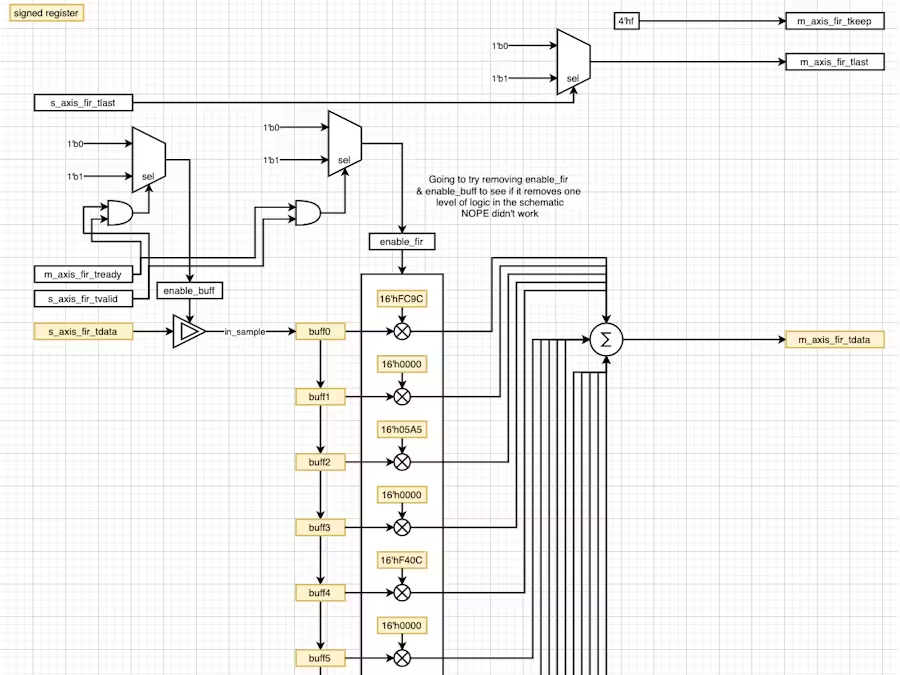

该项目的主要重点是在 HDL(具体为 Verilog)中实现 FIR,它可以分解为三个主要逻辑组件:一个循环缓冲器,用于将每个样本计时到适当地考虑了串行输入的延迟、每个抽头系数值的乘法器以及每个抽头输出的求和结果的累加器。

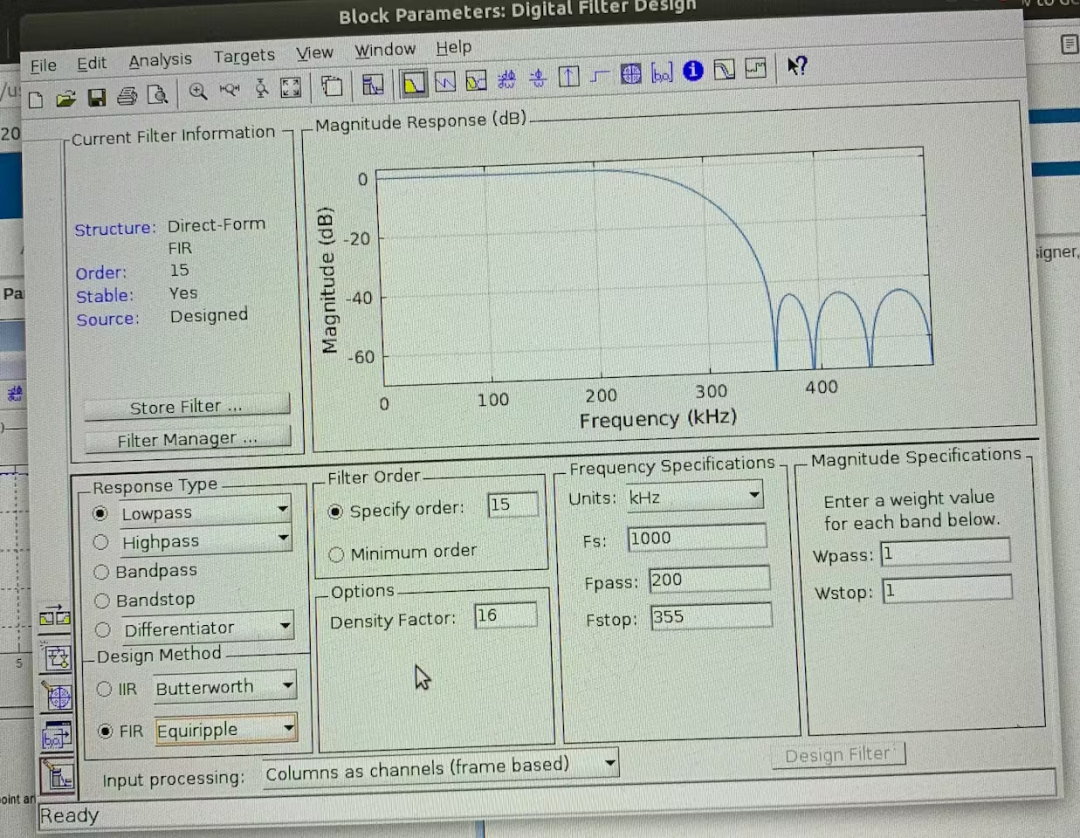

由于本项目专注于 FPGA 逻辑中 FIR 的设计机制,所以只是使用 Simulink 中的 FDA 工具和 Matlab 为低通滤波器插入一些简单参数,然后使用生成的系数值放到 Verilog 模块中完成滤波器的设计(在后面的步骤中完成)。

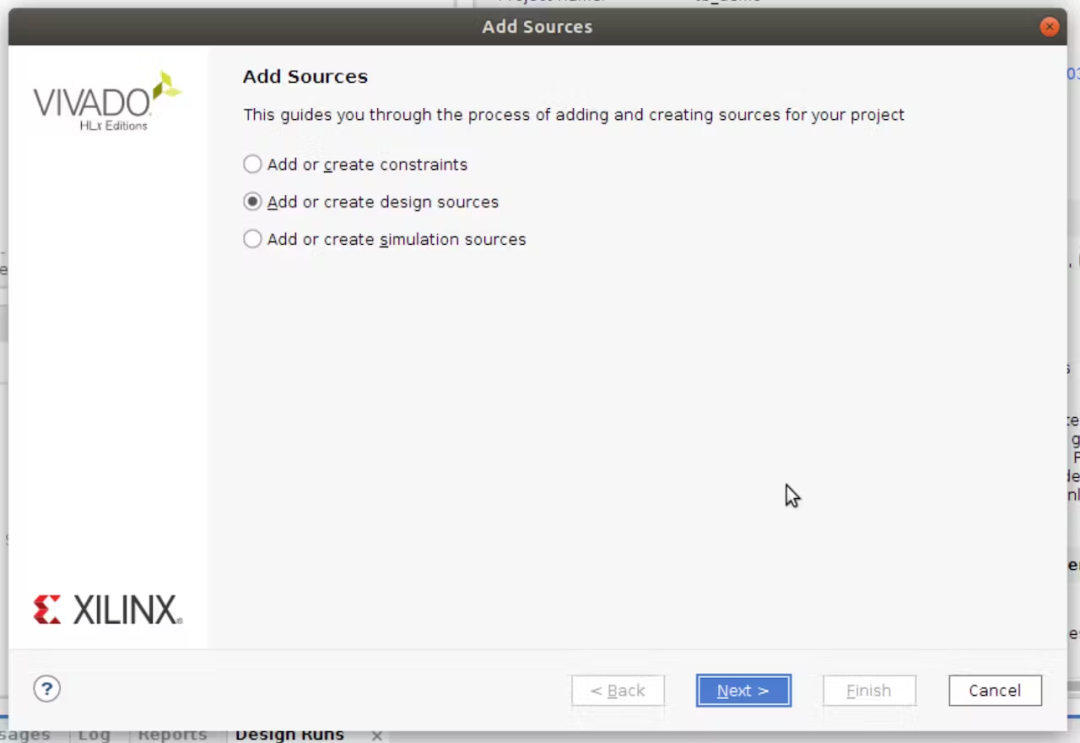

选择实现一个简单的 15 抽头低通滤波器 FIR,采样率为 1Ms/s,通带频率为 200kHz,阻带频率为 355kHz,得到以下系数: -0.0265 0 0.0441 0 -0.0934 0 0.3139 0.5000 0.3139 0 -0.0934 0 0.0441 0 -0.0265 为 FIR 模块创建设计文件在 Vivado 项目中添加源文件。

在确定 FIR 的顺序(抽头数)并获得系数值后,接下来需要定义的下一组参数就是输入样本、输出样本和系数本身的位宽。 对于这个 FIR,选择将输入样本和系数寄存器设置为 16 位宽,并将输出样本寄存器设置为 32 位,因为两个 16 位值的乘积是一个 32 位值(两个值的宽度相乘得到乘积的宽度,所以如果选择了 8 位抽头的 16 位输入样本,那么输出样本将为 24 位宽)。 这些值也都是带符号的,因此 MSB 用作符号位,在选择输入样本寄存器的初始宽度时一定要记住这一点。要在 Verilog 中将这些值设置为有符号数据类型,使用关键字signed : reg signed [15:0] register_name;接下来要解决的是如何在 Verilog 中处理系数值,小数点值需要转换为定点值。由于所有系数值都小于 1,因此寄存器的所有 15 位(总共 16 位,MSB 是有符号位)都可以用于小数位。通常,必须决定要将寄存器中的多少位用于数字的整数部分与数字的小数部分。因此,转换分数值抽头的数学是:(fractional coefficient value)*(2^(15))该乘积的小数值被四舍五入,并且如果系数为负,则计算该值的二进制补码: tap0 = twos(-0.0265 * 32768) = 0xFC9C tap1 = 0 tap2 = 0.0441 * 32768 = 1445.0688 = 1445 = 0x05A5 tap3 = 0 tap4 = twos(-0.0934 * 32768) = 0xF40C tap5 = 0 tap6 = 0.3139 * 32768 = 10285.8752 = 10285 = 0x282D tap7 = 0.5000 * 32768 = 16384 = 0x4000 tap8 = 0.3139 * 32768 = 10285.8752 = 10285 = 0x282D tap9 = 0 tap10 = twos(-0.0934 * 32768) = 0xF40C tap11 = 0 tap12 = 0.0441 * 32768 = 1445.0688 = 1445 = 0x05A5 tap13 = 0 tap14 = twos(-0.0265 * 32768) = 0xFC9C现在我们终于准备好关注 FIR 模块的逻辑,第一个是循环缓冲区,它引入串行输入样本流并为滤波器的 15 个抽头创建一个包含 15 个输入样本的数组。 always @ (posedge clk) begin if(enable_buff == 1'b1) begin buff0 |

【本文地址】

今日新闻 |

推荐新闻 |