PDS软件使用指南(二)建立工程与IO管脚分配 |

您所在的位置:网站首页 › ep1c6q240c8n引脚分配 › PDS软件使用指南(二)建立工程与IO管脚分配 |

PDS软件使用指南(二)建立工程与IO管脚分配

|

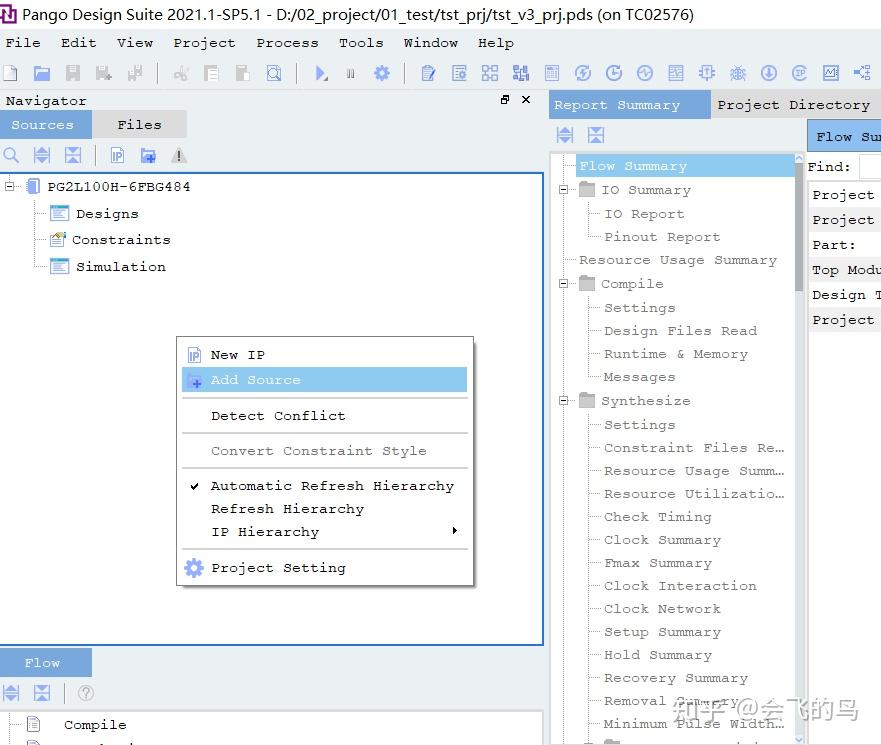

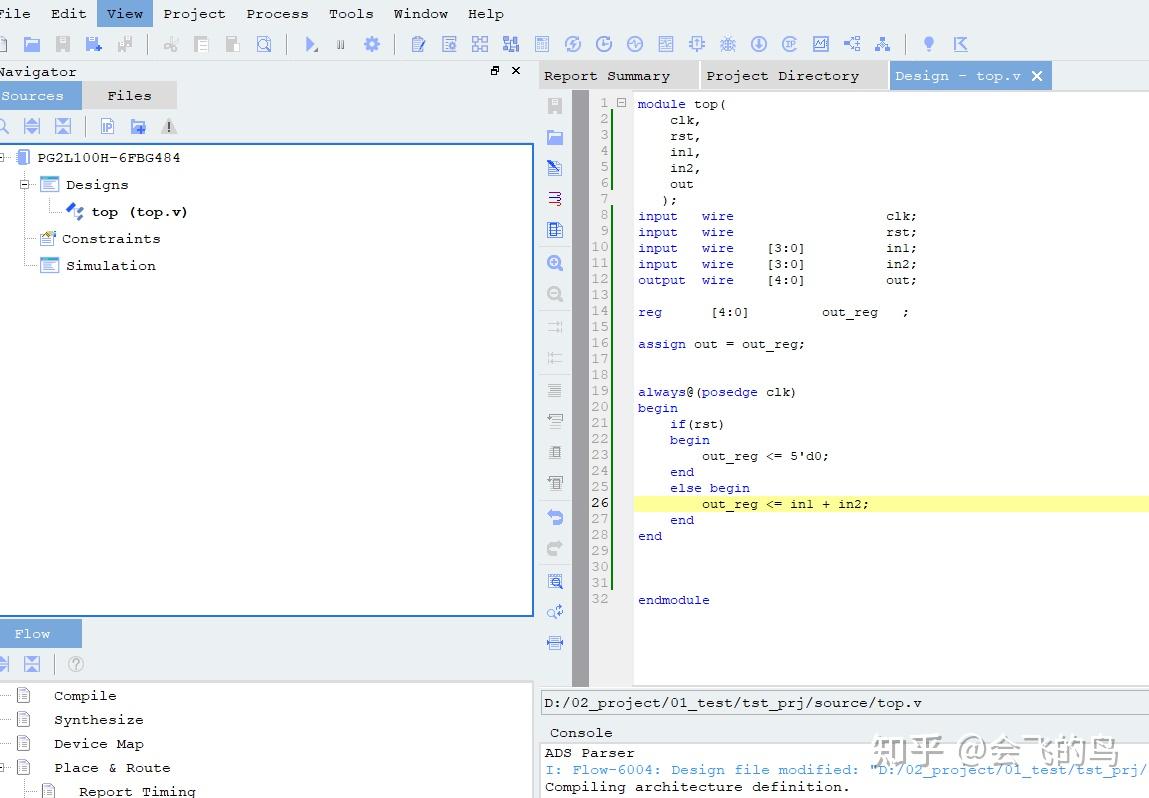

参考资料:PDS安装目录下doc文件夹《Pango_Design_Suite_User_Guide.pdf》。 该参考资料对PDS软件讲的非常详细,用户可以通过资源管理器直接打开该文件,或者打开PDS软件首页,点击open user guide。   一、建立工程打开PDS软件,上图中可以点击New Project,开始建立工程。 一、建立工程打开PDS软件,上图中可以点击New Project,开始建立工程。 2. 点击Next,在新出现的对话框中,填上自己新建工程名字,并选择该新建工程所在的路径,然后点击Next。  3. 第三步是是否需要综合工具,我们选择第一个选项,需要,然后点击Next。  4. 第四步,看你是否有需要添加.v文件,由于这一步在新建工程之后也可以操作,所以直接点击Next。  5. 询问建立的工程是否有已经存在的IP,我们这里没有,所以不用管,直接点击Next。  6. 然后询问是否有约束文件,我们这里没有,所以也略过,选择Next。  7. 这一步,需要用户选择使用紫光fpga器件的类型,现在紫光fpga器件有compact系列(也就是cpld),logos系列、logos2系列、titan系列和titan2系列,想详细了解的可以去官网搜一下datasheet。在这里,我们随便选择一个器件类型,然后选择综合工具ADS(我这个版本的PDS只有ADS综合工具),点击Next。  8. 最后弹出的一个窗口是对你所建立工程的一个总结,用户可以校验一下,如果有问题,可以点击Back,进行修改,没问题的话,就点击Finish。  9. 这是用户点击finish之后出现的窗口,可以看到新建的工程没有任何代码,所以接下来需要我们建立verilog文件。  10. 右击左侧窗口空白处,选择Add Source。  11. 点击Next  12. 点击Create File。  13. 输入新创建的verilog文件的名字以及保存目录。  14. 这里可以同时创建多个Verilog文件,创建好之后,点击两次ok,就成功了。  15. 创建好verilog文件之后,可以在右侧子窗口编写代码,编写完成之后,下一步就是对工程进行编译了,编译的小窗口在大窗口的左下侧。  16. 双击flow窗口的compile,可以对工程进行编译、综合等操作,如果代码有错误或者警告,右下侧message窗口可显示线索。  二、IO管脚分配新建工程,compile阶段完成之后,在PDS工具Tools菜单下,打开UCE工具。 二、IO管脚分配新建工程,compile阶段完成之后,在PDS工具Tools菜单下,打开UCE工具。 2. 在新出现的窗口,切换到Device,然后点击IO图标,就会出现对工程顶层文件IO管脚分配界面。  3. 查看芯片原理图,根据实际结果,对clk、复位以及其它IO引脚进行分配。  4. 分配完IO引脚之后,点击保存。  5. UCE工具会生成fdc文件,选择目录,然后点击保存。  6. 保存之后,fdc文件会自动添加到工程中。

|

【本文地址】

今日新闻 |

推荐新闻 |