计算机组成原理 |

您所在的位置:网站首页 › dram存储芯片是什么意思啊 › 计算机组成原理 |

计算机组成原理

|

计算机组成原理 —— 存储系统(DRAM和SRAM)

DRAM和SRAMDRAM的刷新DRAM地址复用ROM(Read-Only Memory(只读存储器))

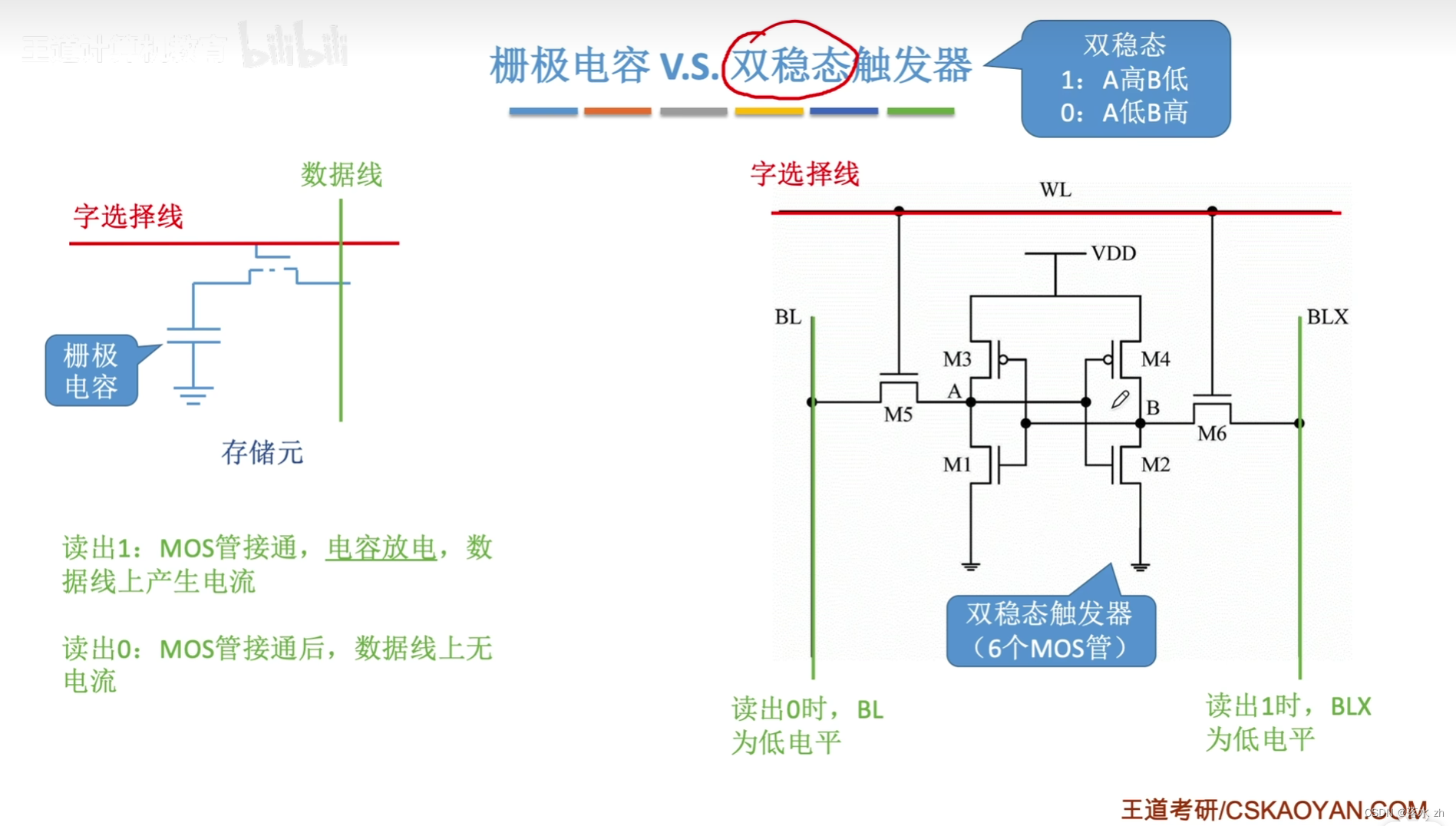

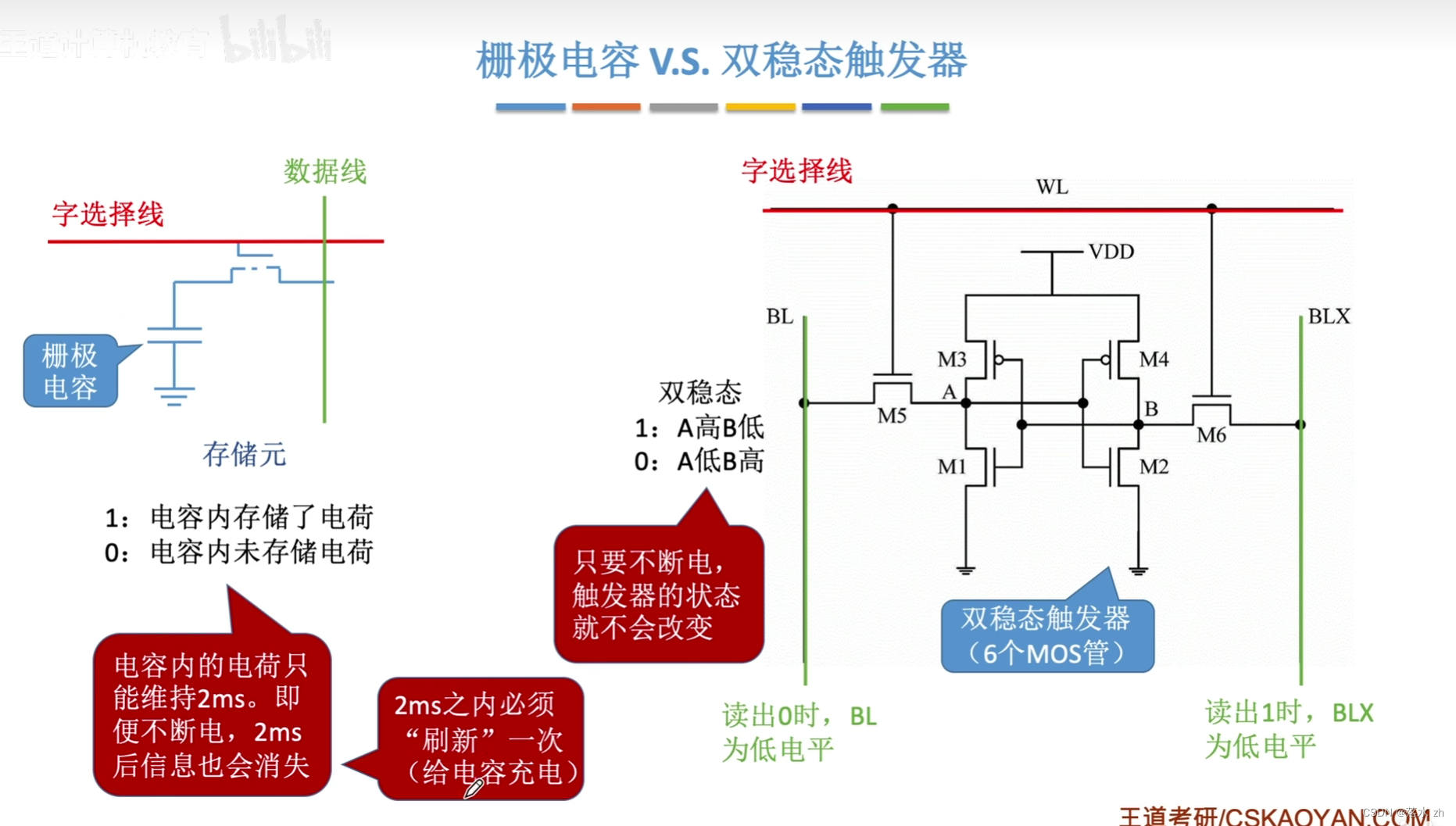

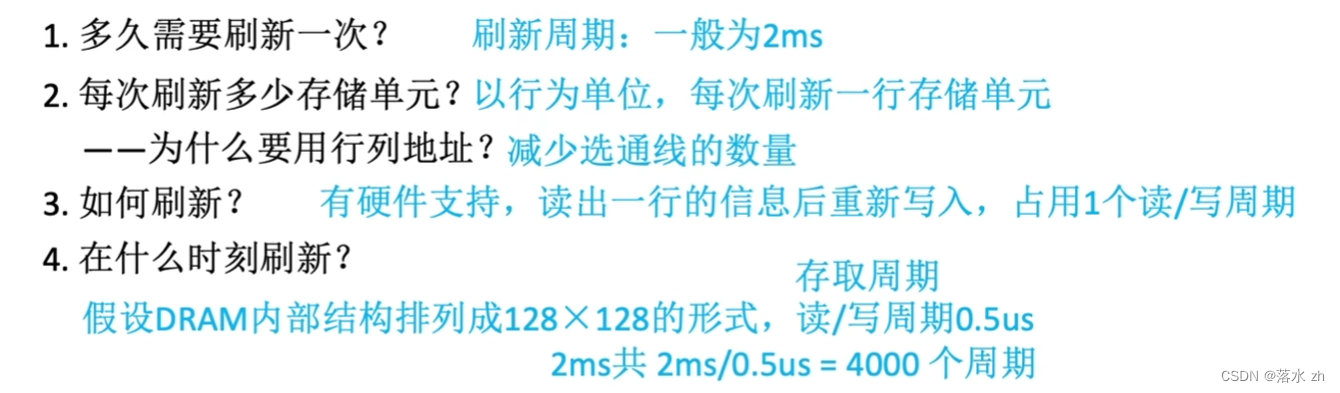

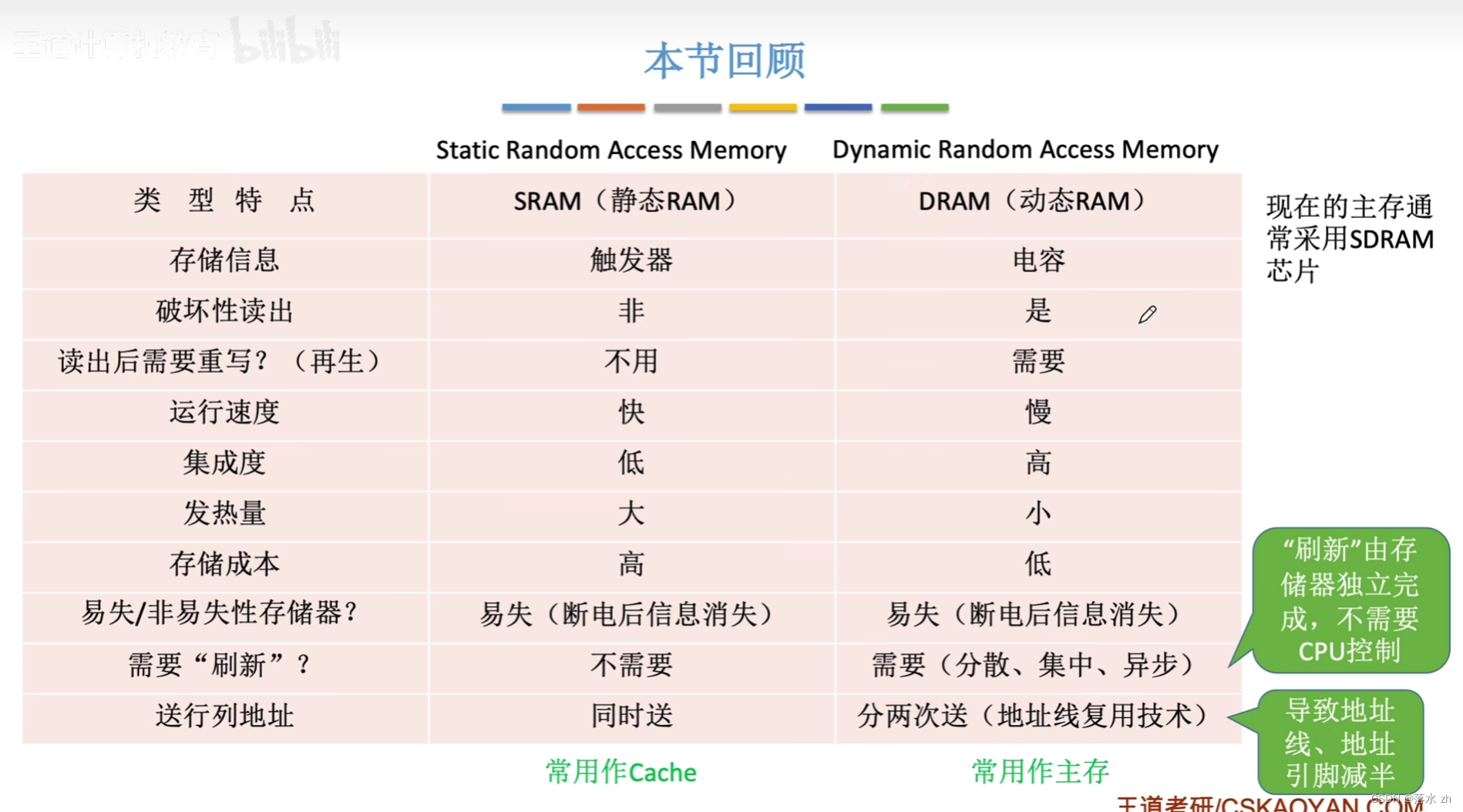

我们今天来看DRAM和SRAM: DRAM和SRAMDRAM(动态随机存取存储器)和SRAM(静态随机存取存储器)都是半导体存储器,广泛应用于计算机和其他电子设备中,但它们在设计、性能、成本和应用场景上存在显著差异: SRAM(静态随机存取存储器): 工作原理:SRAM使用双稳态触发器来存储每个比特的信息,不需要刷新电路来维持数据。这意味着一旦数据被写入SRAM,只要电源持续供应,数据就会保持不变。速度:由于其设计,SRAM提供了非常快速的读写访问时间,通常用于需要高速数据访问的场景,如CPU缓存(L1、L2、L3缓存)。集成度与成本:SRAM的每个存储单元需要更多的晶体管(通常是4到6个),这导致其集成度相对较低,成本较高,且占用更多空间。应用场景:因其高速特性,SRAM常用于缓存、寄存器以及对速度要求极高的局部存储。DRAM(动态随机存取存储器): 工作原理:DRAM通过电容来存储电荷,以此表示比特的1或0状态。由于电容会自然放电,DRAM需要定期刷新(每隔几毫秒)来保持数据的完整性。速度:相比SRAM,DRAM的读写速度较慢,因为它涉及到电容充电/放电的过程以及刷新操作。集成度与成本:DRAM的存储单元结构更为简单,每个比特通常只需一个晶体管和一个小电容,这使得DRAM能够在给定的芯片面积上集成更多的存储单元,从而降低成本,提高存储密度。应用场景:由于其高密度和相对低廉的成本,DRAM是计算机主内存(如DDR SDRAM)的首选,广泛应用于个人电脑、服务器、移动设备等,作为大容量存储解决方案。总结来说,SRAM提供快速访问但成本较高,适用于需要快速数据交换的小容量存储场景;而DRAM虽然访问速度稍慢,但因成本效益高、容量大,成为大规模存储的主流选择。 其实我们上篇博客讲的就是DRAM:

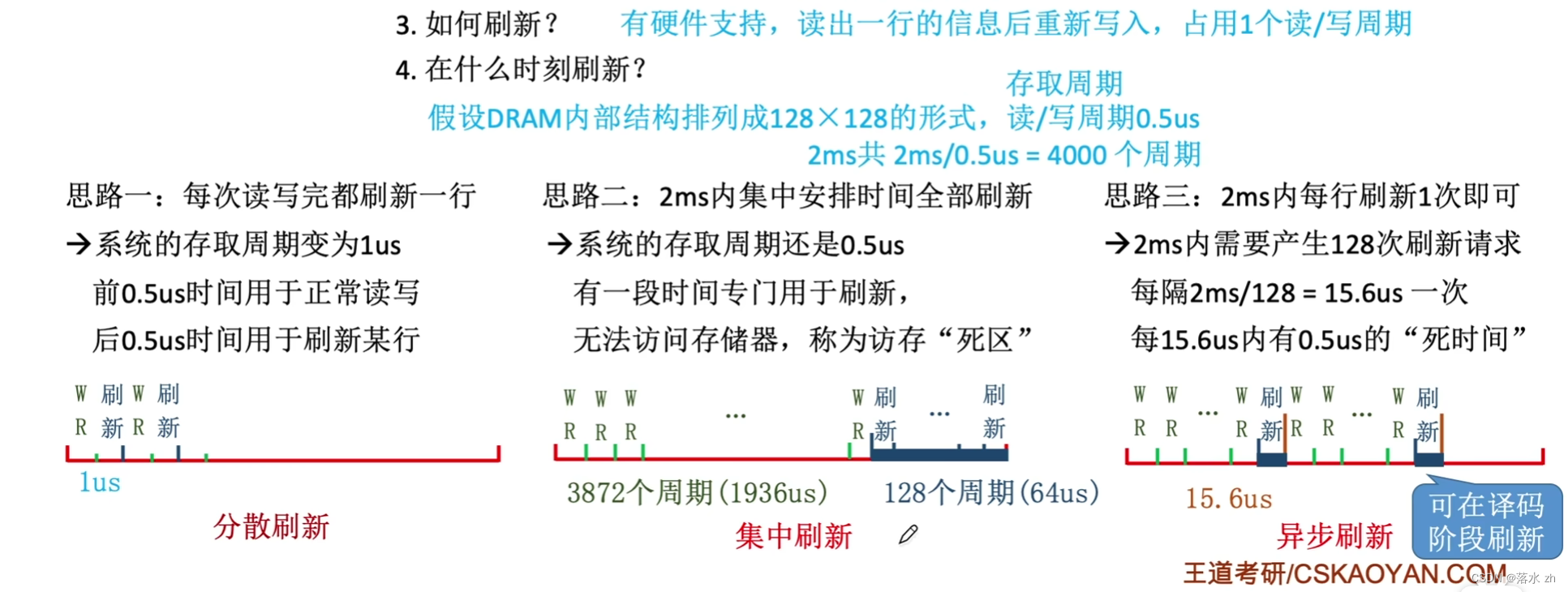

https://blog.csdn.net/qq_67693066/article/details/139881200 SRAM换了一种材料,换成了双稳态触发器: DRAM(动态随机存取存储器)的刷新是维护DRAM存储数据完整性的必要操作,因为DRAM单元中的电容会随着时间逐渐放电,导致存储的信息丢失。为了防止这种情况发生,DRAM需要定期刷新。刷新操作涉及读取每一行的数据,然后立即重写回该行,以补充电容的电荷,确保数据得以保持。 DRAM刷新主要采用以下三种方式: 集中刷新(Bulk Refresh或Collective Refresh):在这种模式下,系统会在一个特定的刷新周期内,暂停正常的读写操作,集中一段时间来逐行刷新所有存储单元。这意味着在刷新期间,DRAM无法响应其他读写请求,这会造成所谓的“刷新死区”(refresh dead time),影响系统的连续数据访问性能。 分散刷新(Distributed Refresh或Hidden Refresh):分散刷新尝试减少集中刷新带来的性能损失,它将刷新操作分散到每个存储周期中进行。在每次访问DRAM时,系统会检查是否需要对当前行进行刷新,如果需要,则在访问之后立即执行刷新操作,尽量使刷新操作与正常读写操作重叠,从而隐藏刷新带来的延迟。 异步刷新(Self Refresh):异步刷新是集中刷新和分散刷新的折衷方案,它允许DRAM在没有外部命令的情况下自行管理刷新操作。在低功耗模式或待机状态下特别有用,此时DRAM可以按照内部定时器控制的周期自行进行刷新,减少了对外部控制器的依赖,降低了系统整体的能耗。

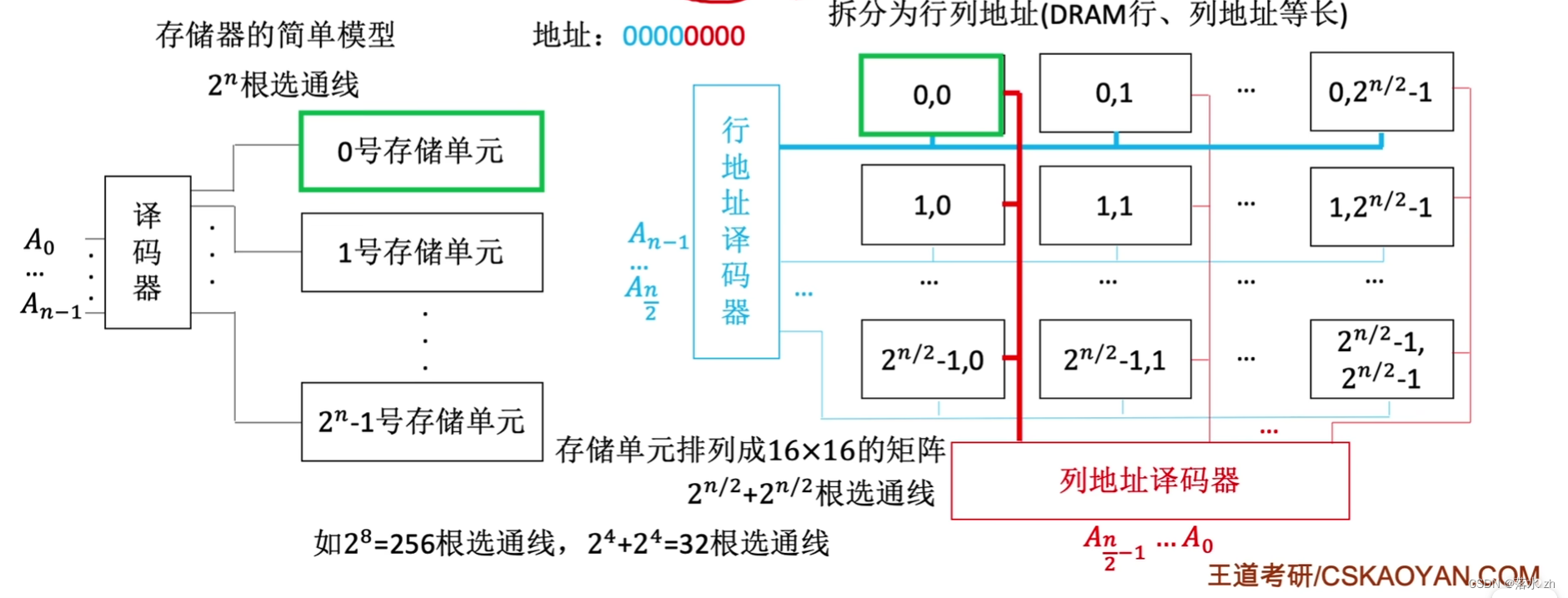

刷新间隔和刷新周期是DRAM参数的重要组成部分,刷新间隔定义了两次刷新操作之间的时间,而刷新周期则是对DRAM所有存储单元完成一次刷新的总时间间隔。这些参数由DRAM芯片规格确定,并需由系统内存控制器妥善管理,以确保数据的可靠存储。 DRAM地址复用DRAM(动态随机存取存储器)采用地址复用技术,主要是为了减少芯片引脚数量,从而降低成本并简化电路设计。具体来说,DRAM的存储阵列由行和列地址共同确定一个唯一的存储单元位置。由于DRAM存储单元数量庞大,若为每个地址位都分配单独的引脚,会显著增加芯片的物理尺寸和复杂性,进而增加制造成本。 在地址复用技术中,DRAM将完整的地址信号分为两部分:行地址和列地址,通过同一组地址线分时传送。具体过程如下: 行地址传输:首先,DRAM接收到来自内存控制器的行地址,通过行地址选通信号(RAS, Row Address Strobe)激活相应的行,这个过程被称为行有效(Row Active)或行选通(Row Access)。 列地址传输:随后,在列地址选通信号(CAS, Column Address Strobe)的作用下,DRAM准备好接收列地址。列地址被送入后,指定的列与之前激活的行交叉点处的存储单元就被选中,从而完成寻址。 数据读写:在列地址传输完成后,可以进行数据的读取或写入操作。

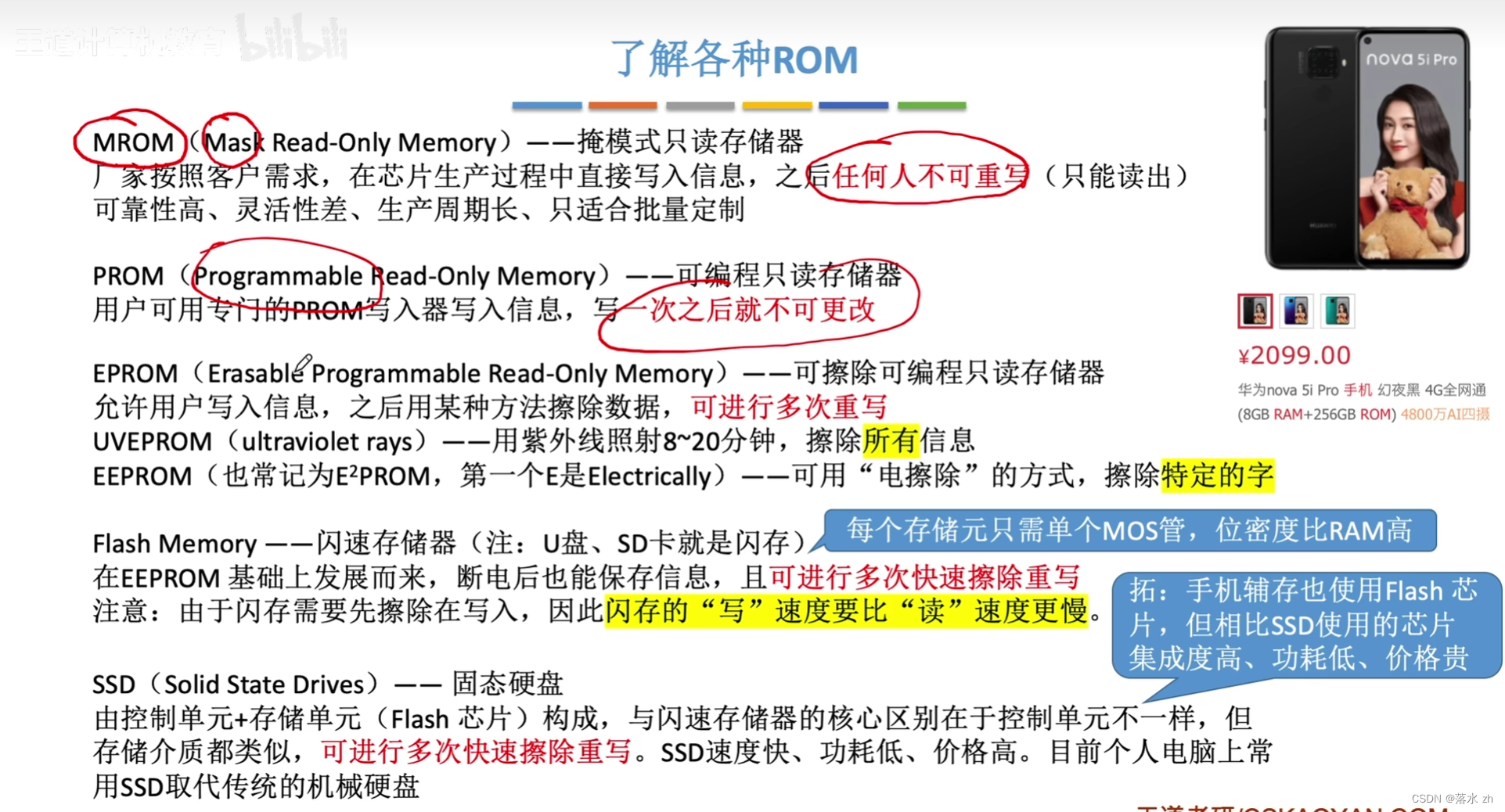

通过这样的分时复用机制,DRAM使用较少的地址线实现了对大量存储单元的寻址,降低了对硬件资源的需求。然而,这也意味着相比于地址线独立的SRAM,DRAM在每次访问时需要更多的时钟周期来完成寻址,因此在速度上有所牺牲。 我们的刷新操作一般会在行列选址的时候发生: ROM,全称为Read-Only Memory(只读存储器),是一种非易失性存储介质,其中存储的数据在正常操作下是固定的,无法轻松或直接修改。ROM的特点包括: 数据持久性:ROM中的信息在断电后仍能保留,因为它是非易失性的。 出厂预编程:传统ROM的信息通常在制造过程中就被永久写入,不适合用户修改。 固定用途:由于数据不可改写,ROM常用于存储计算机启动时所需的固件、BIOS、初始化程序或者特定设备的控制代码等。随着技术的发展,ROM的概念扩展到了几种不同的类型,包括: PROM (可编程只读存储器):用户可以通过特殊的设备一次性写入数据,之后便无法更改。 EPROM (可擦除可编程只读存储器):可以通过紫外线照射擦除原有数据,然后可以重新编程。这类ROM有一个透明窗口,以便暴露芯片于紫外线。 EEPROM (电可擦除可编程只读存储器):可以在电路板上通过电信号擦除和重写数据,无需移除芯片或使用特殊设备,提供了更高的灵活性。 Flash Memory(闪存):虽然通常不归类为传统的ROM,但闪存基于EEPROM技术,提供高速度、高密度和更便捷的多次擦写能力,广泛应用于USB驱动器、存储卡和固态硬盘中。

|

【本文地址】

今日新闻 |

推荐新闻 |

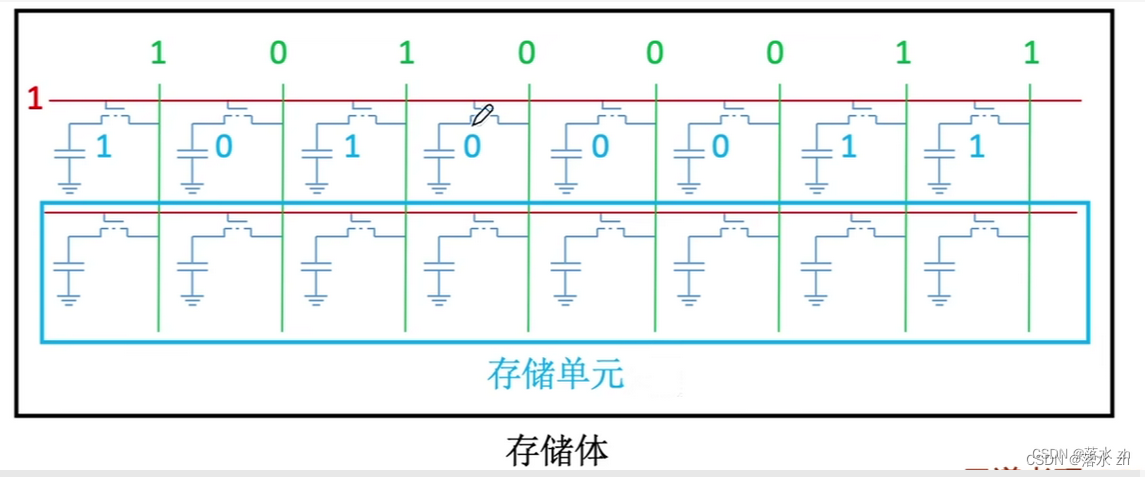

这就是DRAM的内部组成,如果大家对上一篇博客有兴趣的话,可以点击这里:

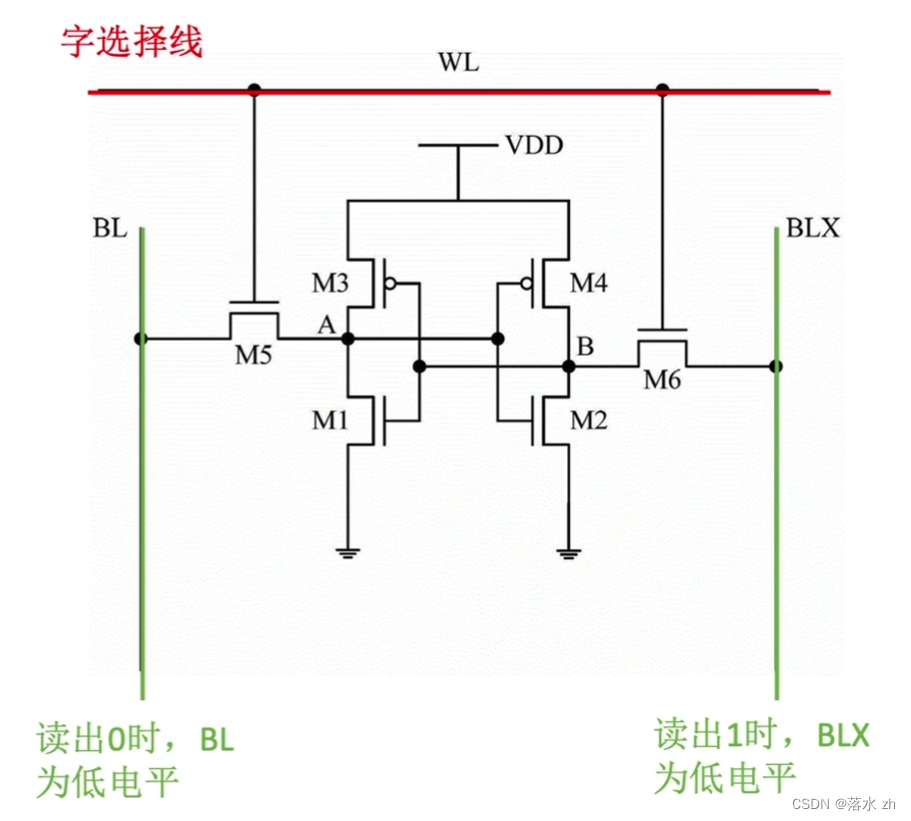

这就是DRAM的内部组成,如果大家对上一篇博客有兴趣的话,可以点击这里: 双稳态触发器集成了6根MOS管,体积更大,稳定性更高。经常用作Cache的材料。

双稳态触发器集成了6根MOS管,体积更大,稳定性更高。经常用作Cache的材料。

我们的SRAM就不用刷新:

我们的SRAM就不用刷新:

下面一张图对比了SRAM和DRAM

下面一张图对比了SRAM和DRAM

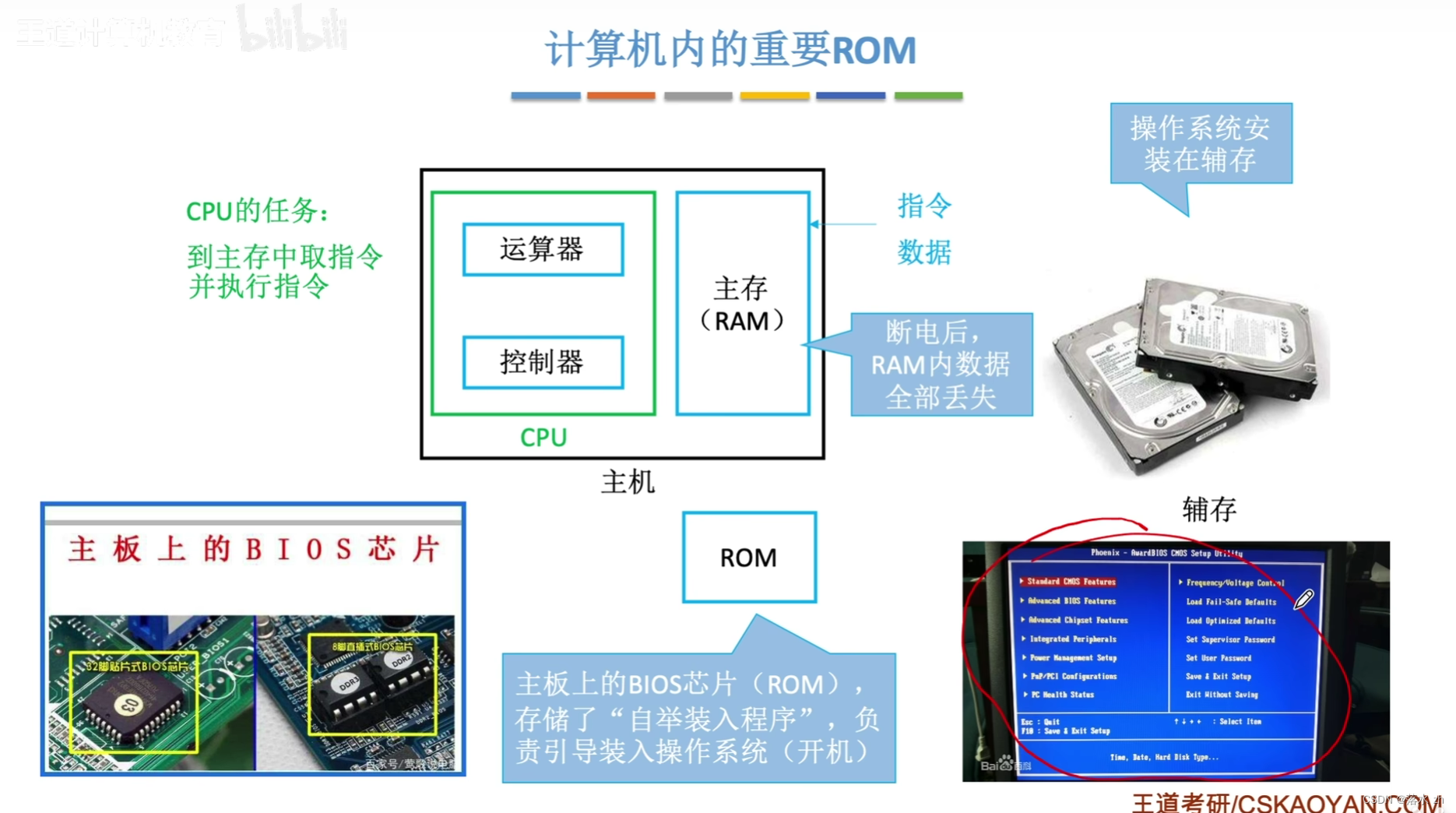

我们的操作系统就是安装在ROM中的:

我们的操作系统就是安装在ROM中的: