DDR4看这一篇就够了 |

您所在的位置:网站首页 › ddr42000 › DDR4看这一篇就够了 |

DDR4看这一篇就够了

|

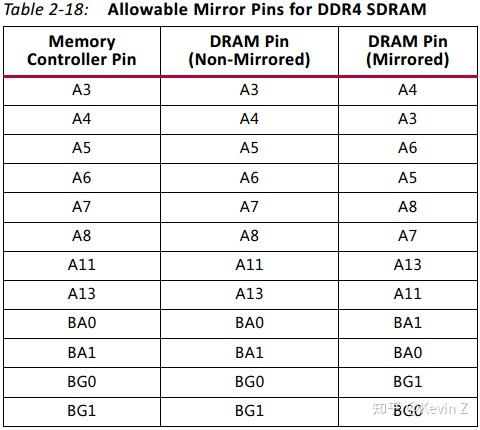

DDR4看这一篇就够了简介信号分析1. 电源2. 时钟3. 数据线和DQS4. 地址和控制等长管理布局方式参考链接简介 DDR4 SDRAM(Double-Data-Rate Fourth Generation Synchronous Dynamic Random Access Memory,简称为DDR4 SDRAM),是一种高带宽的计算机存储器规格。它属于SDRAM家族的存储器产品,提供了相较于DDR3 SDRAM更高的运行性能与更低的电压,是现时最新的存储器规格。起始数据传送率由2133MT/s起跳,上限暂定为4266MT/s。 信号分析DDR的信号主要分为以下几类: 1. 电源DDR的电源又可分为三类: 主电源VDD和VDDQ。主电源的要求是VDDQ=VDD=1.2V。VDDQ是给IO buffer供电的电源,VDD则是DDR的core power supply。一般使用中都是吧VDDQ和VDD合成一个电源使用,在SODIMM上则只有VDD引脚,内存条上可能有一些电路,也可能没有。参考电源Vref。参考电源Vref要求跟随VDDQ,并且Vref=VDDQ/2,这个电压既可以使用电源芯片,也可以使用电阻分压的方式得到。Vref电流较小,在几个mA~几十mA之间。一般采用电阻分压的方式,分压电阻在100~10K之间均可,需要1%精度的电阻。Vref的每个管教上需要加10nF的电容滤波,并且每个分压电阻上也并联一个电容较好。匹配电压VTT(Tracking Termination Voltage)VTT为匹配电阻上拉到的电源,VTT=VDDQ/2。DDR的设计中,有些用不到VTT;但如果使用VTT,VTT的电流要求是比较大的,因此需要专门的电源芯片来满足要求,并且会放一些uF级别储能电容。激活电压VPP(DRAM Activating Power Supply)VPP一般为2.5V。VPP激活电压,必须要同时或者早于VDD,电压值也要全时间段都高于VDD。2. 时钟DDR时钟CK_N/P为差分走线,一般使用终端并联100欧姆的匹配方式,差分走线差分对控制阻抗为差分100欧姆,单端50欧姆。DDR4的工作时钟依赖于DDR controller的input,一般也即CPU或者交换芯片。 3. 数据线和DQSDQS(data strobe)信号相当于数据信号的参考时钟,它在走线时需要保持和CLK信号保持等长,每8bit数据信号对应一组DQS信号。DQS信号在走线时需要与同组的DQS信号保持等长,控制单端50欧姆的阻抗。 根据Xilinx的UG583,DQS需要做到和DQ的严格等长,但与clock信号有较大的弹性,直接看图:   这种要求在原理上其实也是统一的,也即传输的信号要与时钟时间上同步,通过PCB上等长来尽量保证同步,因此DQS作为DQ的类似于clock的信号,需要做到严格等长,但clock与DQS之间并没有强绑定关系,所以相对长度就可以宽松一些。但因为clock与DQ信号有直接关系,所以它们之间又有相对严格的要求。 数据 数据信号IO方向功能描述 4. 地址和控制 4. 地址和控制地址和控制信号没有DQ的速度快,以时钟的上升沿采样,所以需要与时钟走线保持等长。使用多片DDR的情况下,地址和控制信号为一驱多的关系,需要注意匹配方式。地址 地址信号IO方向功能描述 控制 控制信号IO方向功能描述 等长管理以下等长要求来自ddr手册,实际应用中需要参考主芯片guideline和skew control,可能会有或松或严的改变 等长管理以下等长要求来自ddr手册,实际应用中需要参考主芯片guideline和skew control,可能会有或松或严的改变差分时钟之间等长不大于5mil,地址和控制信号都以时钟为基准,等长误差范围为±150mil。数据组以DQ0为准,等长控制在25mil以内。各数据组之间,以时钟线为基准,等长差范围设置为0~500mil。布局方式 在PCB上,DDR4 Layout分为所有内存颗粒在单面的 Fly-By 拓扑和双面的 Clamshell 拓扑。Fly-By 拓扑更易于信号走线,信号完整性更好,但占用单板空间较大;Clamshell 拓扑更节约空间,但对走线要求更高,适用于对空间要求严格的应用场合。  对于 Clamshell 拓扑的走线,由于内存颗粒PIN分布对称的特性,地址线在换层时造成地孔不足、桩线过长等信号完整性问题,为此 JEDEC 规范定义 Address Mirroring 功能,允许调换DRAM特定地址管脚的功能。下表列出的是DDR4 SDRAM中可以调换的地址引脚。  参考链接DDR4原理及硬件设计DDR硬件设计要点详解DDR4设计概述以及分析仿真案例 扒一扒DDR4的新功能和PCB设计上的一些注意事项JESD79-4A-(DDR4)DDR布线要求及拓扑结构分析DDR4 PCB Design 参考链接DDR4原理及硬件设计DDR硬件设计要点详解DDR4设计概述以及分析仿真案例 扒一扒DDR4的新功能和PCB设计上的一些注意事项JESD79-4A-(DDR4)DDR布线要求及拓扑结构分析DDR4 PCB Design

|

【本文地址】

今日新闻 |

推荐新闻 |