ZYNQ AXI4(AXI |

您所在的位置:网站首页 › axi4总线实现ddr读写 › ZYNQ AXI4(AXI |

ZYNQ AXI4(AXI

|

1.简述

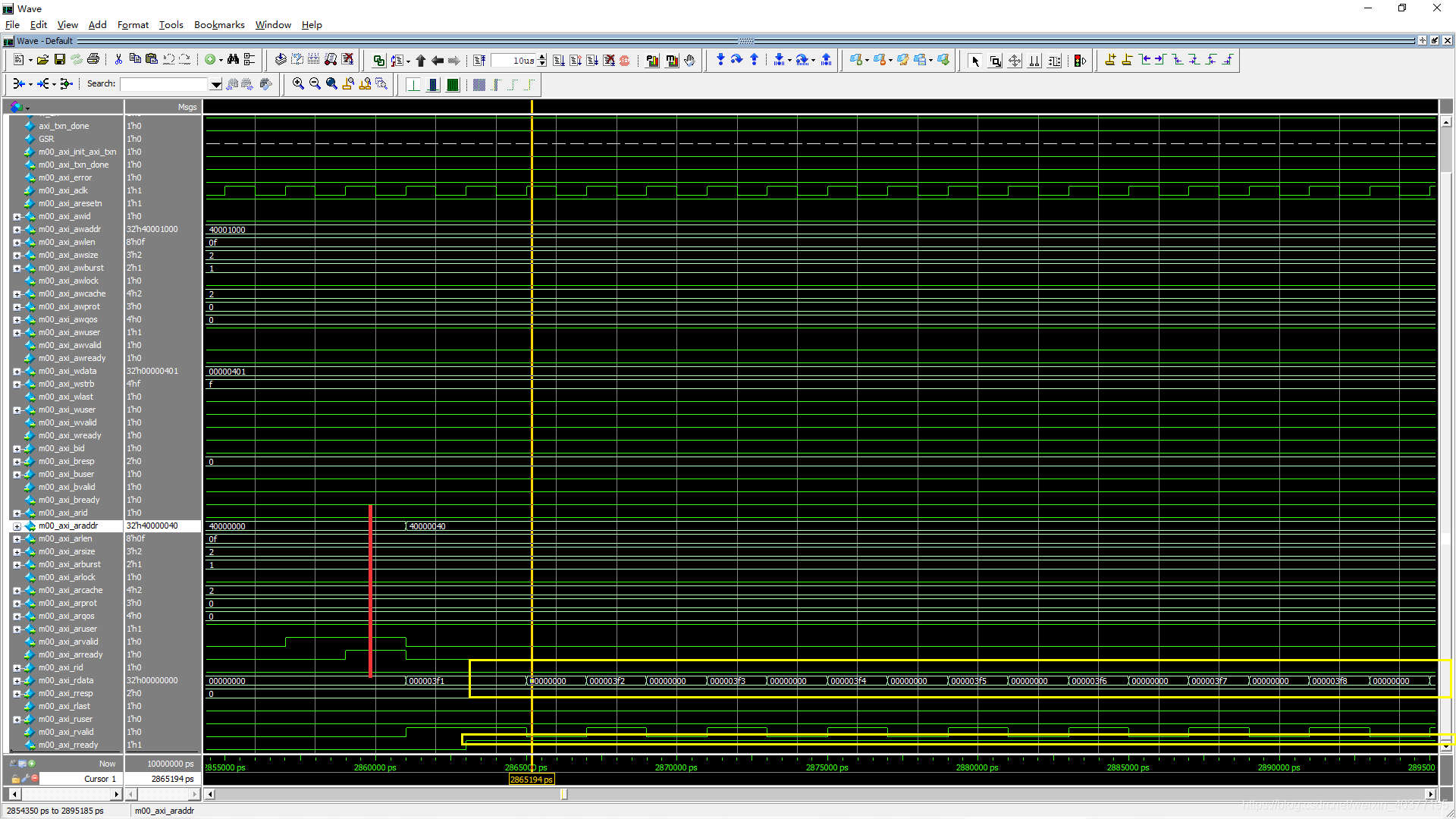

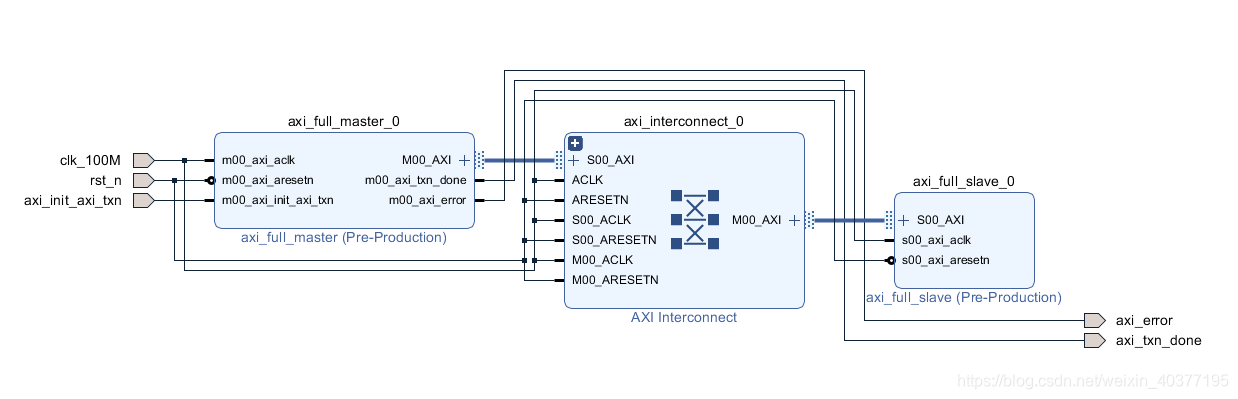

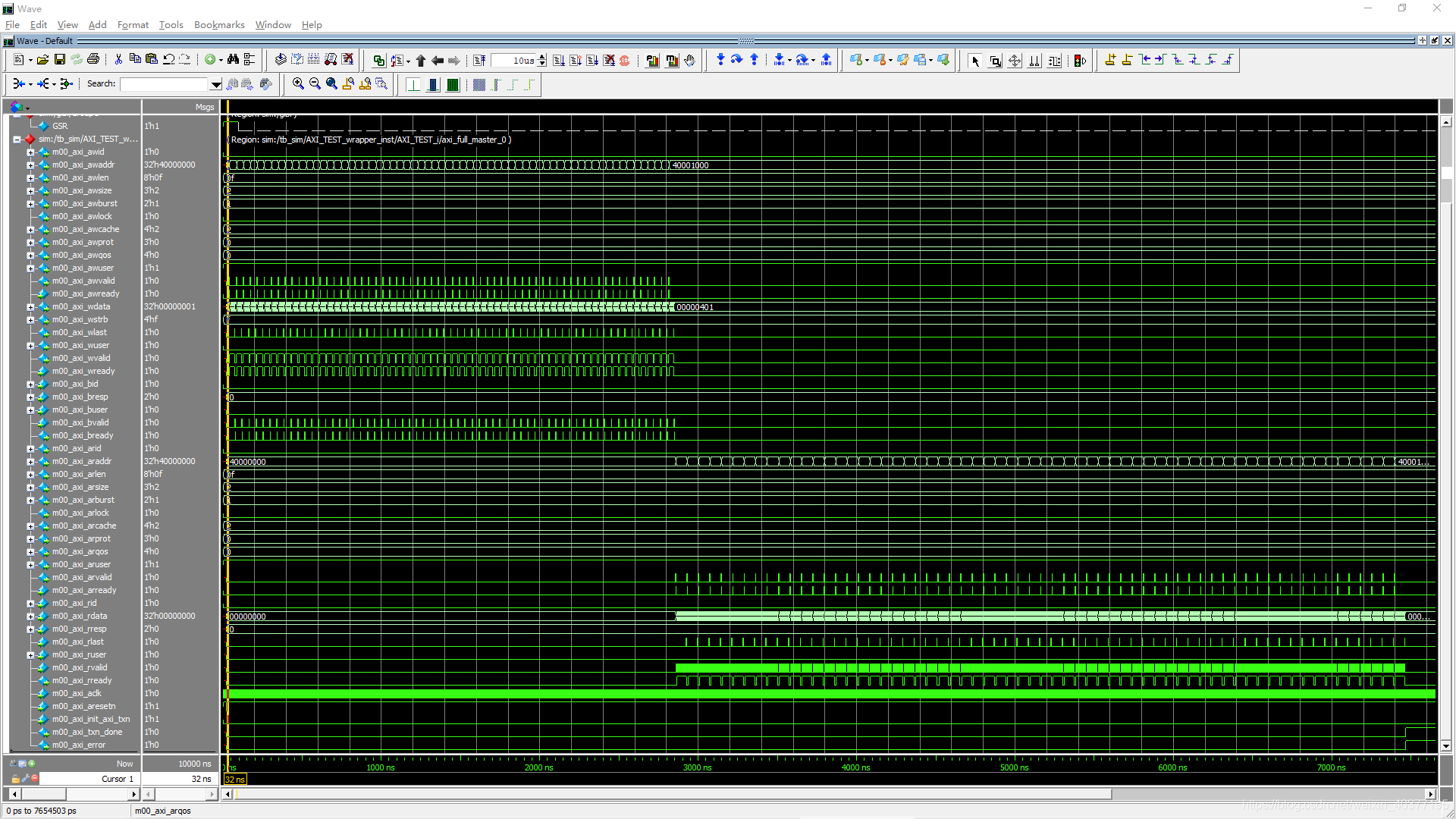

使用vivado自定义封装axi-full master IP,同时也封装一个slave IP方便仿真观察信号。 2.封装IP1)打开vivado,进行如下操作 过程我就不说了,大家应该都会。 记得生成wrapper,然后将wrapper的端口例化到激励里面。 `timescale 1ns / 1ps // // Company: // Engineer: // // Create Date: 2020/03/01 18:28:32 // Design Name: // Module Name: tb_sim // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // // module tb_sim(); reg axi_ACLK; // AXI 总线时钟 reg axi_ARESETn; // 系统复位信号,低电平有效 reg r_in_key; // 模拟按键,正脉冲 wire w_err; // 状态指示,异常 wire axi_txn_done; AXI_TEST_wrapper AXI_TEST_wrapper_inst( .axi_error (w_err ), .axi_init_axi_txn (r_in_key ), .axi_txn_done (axi_txn_done ), .clk_100M (axi_ACLK ), .rst_n (axi_ARESETn ) ); parameter PERIOD = 2; always begin #(PERIOD/2); axi_ACLK = ~axi_ACLK; end initial begin axi_ACLK = 1'b0; axi_ARESETn = 1'b1; r_in_key = 1'b0; #(10*PERIOD); axi_ARESETn = 1'b0; #(2*PERIOD); axi_ARESETn = 1'b1; #(4*PERIOD); r_in_key = 1'b1; #(2*PERIOD); r_in_key = 1'b0; end endmodule 5.启动仿真我是使用modelsim与vivado联合仿真。我们直接看仿真波形。 1)可以直接看出,master端一开始直接先写数据,然后再读数据。 axi-full到这儿,算是很清晰了,下一步就要进行改造。 欢迎关注我的公众号:芯王国,有更多的FPGA&数字IC的技术分享,还可以获取开源FPGA项目!

|

【本文地址】

今日新闻 |

推荐新闻 |

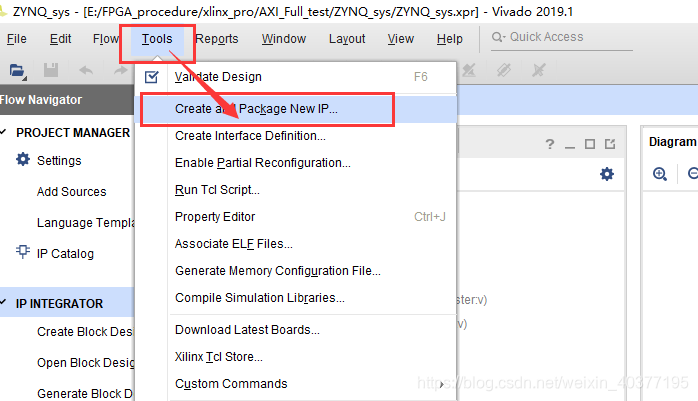

2)选择axi选项

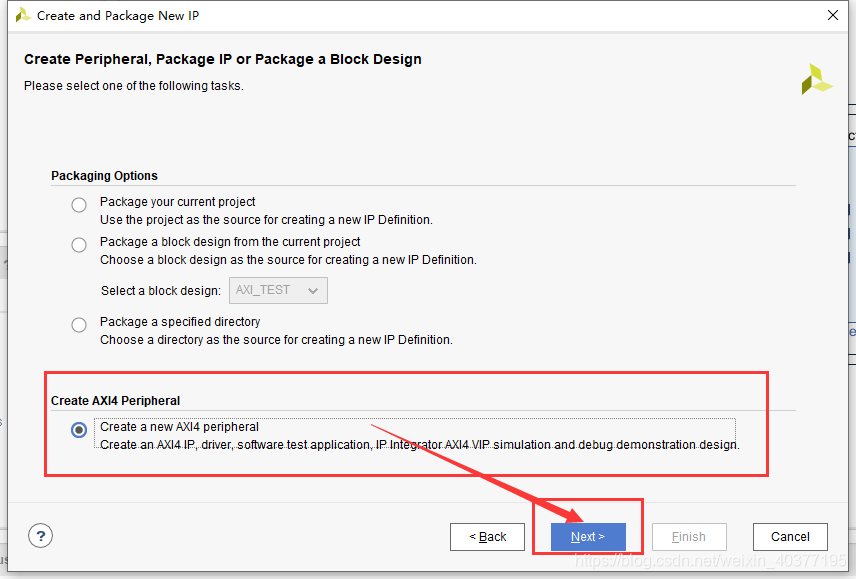

2)选择axi选项  3)改下名字

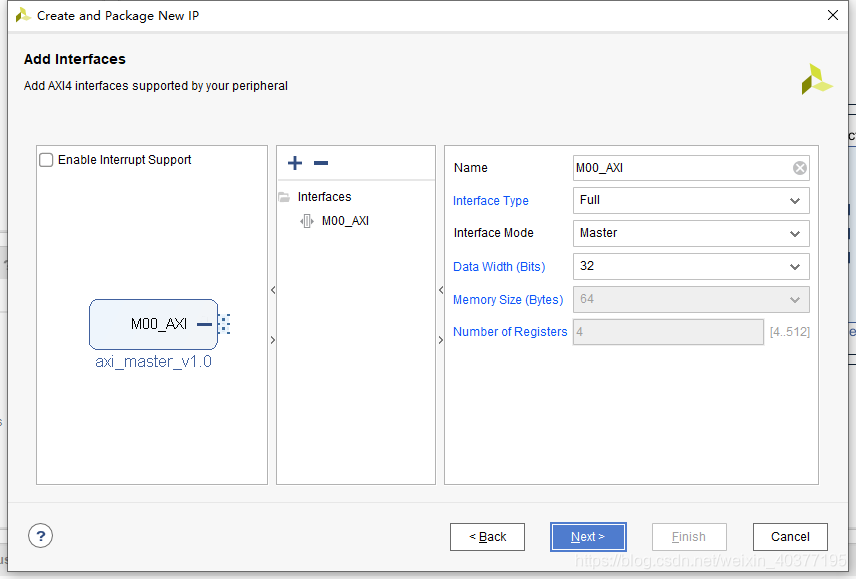

3)改下名字  4)选择full类型,选择Master,点击next

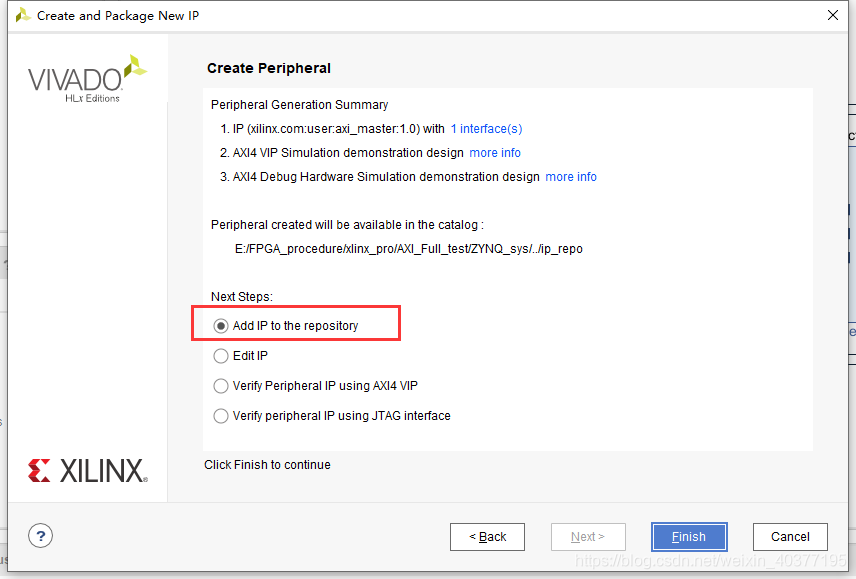

4)选择full类型,选择Master,点击next  5)最后默认选择将IP添加到IP库,现在不用编辑。

5)最后默认选择将IP添加到IP库,现在不用编辑。 6)slave的和上面一样流程,记得改名,最后设置如图默认。

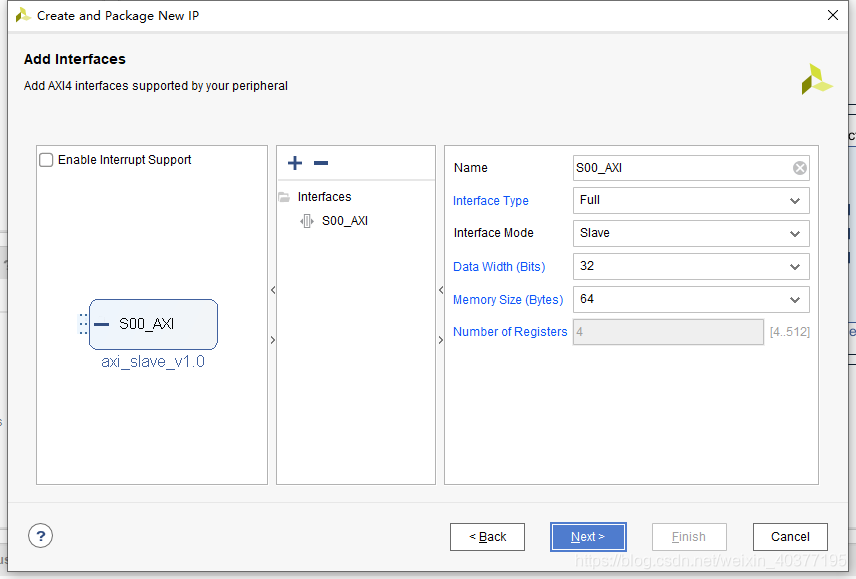

6)slave的和上面一样流程,记得改名,最后设置如图默认。

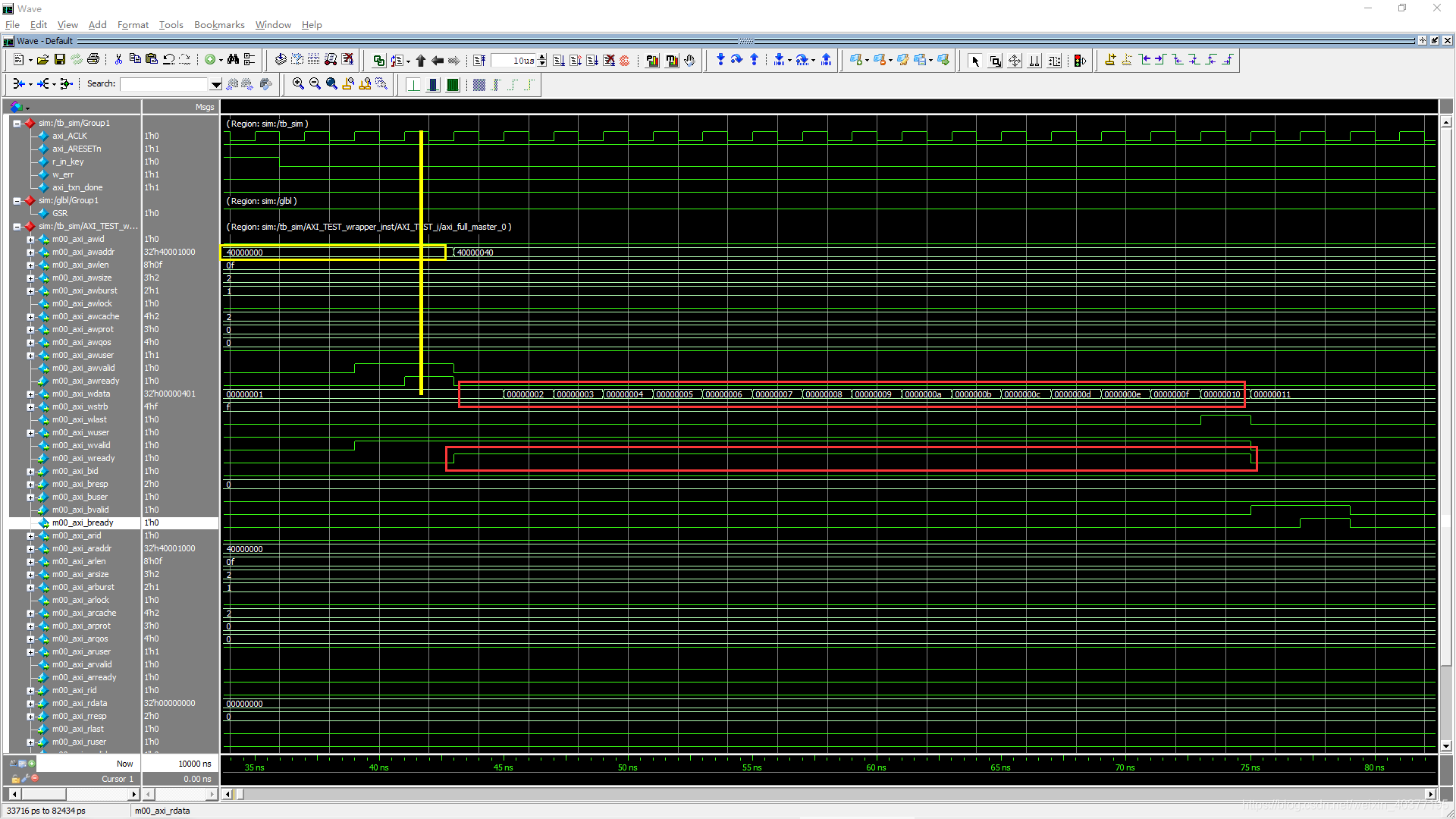

2)如图,IP默认是16突发,所以先写入地址,再写入16个数据。

2)如图,IP默认是16突发,所以先写入地址,再写入16个数据。  3)看看读,也和写一样,先写入地址,然后读入16个突发的数据,但是这个数据不是连续的,间隔了一个时钟周期。

3)看看读,也和写一样,先写入地址,然后读入16个突发的数据,但是这个数据不是连续的,间隔了一个时钟周期。