电子技术 |

您所在的位置:网站首页 › NMOS反相器 › 电子技术 |

电子技术

|

电子技术——CMOS反相器的动态响应

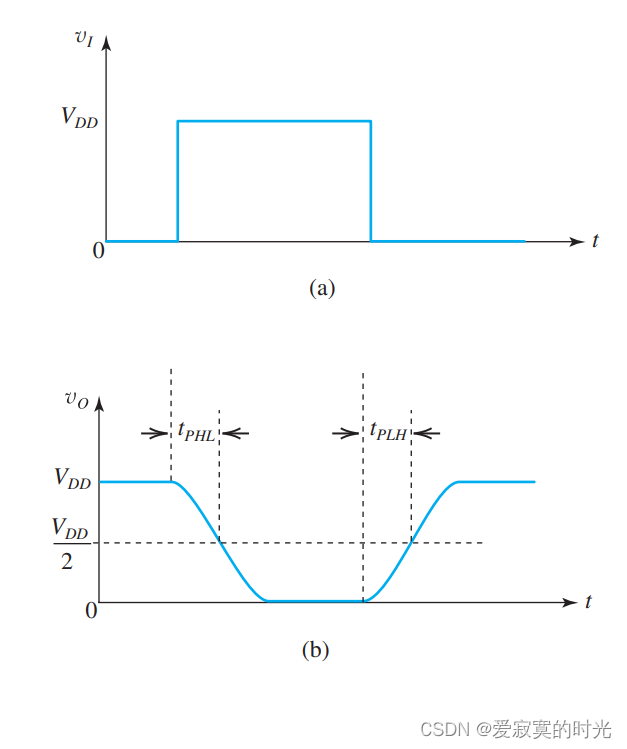

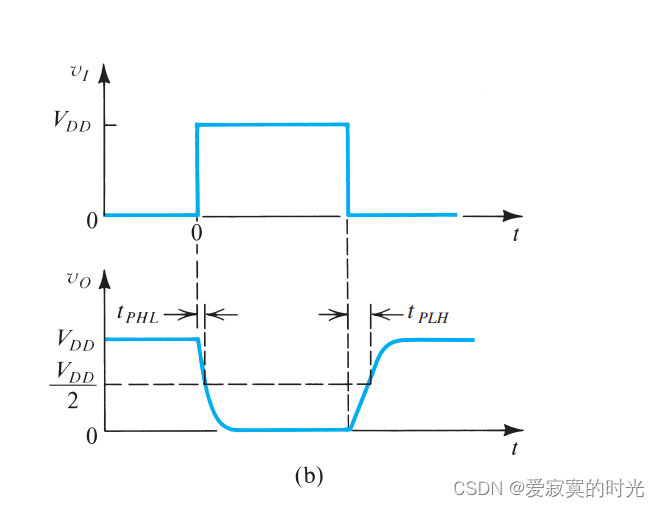

数字系统的速度(例如计算机)取决于其构成逻辑门的信号传播速度。因为反相器是数字逻辑门电路的基础,反相器的传播速度是一个很重要的特性。 传播延迟传播延迟定义为反相器响应他的输入所需要的时间。特别的,先让我们对反相器输入一个理想的阶跃函数,获得对应的响应,如图:

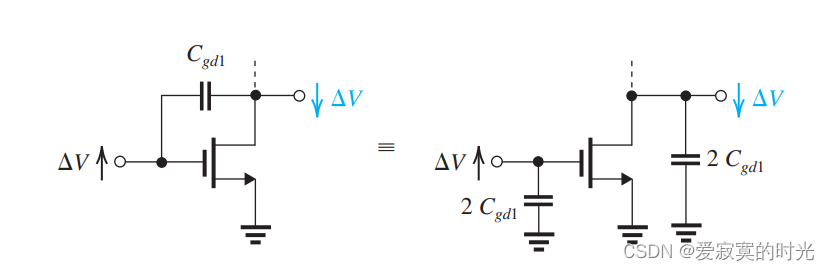

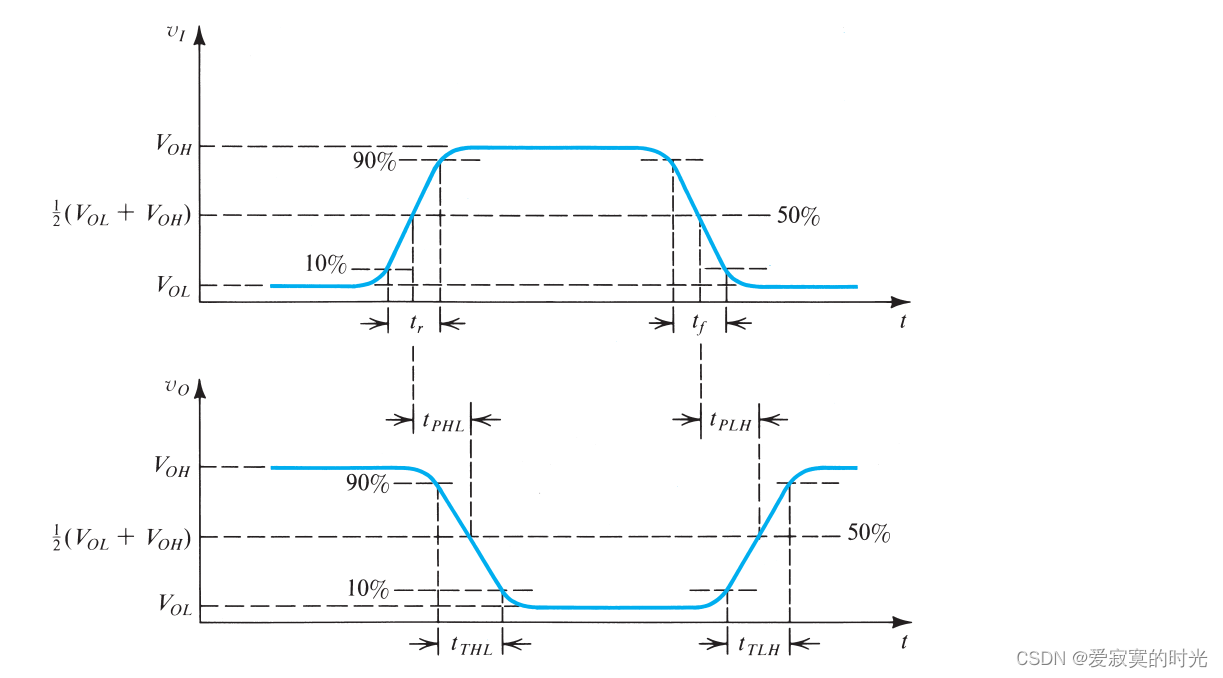

传播延迟定义为: t P ≡ 1 2 ( t P L H + t P H L ) t_P \equiv \frac{1}{2}(t_{PLH} + t_{PHL}) tP≡21(tPLH+tPHL) 定义完传播延迟之后,我们定义反相器的最大开关速度,从图(b)中我们发现,最小的周期为: T m i n = t P H L + t P L H = 2 t P T_{min} = t_{PHL} + t_{PLH} = 2t_P Tmin=tPHL+tPLH=2tP 则最大开关频率为: f m a x = 1 T m i n = 1 2 t P f_{max} = \frac{1}{T_{min}} = \frac{1}{2t_P} fmax=Tmin1=2tP1 到此为止,读者一定想知道造成CMOS反相器传播延迟的原因。这仅仅是因为需要给电路中的电容充放电所需要的时间,电容存在于MOSFET内部的电容、线间电容以及逻辑门之间的输入容抗。稍后我们会解释电容如何决定 t P t_P tP ,现在我们预备两个关键的知识: 一个分析动态响应的关键表达式为 I Δ t = Δ Q = C Δ V I\Delta t = \Delta Q = C \Delta V IΔt=ΔQ=CΔV 。这说明,对一个电容器充 Δ Q \Delta Q ΔQ 的电荷量需要时间 Δ t \Delta t Δt ,此时电容器两端电压上升 Δ V \Delta V ΔV 。对于一个时间常数为 τ \tau τ 的低通型或高通型STC电路来说,若输入是一个阶跃函数,则输出的瞬态响应为 y ( t ) = Y ∞ − ( Y ∞ − Y 0 + ) e − t / τ y(t) = Y_\infty - (Y_\infty - Y_{0+}) e^{-t/\tau} y(t)=Y∞−(Y∞−Y0+)e−t/τ ,这里 Y ∞ Y_\infty Y∞ 是一个有限值,这个值代表了响应的终值, Y 0 + Y_{0+} Y0+ 表示响应的起始值当 t = 0 t = 0 t=0 的时候。现在,我们可以正式的定义CMOS反相器的传播延迟,若输入的激励是一个具有 上升下降时间 的阶跃函数,那么我们称 1 2 ( V O L + V O H ) \frac{1}{2} (V_{OL} + V_{OH}) 21(VOL+VOH) 为输入的翻转点,反相器的在输入翻转点处开始动态响应,从这里开始计时,直到输出也达到翻转点停止,这一段时间称为响应的上升或下降时间,分别记为 t P L H t_{PLH} tPLH 和 t P H L t_{PHL} tPHL ,这里 P P P 是延迟的意思,而 L H LH LH 是从低到高, H L HL HL 是从高到低。通常定义传播延迟为 t P L H t_{PLH} tPLH 和 t P H L t_{PHL} tPHL 的平均值。并且,我们称过渡时间为从一个响应的10%到90%的时间,如图:

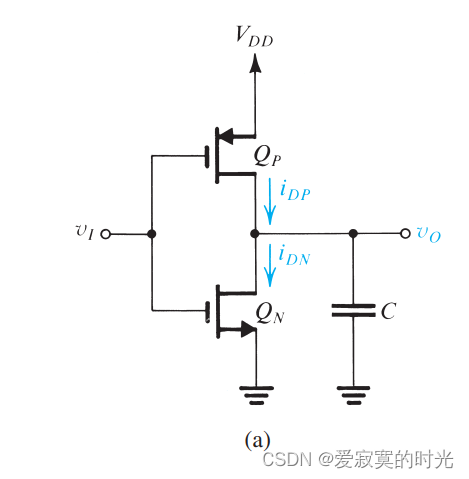

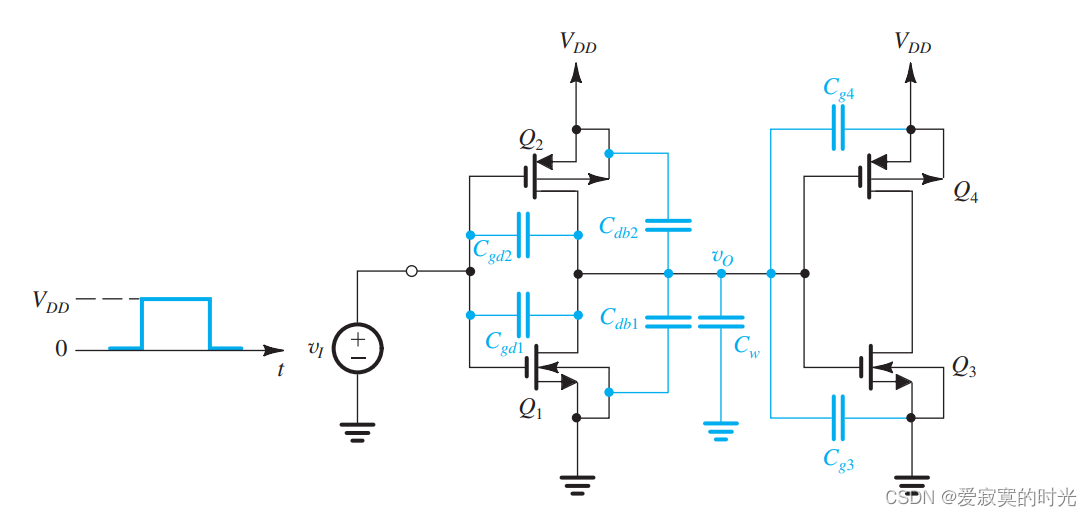

我们通过一下两个步骤决定CMOS反相器的传播延迟: 将电路中所有的电容替换为从CMOS反相器的输出端到地的等效电容 C C C 。计算 t P L H t_{PLH} tPLH 和 t P L H t_{PLH} tPLH 以及 t P t_P tP 。我们反过来学习者两个步骤,首先我们先学习如何计算传播延迟,之后我们学习如何等效电容。 下图展示了仅有输出端到地的电容 C C C :

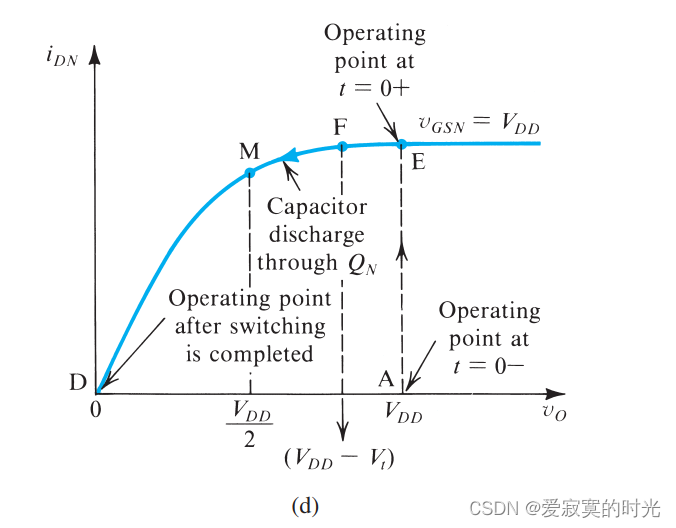

一个简单的方法是我们可以计算EM段的平均电流 I a v I_{av} Iav ,之后,通过方程: I a v t P H L = C [ V D D − ( V D D / 2 ) ] I_{av} t_{PHL} = C[V_{DD} - (V_{DD} / 2)] IavtPHL=C[VDD−(VDD/2)] 决定: t P H L = C V D D 2 I a v t_{PHL} = \frac{CV_{DD}}{2I_{av}} tPHL=2IavCVDD 平均电流 I a v I_{av} Iav 可以通过下面的表达式估算: I a v = 1 2 [ i D N ( E ) + i D N ( M ) ] I_{av} = \frac{1}{2} [i_{DN}(E) + i_{DN}(M)] Iav=21[iDN(E)+iDN(M)] 这里: i D N ( E ) = 1 2 k n ′ ( W / L ) n ( V D D − V t n ) 2 i_{DN}(E) = \frac{1}{2}k_n'(W/L)_n(V_{DD} - V_{tn})^2 iDN(E)=21kn′(W/L)n(VDD−Vtn)2 并且: i D N ( M ) = k n ′ ( W / L ) n [ ( V D D − V t n ) ( V D D 2 ) − 1 2 ( V D D 2 ) 2 ] i_{DN}(M) = k_n' (W/L)_n [(V_{DD} - V_{tn})(\frac{V_{DD}}{2}) - \frac{1}{2}(\frac{V_{DD}}{2})^2] iDN(M)=kn′(W/L)n[(VDD−Vtn)(2VDD)−21(2VDD)2] 我们假设 λ n = 0 \lambda_n = 0 λn=0 带入上式得到: t P H L = α n C k n ′ ( W / L ) n V D D t_{PHL} = \frac{\alpha_nC}{k_n' (W/L)_n V_{DD}} tPHL=kn′(W/L)nVDDαnC 这里的 α n \alpha_n αn 是: α n = 2 / [ 7 4 − 3 V t n V D D + ( V t n V D D ) 2 ] \alpha_n = 2 / [\frac{7}{4} - \frac{3V_{tn}}{V_{DD}} + (\frac{V_{tn}}{V_{DD}})^2] αn=2/[47−VDD3Vtn+(VDDVtn)2] α n \alpha_n αn 通常在1-2的范围内。 同样的分析方法可以计算 t P L H t_{PLH} tPLH 得到: t P L H = α p C k p ′ ( W / L ) p V D D t_{PLH} = \frac{\alpha_pC}{k_p' (W/L)_p V_{DD}} tPLH=kp′(W/L)pVDDαpC 这里: α p = 2 / [ 7 4 − 3 ∣ V t p ∣ V D D + ∣ V t p V D D ∣ 2 ] \alpha_p = 2 / [\frac{7}{4} - \frac{3|V_{tp}|}{V_{DD}} + |\frac{V_{tp}}{V_{DD}}|^2] αp=2/[47−VDD3∣Vtp∣+∣VDDVtp∣2] 最后,传播延迟为: t p = 1 2 ( t P H L + t P L H ) t_p = \frac{1}{2}(t_{PHL} + t_{PLH}) tp=21(tPHL+tPLH) 通过上面的表达式我们可以总结一下几点: t P t_P tP 的两个分量可以通过条件 W / L W/L W/L 来使得相同。因为 t P t_P tP 正比于 C C C 。设计师应该努力减小 C C C 的值,这可以通过减小沟道长度,或是减小信号线长或是其他寄生电容。通过合理的电路布局可以减小潜在的寄生电容。使用合适的工艺,使得增加 k ′ k' k′ 的值,以减少传播延迟。但是, C o x C_{ox} Cox 也会增加。使用更大的宽长比。同样的,增加元件的体积同样会增加电容值。更大的 V D D V_{DD} VDD 可以减小 t P t_P tP 。然而,通常情况下, V D D V_{DD} VDD 受到工艺的限制,而不是设计师随便决定。 另一种替代方法下面的表达式来自于深亚微米工艺,主要由速度饱和效应引起,之后我们会介绍,饱和效应降低了MOS管在饱和区的电流,提升了传播延迟时间。为了估计此情况的传播延迟,我们可以使用下面的方法。 下图展示了一个替代估算的方法原理图:

t P H L = 0.69 R N C t_{PHL} = 0.69R_NC tPHL=0.69RNC 以及: t P L H = 0.69 R P C t_{PLH} = 0.69R_PC tPLH=0.69RPC 一个经验的估算公式为: R N = 12.5 ( W / L ) n k Ω R_N = \frac{12.5}{(W/L)_n}k\Omega RN=(W/L)n12.5kΩ R P = 30 ( W / L ) p k Ω R_P = \frac{30}{(W/L)_p}k\Omega RP=(W/L)p30kΩ 这个公式适用于CMOS 0.25um 和 0.18um 以及 0.13um 的工艺。 对于更实际的情况,输入具有上升和下降时间,此时 0.69 0.69 0.69 十分接近于单位一,此时: t P H L ≃ R N C t_{PHL} \simeq R_NC tPHL≃RNC t P L H ≃ R P C t_{PLH} \simeq R_PC tPLH≃RPC 最后,需要注意的是,以上分析都是基于估算,并不总是会产生精确的结果,必要请需要使用电路仿真。 决定等效容性负载C下图是我们研究的原理图:

同理对于

C

g

d

2

C_{gd2}

Cgd2 。通常来说体极的电压是固定的,因此体极-漏极直接的电容,可以直接等效为对地的电容。此时我们假设第二个CMOS反相器的状态还没有切换,所以输入容抗等于:

C

g

3

+

C

g

4

=

(

W

L

)

3

C

o

x

+

(

W

L

)

4

C

o

x

+

C

g

s

o

v

3

+

C

g

d

o

v

3

+

C

g

s

o

v

4

+

C

g

d

o

v

4

C_{g3} + C_{g4} = (WL)_3 C_{ox} + (WL)_4 C_{ox} + C_{gsov3} + C_{gdov3} + C_{gsov4} + C_{gdov4}

Cg3+Cg4=(WL)3Cox+(WL)4Cox+Cgsov3+Cgdov3+Cgsov4+Cgdov4 。 同理对于

C

g

d

2

C_{gd2}

Cgd2 。通常来说体极的电压是固定的,因此体极-漏极直接的电容,可以直接等效为对地的电容。此时我们假设第二个CMOS反相器的状态还没有切换,所以输入容抗等于:

C

g

3

+

C

g

4

=

(

W

L

)

3

C

o

x

+

(

W

L

)

4

C

o

x

+

C

g

s

o

v

3

+

C

g

d

o

v

3

+

C

g

s

o

v

4

+

C

g

d

o

v

4

C_{g3} + C_{g4} = (WL)_3 C_{ox} + (WL)_4 C_{ox} + C_{gsov3} + C_{gdov3} + C_{gsov4} + C_{gdov4}

Cg3+Cg4=(WL)3Cox+(WL)4Cox+Cgsov3+Cgdov3+Cgsov4+Cgdov4 。

所以,等效电容为: C = 2 C g d 1 + 2 C g d 2 + C d b 1 + C d b 2 + C g 4 + C g 3 + C w C = 2C_{gd1} + 2C_{gd2} + C_{db1} + C_{db2} + C_{g4} + C_{g3} + C_w C=2Cgd1+2Cgd2+Cdb1+Cdb2+Cg4+Cg3+Cw |

【本文地址】

今日新闻 |

推荐新闻 |

为了方便计算,我们假设输入的激励是一个理想的阶跃函数,对应的响应如图:

为了方便计算,我们假设输入的激励是一个理想的阶跃函数,对应的响应如图: 因为这个电路是对称的,因此分析从低到高和从高到地是相似的。当

t

=

0

t = 0

t=0 的时候,此时

v

I

v_I

vI 从

0

0

0 上升至

V

D

D

V_{DD}

VDD 。此时

Q

P

Q_P

QP 截止而

Q

N

Q_N

QN 导通,如图:

因为这个电路是对称的,因此分析从低到高和从高到地是相似的。当

t

=

0

t = 0

t=0 的时候,此时

v

I

v_I

vI 从

0

0

0 上升至

V

D

D

V_{DD}

VDD 。此时

Q

P

Q_P

QP 截止而

Q

N

Q_N

QN 导通,如图: 我们发现,此时的输出端电压的起始值为

V

D

D

V_{DD}

VDD 。因此在

t

=

0

+

t = 0+

t=0+ 的时候

Q

N

Q_N

QN 处于饱和区,提供一个关于电容

C

C

C 的放电电流,下图展示了放电过程中,

i

D

N

i_{DN}

iDN 与

v

O

v_O

vO 的关系:

我们发现,此时的输出端电压的起始值为

V

D

D

V_{DD}

VDD 。因此在

t

=

0

+

t = 0+

t=0+ 的时候

Q

N

Q_N

QN 处于饱和区,提供一个关于电容

C

C

C 的放电电流,下图展示了放电过程中,

i

D

N

i_{DN}

iDN 与

v

O

v_O

vO 的关系: 在这里我们只关心

t

P

H

L

t_{PHL}

tPHL 时间,也就是上图中从点E到点M所需要的时间,在EF段,此时

Q

N

Q_N

QN 处于饱和区,超过F点之后,进入三极管区。

在这里我们只关心

t

P

H

L

t_{PHL}

tPHL 时间,也就是上图中从点E到点M所需要的时间,在EF段,此时

Q

N

Q_N

QN 处于饱和区,超过F点之后,进入三极管区。 我们将MOS管替换成一个等效的电阻,通过:

我们将MOS管替换成一个等效的电阻,通过: 这里

Q

1

Q_1

Q1 和

Q

2

Q_2

Q2 作为驱动CMOS反相器而

Q

3

Q_3

Q3 和

Q

4

Q_4

Q4 作为负载CMOS反相器,我们在这里只列出关于输出节点的电容,特别的

C

w

C_{w}

Cw 称为 线间电容 。

这里

Q

1

Q_1

Q1 和

Q

2

Q_2

Q2 作为驱动CMOS反相器而

Q

3

Q_3

Q3 和

Q

4

Q_4

Q4 作为负载CMOS反相器,我们在这里只列出关于输出节点的电容,特别的

C

w

C_{w}

Cw 称为 线间电容 。