LVDS |

您所在的位置:网站首页 › 80211a的最大传输速率 › LVDS |

LVDS

|

LVDS :Low-Voltage Differential Signaling 低电压差分信号 这种技术的核心是采用极低的电压摆幅高速差动传输数据,可以实现点对点或一点对多点的连接,具有低功耗、低误码率、低串扰和低辐射等特点,其传输介质可以是铜质的PCB连线,也可 以是平衡电缆。LVDS在对信号完整性、低抖动及共模特性要求较高的系统中得到了越来越广泛的应用。 LVDS为当今和未来的高带宽数据传输应用提供毫瓦每千兆位的方案 标准推荐的最高数据传输速率是655Mbps,而理论上,在一个无衰耗的传输线上,LVDS的最高传输速率可达1.923Gbps LVDS传输信号为平衡传输信号。TTL传输信号为非平衡传输信号。 终端匹配电阻标准规定为100Ω,由于恒流源为3.5mA,则摆动电平幅度为-350mV~350mV。由于偏置电压为1.2V,则差分信号的电压范围为850mV~1550mV。 - 通常大多数低速数字逻辑电平(如TTL、CMOS)是以电压对参考地的幅值来判断是高电平还是低电平,如下图所示:

而LVDS却完全不一样,它是通过数据接收器同相端与反相端的电压相对大小判断高低电平的,而不是通过同相端或反相端对公共地(GND)。

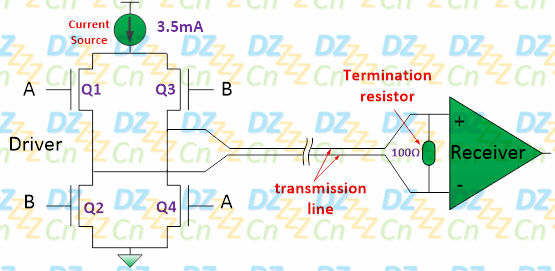

LVDS的发送器与接收器的基本结构如下图所示。它使用两根线(即差分信号线)来传输一个信号,并且使用恒流源(Current Source)驱动,即电流驱动型(而TTL、CMOS之类电平标准为电压驱动型)。

其中,驱动器(Driver)中的场效应管Q1、Q2、Q3、Q4(不一定是场效应管,因为LVDS技术规范主要侧重于LVDS接口的电气我、互连与线路端接,对于生产工艺、传输介质及供电电压无明确要求,也就是说,可以采用CMOS、GaAs或其它工艺实现,能抓到老鼠的黑猫白猫都是好猫)组成一个全桥开关电路,用来控制3.5mA恒流源的电流流动方向,接收器(Receiver)的同相与反相端之间并联了一个100欧姆的端接电阻,这样电流经过电阻即可产生电压,再经过接收器判断就形成了高低电平。

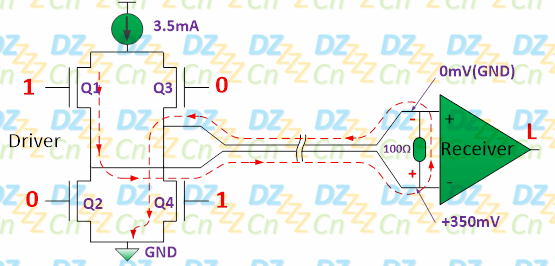

当Q2、Q3导通而Q1、Q4截止时,恒流源电流经Q3流向接收器,并向下穿过100欧姆端接电阻再返回至驱动端,最后经Q2到地(GND),3.5mA的电流在100欧姆电阻上产生350mV的压降,此时同相端电压高于反相端电压,输出为高电平“H”,如下图所示:

而当Q2、Q3截止而Q1、Q4导通时,恒流源电流经Q1向右流向接收器,并向上穿过100欧姆端接电阻再返回至驱动端,最后经Q4到地(GND),3.5mA的电流在100欧姆电阻上也产生350mV的压降,但此时同相端电压低于反相端电压,输出为高电平“L”,如下图所示:

通常我们将LVDS接收器与发送器简化成类似下图所示:

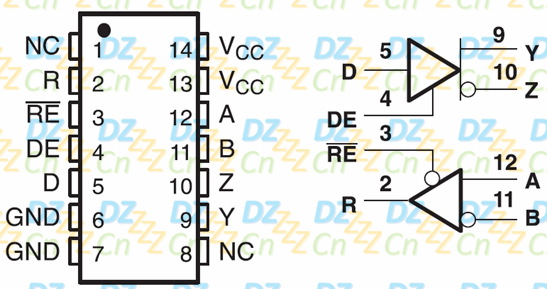

如下图所示(来自TI公司LVDS收发芯片SN65LVDS180数据手册)

从LVDS结构原理可以看出,一对差分信号线只能够进行一个方向的数据传输,即单工通信(也称为点对点传输,point-to-point),但是我们常见的USB接口也只是使用一对差分信号线,为什么却可以双向传输呢?原因很简单,它是使用两对驱动器与接收器组合而成的,如下图所示:

|

【本文地址】

今日新闻 |

推荐新闻 |