计数器芯片74ls193原理 |

您所在的位置:网站首页 › 74hc193引脚图及功能 › 计数器芯片74ls193原理 |

计数器芯片74ls193原理

|

计数器芯片74ls193原理_引脚图及功能_真值表_设计方法说明

来源:华强商城

发布时间:2020-06-30

分享到:

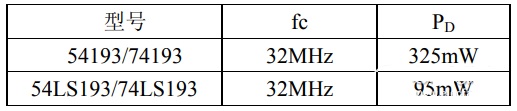

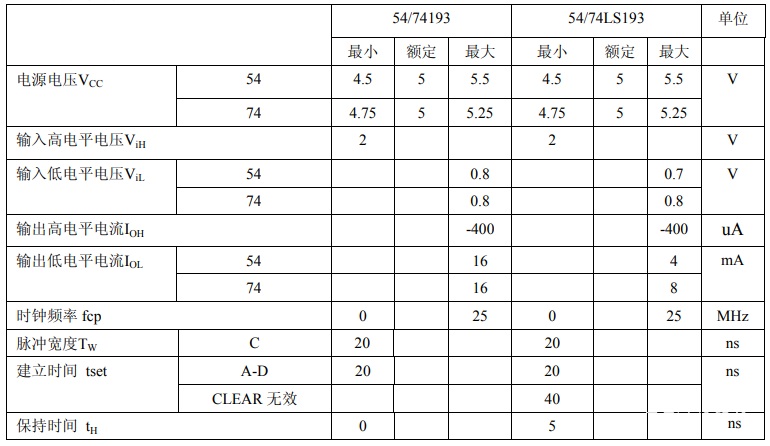

摘要: 本文将主要为大家介绍计数器芯片74ls193的工作原理、引脚图及功能、真值表、极限值、如何设计六进制加法计数器、逻辑图、时序图、静态特性和动态特性等方面的内容。 计数器芯片74ls193中文资料本文将主要为大家介绍计数器芯片74ls193的工作原理、引脚图及功能、真值表、极限值、如何设计六进制加法计数器、逻辑图、时序图、静态特性和动态特性等方面的内容。 74LS193芯片是同步四位二进制可逆计数器,它具有双时钟输入,并具有异步清零和异步置数等功能。 74ls193计数器工作原理193为可预置的十进制同步加/减计数器,共有54193/74193,54LS193/74LS193两种线路结构形式。其主要电特性的典型值如下:

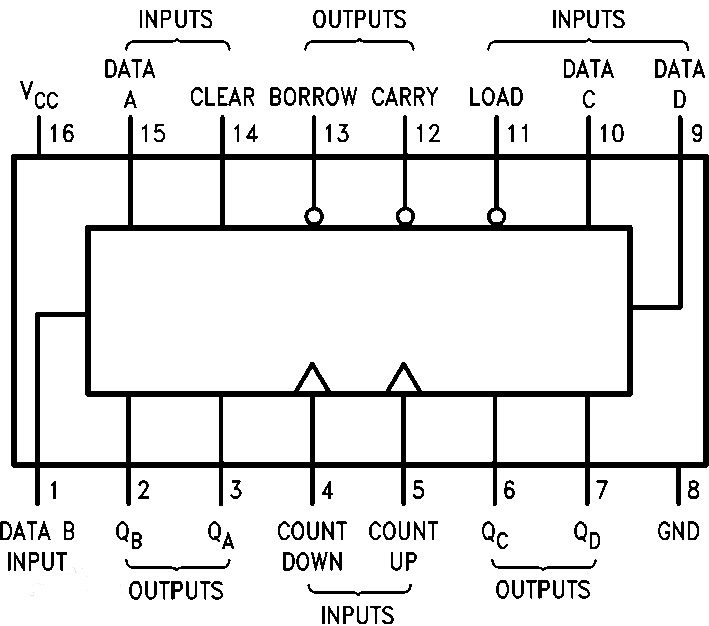

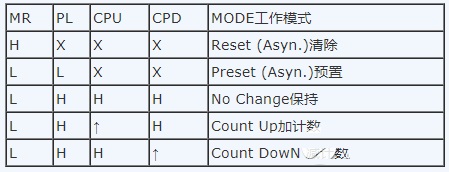

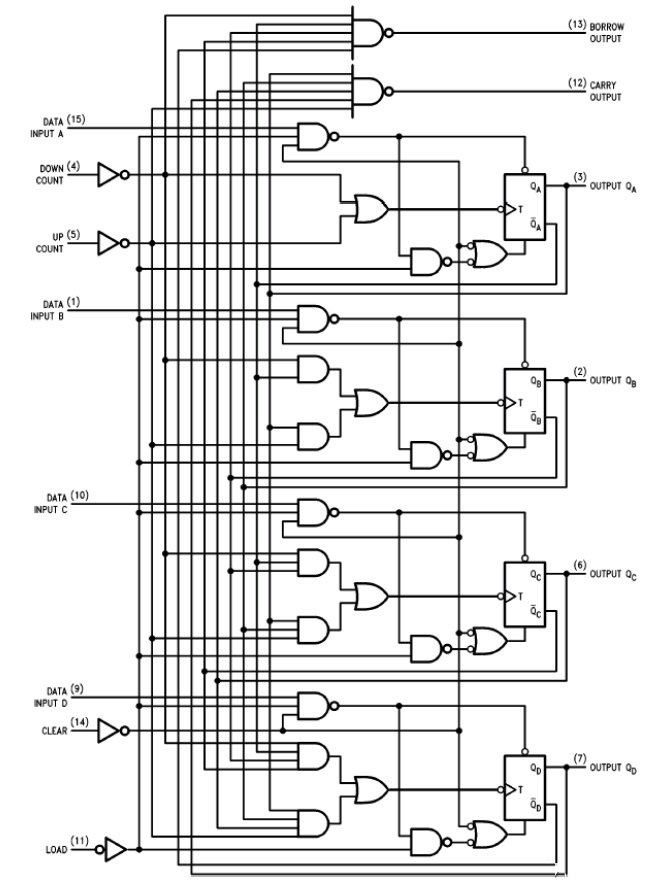

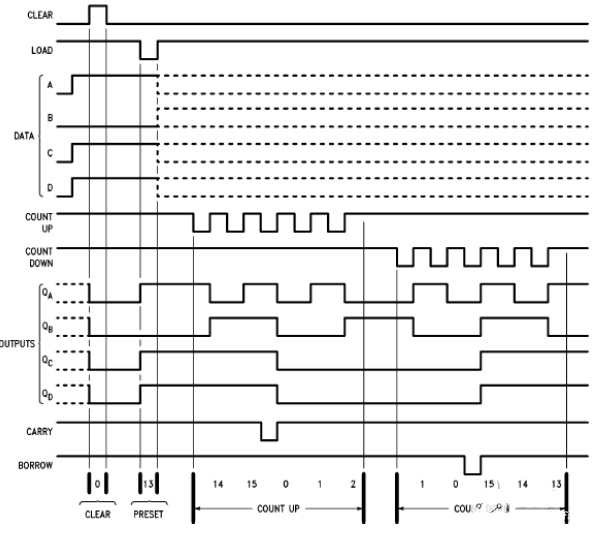

193的清除端是异步的。当清除端(CLEAR)为高电平时,不管时钟端(CDOWN、CUP)状态如何,即可完成清除功能。 193的预置是异步的。当置入控制端(LOAD)为低电平时,不管时钟(CDOWN、CUP)的状态如何,输出端(QA-QD)即可预置成与数据输入端(A-D)相一致的状态。 193的计数是同步的,靠CDOWN、CUP同时加在4个触发器上而实现。在CDOWN、CUP上升沿作用下QA-QD同时变化,从而消除了异步计数器中出现的计数尖峰。当进行加计数或减计数时可分别利用CDOWN或CUP,此时另一个时钟应为高电平。 当计数上溢出时,进位输出端(CARRY)输出一个低电平脉冲,其宽度为CUP低电平部分的低电平脉冲;当计数下溢出时,错位输出端(BORROW)输出一个低电平脉冲,其宽度为CDOWN低电平部分的低电平脉冲。 当把BORROW和CARRY分别连接后一级的CDOWN、CUP,即可进行级联。 74ls193引脚图

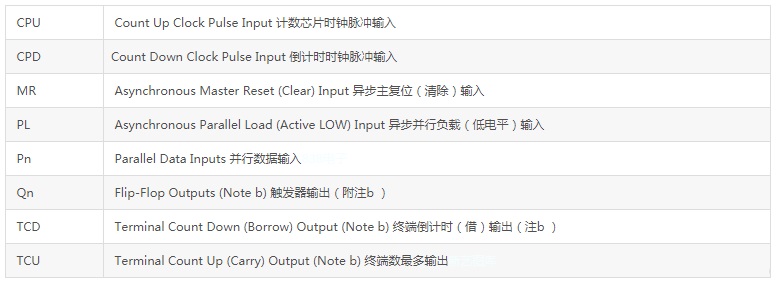

74ls193引脚说明: BORROW错位输出端(低电平有效) CARRY进位输出端(低电平有效) CDOWN减计数时钟输入端(上升沿有效) CUP加计数时钟输入端(上升沿有效) CLEAR异步清除端 A-D并行数据输入端 LOAD异步并行置入控制端(低电平有效) QA-QD输出端 74ls193功能

电源电压7V 输入电压 54/741935.5V 54/74LS1937V 工作环境温度 54&TImes;&TImes;&TImes;-55~125℃ 74&TImes;××0~70℃ 储存温度-65℃~150℃ 74ls193设计六进制加法计数器1.清零法: 当计数器计数到0100时=4,此时TCU输出为0,这就是复进位有效信号,因为是同步计数器,计数器要等待下一个时钟脉冲到来才会进制行清零,而此时正好计数到0101,而且又刚好清零。可通过百TPU连接一个反相器输出到MR实现清零。 2.置数法: 此时将MR接地,P0~P3接地。同样,当计数器计数到0100时=4,此时TPD=0,因为同步的原因,等待下一个时钟脉冲,直接度将TPD与PL相连即可。 74ls193逻辑图

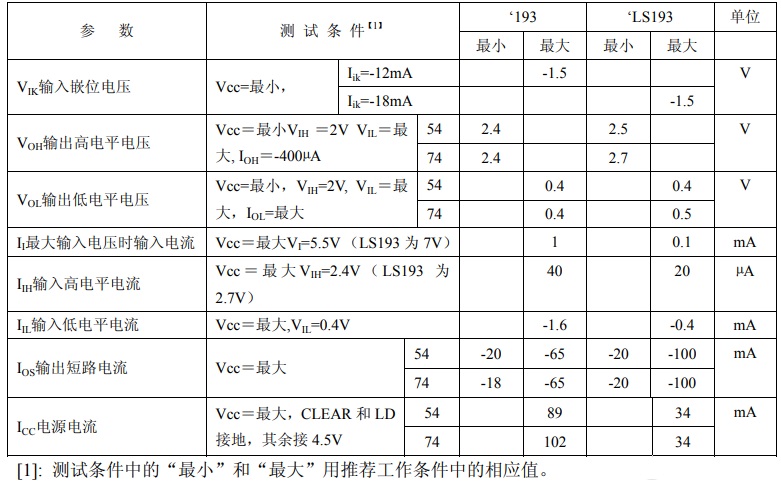

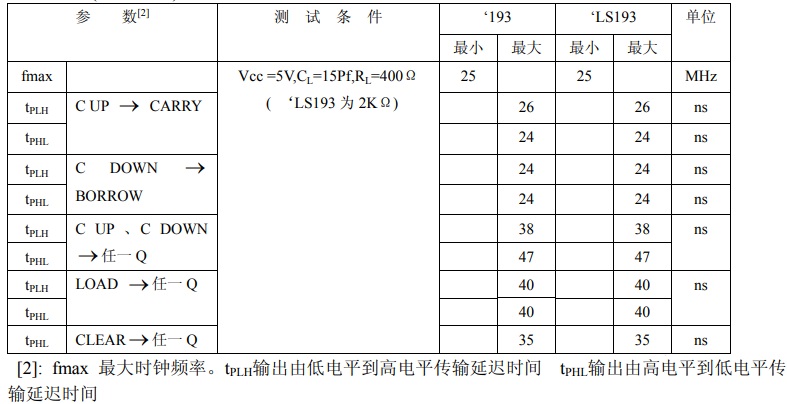

74ls193静态特性(TA为工作环境温度范围) 74ls193静态特性(TA为工作环境温度范围) 74ls193动态特性(TA=25℃) 74ls193动态特性(TA=25℃) 声明:本文观点仅代表作者本人,不代表华强商城的观点和立场。如有侵权或者其他问题,请联系本站修改或删除。

分享到:

声明:本文观点仅代表作者本人,不代表华强商城的观点和立场。如有侵权或者其他问题,请联系本站修改或删除。

分享到:

上一篇:什么是双绕组变压器? 下一篇:未来5年国产OLED屏幕市场规模将超越三星、LG

社群二维码

关注“华强商城“微信公众号 |

【本文地址】

今日新闻 |

推荐新闻 |