6. 【三态门】 74LS244 + 【锁存器】 74LS273 |

您所在的位置:网站首页 › 三态门的主要用途 › 6. 【三态门】 74LS244 + 【锁存器】 74LS273 |

6. 【三态门】 74LS244 + 【锁存器】 74LS273

|

文章目录

1. 三态门芯片 74LS244普通三态门三态门芯片 74LS244 内部图例子

2. 锁存器 74LS273

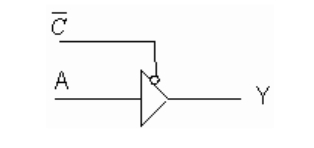

负责把信息从外部设备传入CPU 的接口(端口)叫做输入接口(端口), 而将信息从 CPU输出到外部设备的接口(端口)叫做输出接口(端口)。 在输入数据时,由于外部设备处理的时间一般比 CPU 要长的多,不可能让 CPU 一直等外设传完数据再工作吧。所以对输入接口的要求是:必须具有对数据的控制能力。 不必让外设一直向 CPU 传数据,让外设传入到输入接口,等数据准备好后,CPU开始读取时,才将数据传入 CPU。这样在外设传入数据的时候,CPU 就不用一直等,可以干其他活,等需要时,在发出读信号获取外设的数据。 典型的输入接口芯片是三态门芯片 74LS244。 在输出数据时,同样外设的速度比较慢,要使正确写入外设,CPU 输出的数据必须要保持一段时间,但这样对 CPU 来说是极大的浪费。所以对输出接口的要求是:必须具有对数据的锁存能力。 不必让 CPU 等待向外设传输数据的整个过程,通过向输出接口传输数据,让输出接口来为外设传输数据,就可以节约 CPU 的时间,让 CPU 干其他事情。 典型的输出接口芯片是锁存器 74LS273。 1. 三态门芯片 74LS244 普通三态门如下图所示,A 为输入端,Y 为输出端,C 为控制端。 当 C 为低电平,三态门导通,A 和 Y 之间导通; 当 C 为高电平,三态门不导通,为高阻状态,A 和 Y 之间不导通。

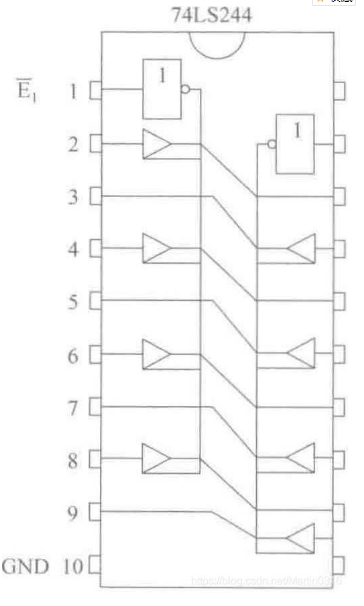

由8个三态门构成,有两个控制端 E1 和 E2。 每个控制端各控制四个三态门。当某一控制端有效(低电平)时,相应的四个三态门导通,否则为高阻状态(断开)。 实际应用中,通常将两个三态门并联,这样就可以用一个控制引号来使 8 个三态门同时导通或关断

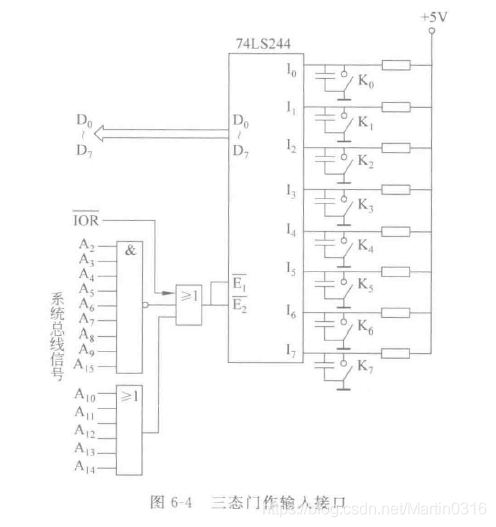

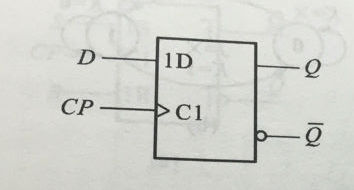

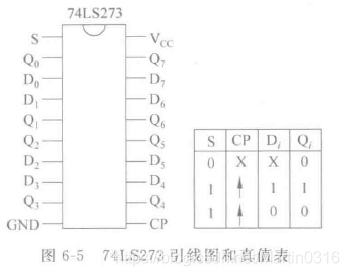

编写程序判断下图中的开关状态。如果所有开关都闭合,则程序转向 NEXT1 的程序段执行,否则转向 NEXT2。 再来分析整体电路: 当 CPU 不发出端口读信号时,#IOR为高电平,使能端 #E1 和 #E2 为高电平,三态门不导通。当 CPU 发出端口读信号时,#IOR为低电平,使能端为低电平,三态门导通,就可以由外设向 CPU 发送数据了。程序段如下: MOV DX ,83FCH IN AL, DX AND AL ,0FFH JZ NEXT1 JMP NEXT2 2. 锁存器 74LS273D触发器如下图所示。在每个上升沿,将 D 的状态所存到 Q 里。 常用的锁存器 74LS273 如图所示。 它内部包含8个 D 触发器。共有 8 个数据输入端(D0 ~ D7)和8个输出端(Q0 ~ Q7)。S为复位端,低电平有效。 CP 为脉冲输入端,在每个脉冲的上升沿将输出端 Di 的锁存到输出端 Qi 里,并将此状态保持到下一个时钟脉冲上升沿的到来。

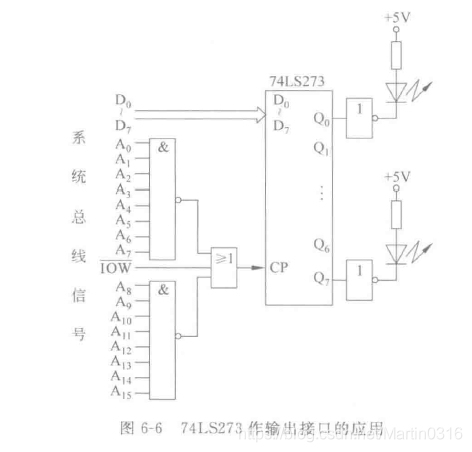

例子 8个 Q 端 与 8 个发光二极管相连接,编程使接到 Q0 端和 Q6 端的发光二极管发光。假设该输出接口的地址为 0FFFFH。 |

【本文地址】

今日新闻 |

推荐新闻 |

先来分析电路结构:

先来分析电路结构:

程序段如下:

程序段如下: