【精选】【高速PCB电路设计】8.DDR模块设计实战 |

您所在的位置:网站首页 › 高速pcb设计实战攻略pdf › 【精选】【高速PCB电路设计】8.DDR模块设计实战 |

【精选】【高速PCB电路设计】8.DDR模块设计实战

前言

本文主要记录DDR模块PCB实际设计当作的相关要点。关于DDR原理图设计的相关内容介绍链接: 【高速PCB电路设计】2.高速电路DDR原理图概述

之前一直找不到硬件题目来练习,老羡慕人家做软件的,最近发现牛客居然有硬件相关题目!这是链接,牛客网刷题(点击可以跳转),而且它登陆后会自动保存刷题记录,重新登录时不会又原地重练,我觉得这一点还挺好的。个人刷题练习系列专栏:个人CSDN牛客刷题专栏而且牛客的硬件板块还挺多的,包括FPGA等等,而CSDN相对硬件板块太少了,如下是牛客硬件专项题目位置:  文章目录

前言一、DDR特性介绍1.常见内存器件分类2.DDR技术发展及参数3.ODT4.动态ODT5.拓扑结构6.读写平衡(Write Leveling)7.伪开漏开路(POD)电平8.数据总线倒置(DBI)9.DDR5相对DDR4的升级点

二、DDR设计指南1.DDR模块常用拓扑结构2.多片DDR地址、控制线T型拓扑方案3.DDR3、4设计指南4.Fly-By拓扑布线参考

三、DDR设计实战(未完待续)1.DDR设计步骤2.DDR布线规则3.FPGA换Pin规则

总结结束语

一、DDR特性介绍

1.常见内存器件分类

文章目录

前言一、DDR特性介绍1.常见内存器件分类2.DDR技术发展及参数3.ODT4.动态ODT5.拓扑结构6.读写平衡(Write Leveling)7.伪开漏开路(POD)电平8.数据总线倒置(DBI)9.DDR5相对DDR4的升级点

二、DDR设计指南1.DDR模块常用拓扑结构2.多片DDR地址、控制线T型拓扑方案3.DDR3、4设计指南4.Fly-By拓扑布线参考

三、DDR设计实战(未完待续)1.DDR设计步骤2.DDR布线规则3.FPGA换Pin规则

总结结束语

一、DDR特性介绍

1.常见内存器件分类

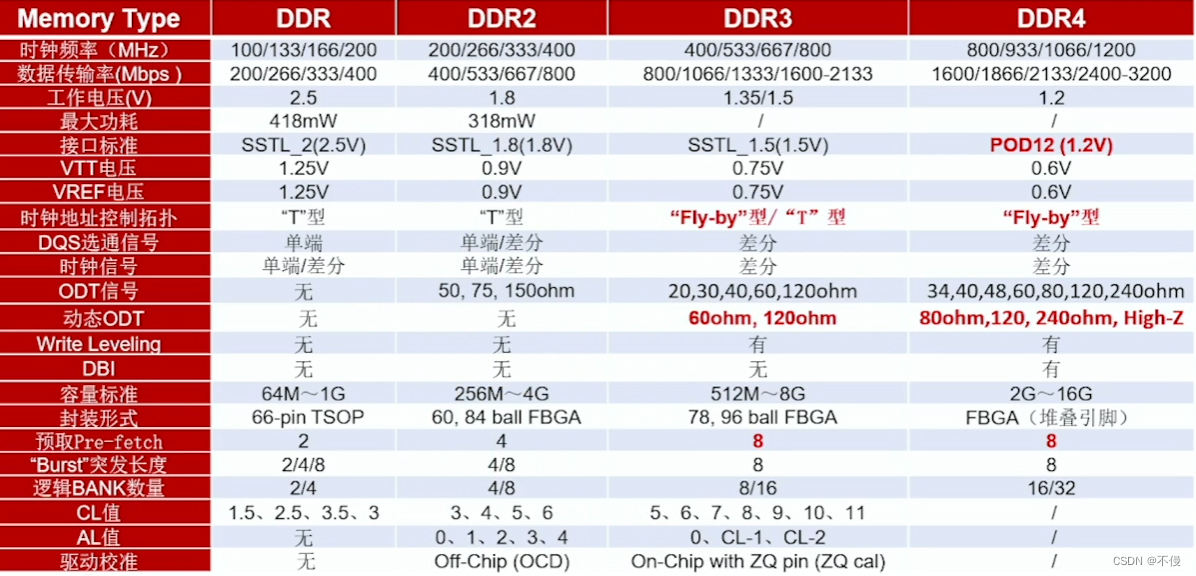

参考链接: 常见储存器件的分辨 2.DDR技术发展及参数 速率越来越高,电压越来越低。

DDR1的端接匹配都在外面。 DDR2开始端接匹配在芯片里。 ODT仅仅在数据线上有,地址线还是需要端接匹配。 4.动态ODT DDR3上有动态ODT,数据线是一驱二的情况下,同一颗粒工作于不工作的输入阻抗是不一样的,如此动态ODT能够进一步提高DDR3数据总线的信号质量,特别是在多个负载,例如:双内存条系统中。  5.拓扑结构

5.拓扑结构

如果颗粒数量比较少(通常小于4片),那么这两种拓扑的信号质量总体上就没有太大的差别;但如果DDR颗粒负载数量多的话(通常大于4片),采用Flyby的拓扑结构信号质量总体会比T型结构好。 下图是同样接了18片颗粒的情况下信号仿真眼图对比,采用Flyby的结果明显好于T型拓扑。   不支持读写平衡的DDR芯片不能用Fly-By,而应选用T型拓扑。 不支持读写平衡的DDR芯片不能用Fly-By,而应选用T型拓扑。

The following optional DDRx features are not supported: Read and Write levelingDDR Controller: DDR2 support up to DDR 800(40OMHz clock rate).DDR3 support up to DDR 1066(533MHz clock rate)1.5V or 1.8VI/o supply for DDR21.5V or 1.35VI/o support for DDR3Write leveling support for DDR332-bit and 16-bit bus withs 7.伪开漏开路(POD)电平 DDR4数据总线的I/O电气接口从推挽SSTL变为下图所示的伪开漏开路(POD)电平。通过截止到VDDQ而不是1/2的VDDQ,信号摆动的幅值和中心可根据不同设计的需要定制。POD的I/O降低了驱动数据时的开关电流,因为只有0时才消耗功率,相对DDR3的推挽式lO口,理论上功耗会降低一半。  8.数据总线倒置(DBI)

根据POD的特性,当数据为高电平时,没有电流流动,所以降低DDR4功耗的一个方法就是让高电平尽可能多,这就是DBI技术的核心。即当有一般数据位位低时,DBI进行翻转,以保证降低功耗。DBI与掩码常共用管脚,需根据需要选择。

8.数据总线倒置(DBI)

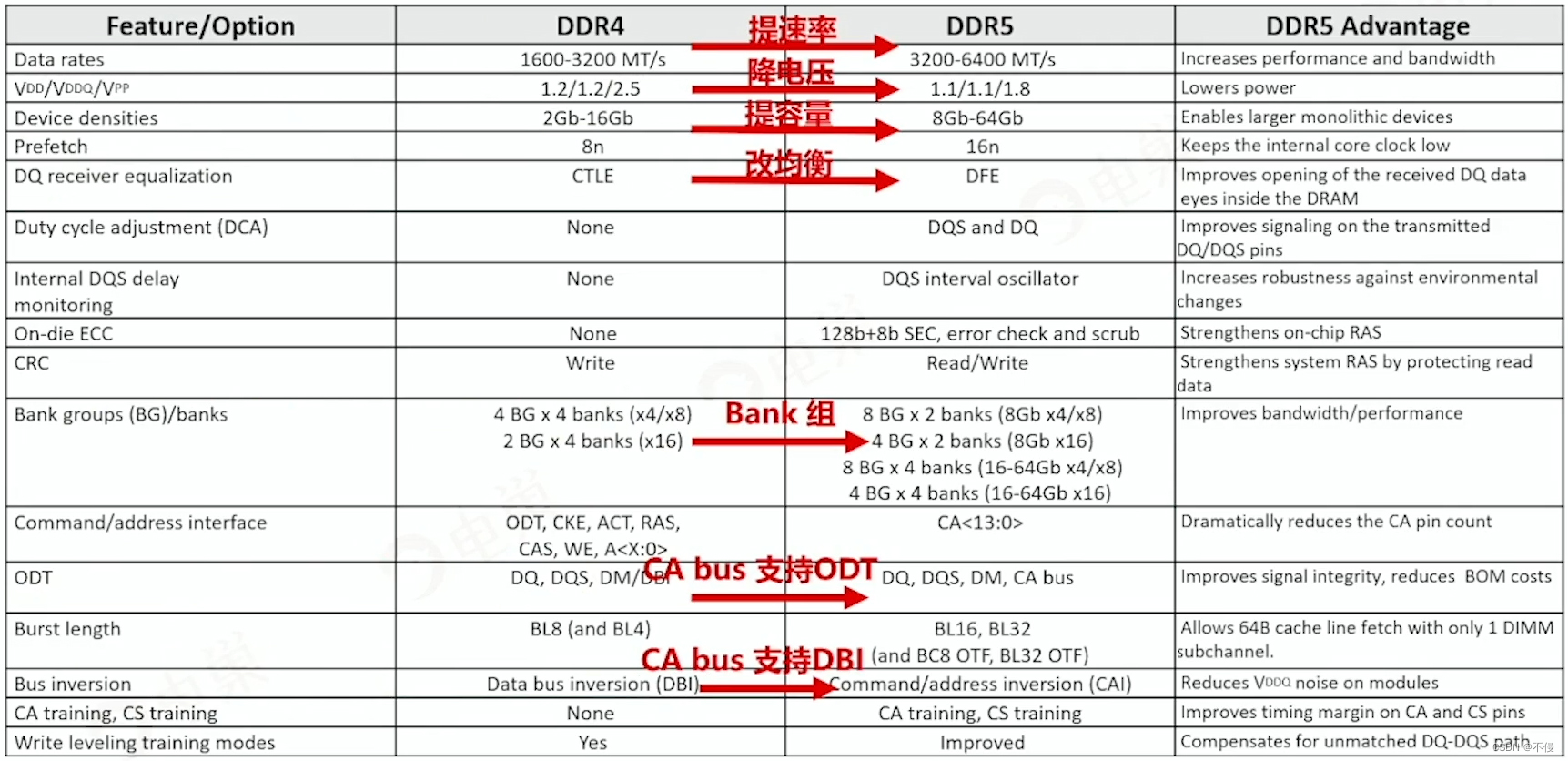

根据POD的特性,当数据为高电平时,没有电流流动,所以降低DDR4功耗的一个方法就是让高电平尽可能多,这就是DBI技术的核心。即当有一般数据位位低时,DBI进行翻转,以保证降低功耗。DBI与掩码常共用管脚,需根据需要选择。  9.DDR5相对DDR4的升级点

9.DDR5相对DDR4的升级点

四片DDR:A:T型与菊花链拓扑相结合;B:树型(T型)拓扑,主干线较短不是远端簇型拓扑;C:T型与远端簇型拓扑相结合(较好),主干线较长;D:Fly-By拓扑(时钟和数据时序偏差不严时,该拓扑是最好的,故不适用DDR2特别是颗粒多时,DDR3也要看主控能不能支持)。 四片DDR:A:T型与菊花链拓扑相结合;B:树型(T型)拓扑,主干线较短不是远端簇型拓扑;C:T型与远端簇型拓扑相结合(较好),主干线较长;D:Fly-By拓扑(时钟和数据时序偏差不严时,该拓扑是最好的,故不适用DDR2特别是颗粒多时,DDR3也要看主控能不能支持)。  2.多片DDR地址、控制线T型拓扑方案

4片DDR地址、控制线T型拓扑方案

2.多片DDR地址、控制线T型拓扑方案

4片DDR地址、控制线T型拓扑方案  DRAM离Controller尽量近TL1尽量长,在远处分支对称结构,保证所有到DRAM的走线等长: 时序匹配、减少反射减少平行走线,抑制串扰根据仿真结果决定是否需要VTT匹配电路(压缩走线长度,尽量省掉VTT匹配)。 DRAM离Controller尽量近TL1尽量长,在远处分支对称结构,保证所有到DRAM的走线等长: 时序匹配、减少反射减少平行走线,抑制串扰根据仿真结果决定是否需要VTT匹配电路(压缩走线长度,尽量省掉VTT匹配)。

T型拓扑阻抗控制方案: 为了保证阻抗连续,理论上要尽可能保证分支并联阻抗等于主干线阻抗。但PCB主干线线宽很难达到,故没那么严。 2颗DDR同层贴布线示例(T点在中间,过孔可打4排,每边2排) 4颗DDR同层贴布线示例(T点在中间,中间4排孔,两边4排孔) 4颗DDR正反贴布线示例(T点在中间,都是两排孔,末梢T点分支线短,反射小(此点优于单面);因为孔太多打孔位置从数据地址往外推。) 成本多,可在连个第二个T点都加上拉VDT匹配,否则在第一个T点位置加VDT匹配。 3.DDR3、4设计指南地址线(数据线、时钟线、命令线)布局布线优先Fly-By; 地址、命令、控制信号的走线拓扑结构,以及终端电阻RTT的位置,RTT值一般为39Ω。 使用FlyBy拓扑,并以60Ω端接,在第一个和最后一个DDR SDRAM颗粒die上看到的命令和地址线的仿真波形如下。(注:FlyBy拓扑上最后一颗DDR上的波形是最好的。因为最后一颗只有最后一部分的反射,且有终端匹配吸收反射。) 以60欧姆端接会导致第一个波形(绿色信号)的信号闭眼,而对最后一个波形(红色信号)的信号没有影响。为优化设计,可以通过仿真模拟来确定合适的电阻值。 DDR3、4布线指南:   4层4片DDR3,Fly-By不费层。 4层4片DDR3,Fly-By不费层。  5片DDR3正反错位贴片: 5片DDR3正反错位贴片:  8片DDR3正反贴片: 8片DDR3正反贴片:  三、DDR设计实战(未完待续)

1.DDR设计步骤

三、DDR设计实战(未完待续)

1.DDR设计步骤

0 2.DDR布线规则0 3.FPGA换Pin规则0 总结0 结束语 以上就是DDR模块设计实战的内容。再次推荐牛客网刷题(点击可以跳转)的硬件刷题板块。

|

【本文地址】