基于mips指令集的处理器设计与实现 |

您所在的位置:网站首页 › 饰品指的是什么 › 基于mips指令集的处理器设计与实现 |

基于mips指令集的处理器设计与实现

|

目录:

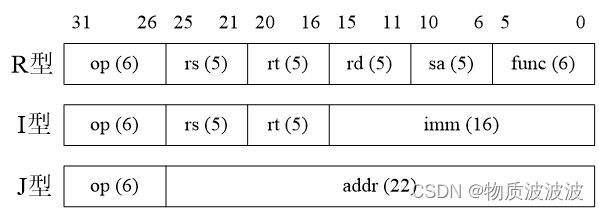

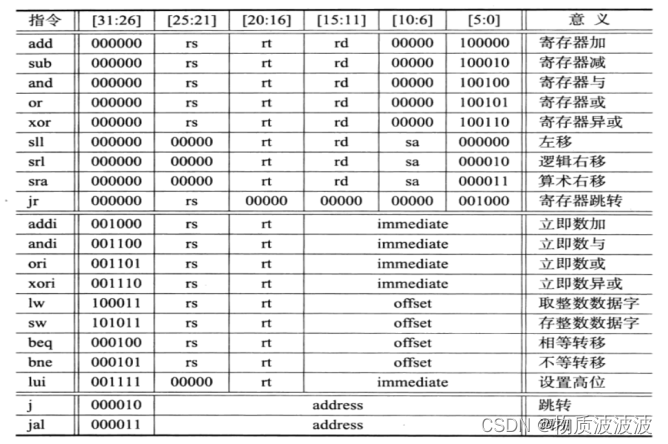

一.MIPS指令集架构

1.mips指令集格式 2.mips寄存器特点 二.单周期MIPScpu_core架构设计 三.子模块结构分析(含Icache)1.ALU模块 2.General_Register模块(通用寄存器) 3.instruction_cache模块(指令cache) 4.program_counter模块(程序计数器) 5.control模块(控制译码) 四.详细设计流程与机器指令验证 一.MIPS指令集架构MIPS是(Microcomputer without interlocked pipeline stages)的缩写,含义是无互锁流水级微处理器。MIPS 是最早的,最成功的RISC处理器之一,源于Stanford 大学的John Hennessy 教授的研究成果。(Hennessy 于1984年在硅谷创建了MIPS公司)。MIPS的指令系统经过通用处理器指令体系MIPS I、 MIPS II、MIPS III、MIPS IV到MIPS V,嵌入 式指令体系MIPS16、MIPS32到MIPS64的发展 已经十分成熟。应用广泛的32位MIPS CPU包括R2000,R3000 其ISA都是MIPS I,另一个广泛使用的、含有许多 重要改进的64位MIPS CPU R4000及其后续产 品,其ISA版本为MIPS III。 1.mips指令集格式 MIPS 32位处理器的指令格式分为R型、I型和J型。R型为寄存器型,即两个源操作数和目的操作数都是寄存器性。I型为操作数含有立即数。而J型特指转移类型指令,如图1所示。 图1 MIPS指令类型 常见的20条MIPS整数指令如下所示:Mips体系结构下的指令都是32位,且其为RISC处理机,特点为指令等长,没有类似x86架构的变长指令。 表 1 20条MIP整数指令 这是设计整个处理机结果的编码依据 可以发现:mips指令集的特点为: R型指令op字段(Instruction[31..26])必为0 I型指令op字段非0。 这是区别指令类型的标志。2.mips寄存器特点 Mips体系结构下的寄存器都是32位,且其为RISC处理机,特点为寄存器很多,以减少访存的发生。 而0–31共32个寄存器,对应地址为五位通用寄存器地址码,可以发现RS、RT、RD寄存器指令都是五位字长。

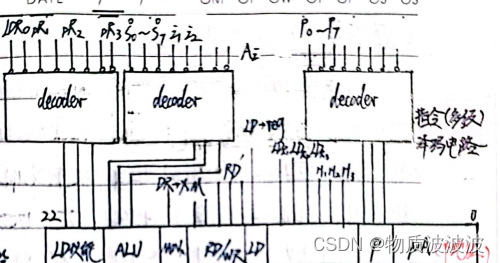

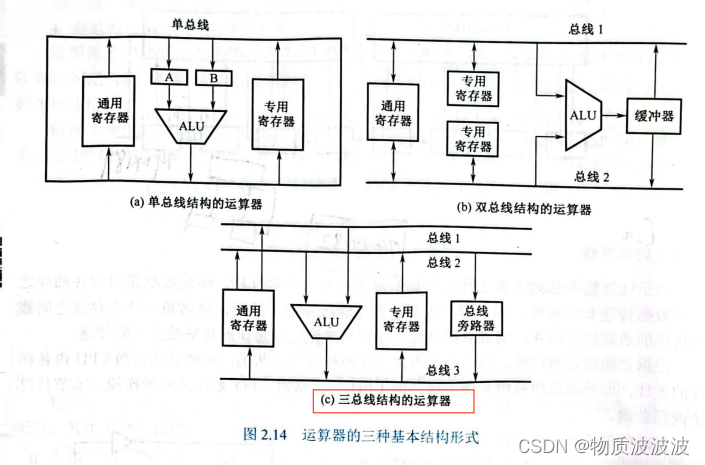

图2 寄存器结构 二.单周期MIPScpu_core架构设计 在此先讨论单周期MIPS处理机的设计:由于读写要在同一个执行周期(即时钟周期)内完成,故cpu必须选择三总线(内总线)结构:如下图,对于单总线、双总线结构:由于数据通路必须分时复用,故只能采用多周期实现。而三总线结构有两个源数据总线,和一个目标数据总线(5bit宽),故可以在一个周期内执行结束;而对一条指令的执行,采用硬布线结构设计:将ICache中读出的指令按MIPS指令的规定译码,就可以完成对各部件的控制。(结构如下所示) 译码的结果是产生一系列微命令信号

图4 指令控制单元结构 三.子模块结构分析(含Icache)1.ALU模块 alu是处理机的核心运算部件,一定要功能强大,故设计32位ALU,五位方式码,共可以实现19种算术逻辑运算模式 module ALU(clk, input_data1, input_data2, output_data,ctrl_sinal, sinal); input clk; input [31:0] input_data1; input [31:0] input_data2; input [4:0] ctrl_sinal; output [31:0] output_data; output sinal; reg sinal; reg [31:0] output_data; parameter ALU_add = 5'b00001; //加法 parameter ALU_sub = 5'b00010; //减法 parameter ALU_mul = 5'b00011; //乘法 parameter ALU_div = 5'b00100; //除法 parameter ALU_mod = 5'b00101; //取余 parameter ALU_and = 5'b00110; //与 parameter ALU_or = 5'b00111; //或 parameter ALU_not = 5'b01000; //非 parameter ALU_xor = 5'b01001; //异或 parameter ALU_xnor= 5'b01010; //同或 parameter ALU_nor = 5'b01011; //或非 parameter ALU_nand= 5'b01100; //与非 parameter ALU_sll = 5'b01101; //逻辑左移 parameter ALU_srl = 5'b01110; //逻辑右移 parameter ALU_sra = 5'b01111; //算术右移 parameter ALU_sla = 5'b10000; //算术左移 parameter ALU_slt = 5'b10001; //小于则置'1' parameter ALU_lui = 5'b10010; //左移16位 parameter ALU_comparer = 5'b10011; //条件相等 always @(posedge clk) begin case(ctrl_sinal) 5'b00000: output_data=input_data1; ALU_add : begin output_data = input_data1+input_data2; sinal = 1; end ALU_sub : begin output_data = input_data1-input_data2; sinal = 1; end ALU_mul : begin output_data = input_data1*input_data2; sinal = 1; end ALU_div : begin output_data = input_data1/input_data2; sinal = 1; end ALU_mod : begin output_data = input_data1%input_data2; sinal = 1; end ALU_and : begin output_data = input_data1&input_data2; if(input_data1 == input_data2) sinal = 1; else sinal = 0; end ALU_or : begin output_data = input_data1|input_data2; sinal = 1; end ALU_not : begin output_data =~input_data1; sinal = 1; end ALU_xor : begin output_data = input_data1^input_data2; sinal = 1; end ALU_xnor : begin output_data = input_data1^~input_data2; sinal = 1; end ALU_nor : begin output_data = ~(input_data1|input_data2); sinal = 1; end ALU_nand : begin output_data = ~(input_data1*input_data2); sinal = 1; end ALU_slt : begin output_data = (input_data1 >> input_data1; sinal = 1; end ALU_sla : begin output_data = ($signed(input_data2)) |

【本文地址】

图3 运算器基本结构

图3 运算器基本结构