【FPGA】数码管电子时钟(可设置时间和闹钟) |

您所在的位置:网站首页 › 闹钟设置响铃时间怎么设置 › 【FPGA】数码管电子时钟(可设置时间和闹钟) |

【FPGA】数码管电子时钟(可设置时间和闹钟)

|

目录

前言一丶需求分析1.设置时间2.设置闹钟

二丶工程源码1.counter2.seg_driver3.key_debounce4.beep5.顶层模块

三丶模块原理图四丶管脚信息五丶上板验证六丶源码

前言

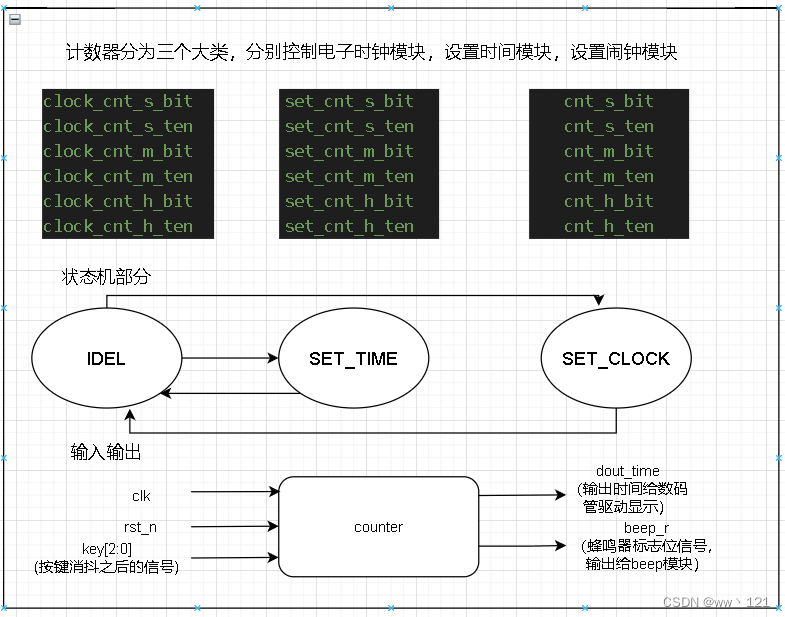

本次实验内容承接上一篇文章数码管电子时钟,在此基础上新增两个功能: 1.设置时间 2.设置闹钟,到点响铃 一丶需求分析模块:beep counter seg_driver top 其中: 1.设置时间 2.设置闹钟,到点响铃 这两个功能都整合在counter模块,里面设置的重要信号如下所示 我们需要利用开发板上的按键来设置时分秒HH:MM:SS 思路: Counter: rst_n:复位按键 【相当于开发板上的key1】 Key[0]:空闲状态—电子时钟 【相当于开发板上的key1】 Key[1]:设置时间 【相当于开发板上的key2】 Key[2]:设置闹钟 【相当于开发板上的key3】 按键切换三个状态: 1.空闲状态—就是一个时钟 输出dout_time给seg_driver模块显示时间 2.设置时间—设置当前的时分秒,改一下几个计时器里面的初值 修改counter里面的6个计时器的值,暂停计时 Key[0]:切换修改的时间位,切换到哪一位,哪一位闪烁 【相当于开发板上的key2】 Key[1]:加1 【相当于开发板上的key3】 Key[2]:确定–退出 【相当于开发板上的key4】 3.设置闹钟—设置个条件,到几时几分几秒蜂鸣器响 修改counter里面的6个计时器的值,暂停计时 Key[0]:切换修改的时间位,切换到哪一位,哪一位闪烁 【相当于开发板上的key2】 Key[1]:加1 【相当于开发板上的key3】 Key[2]:确定–退出(确定之后输出dout_time给beep模块作为响铃时间) 【相当于开发板上的key4】 2.设置闹钟方式与设置时间基本完全一样,区别在设置闹钟的时间不给电子时钟,电子时钟保持设置的时间计时 二丶工程源码 1.counter module counter ( input wire clk , input wire rst_n , input wire [2:0] key , output reg [19:0] dout_time , //输出时间 HH:MM:SS output wire beep_r ); //计数器 reg [25:0] cnt ; wire add_cnt; wire end_cnt; //S计时器 //个位 (0~9) reg [3:0] cnt_s_bit; wire add_cnt_s_bit; wire end_cnt_s_bit; reg [3:0] set_cnt_s_bit; wire add_set_cnt_s_bit; wire end_set_cnt_s_bit; reg [3:0] clock_cnt_s_bit; wire add_clock_cnt_s_bit; wire end_clock_cnt_s_bit; //十位 (0~5) reg [2:0] cnt_s_ten; wire add_cnt_s_ten; wire end_cnt_s_ten; reg [2:0] set_cnt_s_ten; wire add_set_cnt_s_ten; wire end_set_cnt_s_ten; reg [2:0] clock_cnt_s_ten; wire add_clock_cnt_s_ten; wire end_clock_cnt_s_ten; //M计时器 //个位 (0~9) reg [3:0] cnt_m_bit; wire add_cnt_m_bit; wire end_cnt_m_bit; reg [3:0] set_cnt_m_bit; wire add_set_cnt_m_bit; wire end_set_cnt_m_bit; reg [3:0] clock_cnt_m_bit; wire add_clock_cnt_m_bit; wire end_clock_cnt_m_bit; //十位 (0~5) reg [2:0] cnt_m_ten; wire add_cnt_m_ten; wire end_cnt_m_ten; reg [2:0] set_cnt_m_ten; wire add_set_cnt_m_ten; wire end_set_cnt_m_ten; reg [2:0] clock_cnt_m_ten; wire add_clock_cnt_m_ten; wire end_clock_cnt_m_ten; //H计时器 //个位 (0~9) reg [3:0] cnt_h_bit; wire add_cnt_h_bit; wire end_cnt_h_bit; reg [3:0] set_cnt_h_bit; wire add_set_cnt_h_bit; wire end_set_cnt_h_bit; reg [3:0] clock_cnt_h_bit; wire add_clock_cnt_h_bit; wire end_clock_cnt_h_bit; //十位 (0~2) reg [1:0] cnt_h_ten; wire add_cnt_h_ten; wire end_cnt_h_ten; reg [1:0] set_cnt_h_ten; wire add_set_cnt_h_ten; wire end_set_cnt_h_ten; reg [1:0] clock_cnt_h_ten; wire add_clock_cnt_h_ten; wire end_clock_cnt_h_ten; reg [3:0] cnt_flag; reg [3:0] set_cnt_flag; reg [3:0] clock_cnt_flag; reg [2:0] state_c; //现态 reg [2:0] state_n; //次态 reg [5:0] select_seg; //在设置时间和设置闹钟的时候切换位选 wire [19:0] set_time_dout; wire [19:0] idel_dout; wire [19:0] clock_dout; parameter MAX_CNT=26'd50_000_000; //定义状态 localparam IDEL =3'b001, //空闲状态 SET_TIME =3'b010, //设置时间 SET_CLOCK=3'b100; //设置闹钟 //状态转移条件 wire idel_TO_set_time; wire idel_TO_set_clock; wire set_time_TO_idel; wire set_clock_TO_idel; //状态机第一段--状态转移 always @(posedge clk or negedge rst_n) begin if (!rst_n) begin state_c |

【本文地址】

今日新闻 |

推荐新闻 |