NOR FLASH 闪存及基本原理 |

您所在的位置:网站首页 › 闪存用在哪 › NOR FLASH 闪存及基本原理 |

NOR FLASH 闪存及基本原理

|

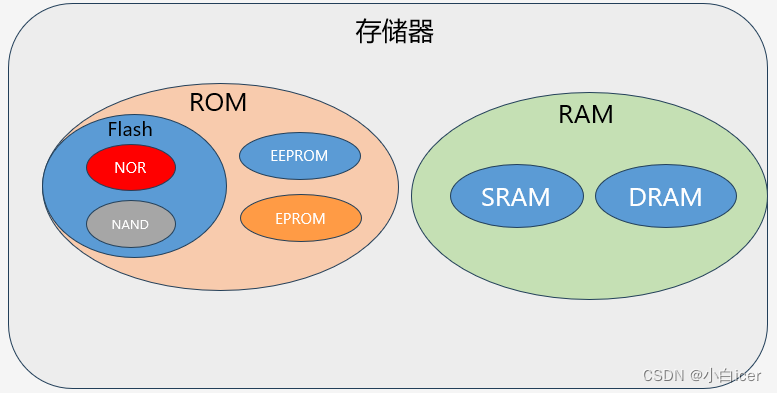

目录 一、介绍 二、NOR Flash结构和原理 2.1 Read 2.2 Program 2.3 Erase 2.4 电压阈值曲线 2.5 过擦 一、介绍存储器是用来存储数据和程序的设备,存储器分类如下图所示:主要分为RAM和ROM。RAM叫做随机访问存储器(Random Access Memory),主要包括了SRAM和DRAM;ROM叫做只读存储器(Read Only Memory),主要包括了Flash、EPOM和EEPROM等。

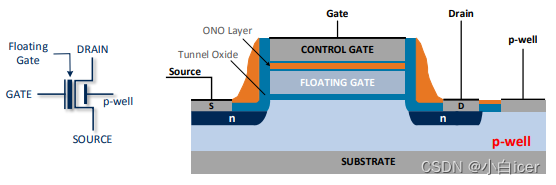

RAM存储器特点是可以从任意一个地址写入或者读出数据,但掉电数据易丢失。SRAM(Satic RAM)静态随机访问存储器通常用于计算机的高速缓存,速度快。DRAM(Dynamic RAM)动态访问存储器通常用于计算机的内存,例如DDR。 ROM存储器特点是CPU 只能读取存储在 ROM 中的数据或指令,无法对存储的数据做修改,更无法写入新的数据,但是掉电数据不易丢失。ROM经历了PROM->EPROM->EEPROM的发展阶段,从一次性可编程,到可编程可擦除,再到带电可编程可擦除,性能越来越强大。Flash闪存是一种高级版的EEPROM。Flash又分为NOR和NAND两大类, NOR Flash闪存是由Intel公司开发的,具有专用的地址和数据线(和SRAM类似),以字节的方式进行读写,允许对存储器当中的任何位置进行访问。NAND Flash经常用于计算机的固态硬盘SSD。本文主要介绍NOR Flash。 二、NOR Flash结构和原理Flash利用三端器件为存储单元,分别是源级、漏级和栅级。和场效应管的工作原理一样,利用电场的效应来控制源漏级的通断。不同场效应管的是,Flash增加了浮置栅极,浮置栅极是由氮化物夹在两层二氧化硅材料之间构成的,中间的氮化物就是可以存储电荷的电荷势阱 。 存储器的基本存储元件(单元)由具有“浮栅”的MOSFET组成。这个被捕获在存储器单元的浮栅内部的电荷量定义了该单元是否已编程或已擦除。

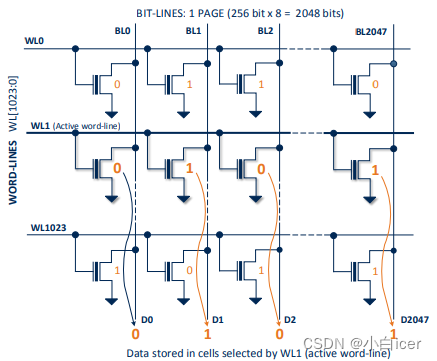

为了存储大量信息,闪存被组织成存储单元的阵列。这个存储器阵列是N行乘M列的矩阵。在每一行一列的交叉点上正好有一个存储器单元(具有浮置栅极的MOSFET)。这个MOSFET存储一位信息。行就是常说的字线WL,列就是位线BL。

硅制造要求所有的存储单元都建立在一个共同的基础上,称为衬底。为了使存储器操作更易于管理,在衬底中植入了一系列p阱。这些p阱彼此电绝缘,称为公共p阱。存储器单元的阵列被嵌入到公共p阱中。每个p阱都有自己的电极,允许其在存储器控制器的控制下用特定电压偏置。 对NOR Flash主要有三种操作:读、写、擦。下面会分别介绍这三种操作,需要注意的是编程之前要执行擦除操作。 2.1 Read要确定单元的状态(无论是编程还是擦除),必须读取单元的内容。这是通过施加连接到MOSFET的GATE的大约5.5V的参考电压来实现的,这被称为“参考阈值电压”,用VTREF表示。

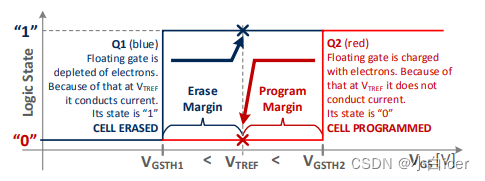

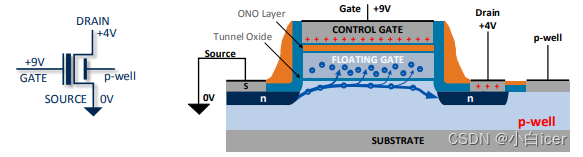

如果处于Q1即被擦除状态,此时浮栅中的电子已耗尽,栅源GS之间的阈值电压小于参考阈值电压,此时源漏加正向电压,源漏之间形成电流,MOSFEAT导通,处于逻辑1。如果处于Q2状态,浮栅中充满被捕获的电子,栅源GS之间的阈值电压大于参考阈值电压,MOSFEAT不导通,处于逻辑0。 2.2 Program编程时,在栅极和漏极加上正向电压,源极接地,此时电子会从源极流向漏极,形成很大的电流,由于栅极加正向电压,这些电子会穿过二氧化硅层到达浮栅,形成电子团。这个过程也叫做热电子注入。

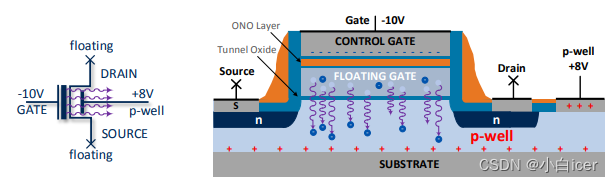

擦除时,在p阱加正向电压,在栅极加负向电压,源漏级浮空,此时电子会从浮栅中逃逸,浮栅电子被耗尽,降低了阈值电压。

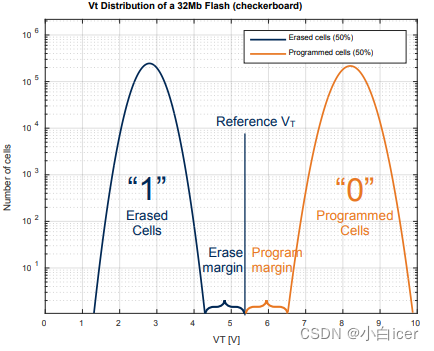

Program相比较Erase操作还是更快的,Program通常通过施加编程脉冲反复执行。每个编程脉冲将一定数量的电子注入到浮置栅极中。Erase本质上是从浮栅中捕获电子穿过氧化层的过程,且针对的是Block进行擦除的动作,因此持续的时间较长。 2.4 电压阈值曲线电压阈值曲线是为了更好描述擦除和编程时cell 的数量的图形,当浮栅中电子足够多,此时电压阈值就更高,当浮栅中电子耗尽时,此时电压阈值就低。电压阈值曲线如下图所示,编程时阈值电压较高,而擦除时阈值电压较低,中间是参考的阈值电压,该电压被用于选择WL。

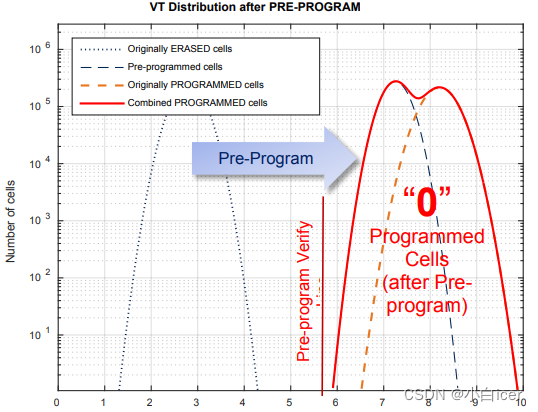

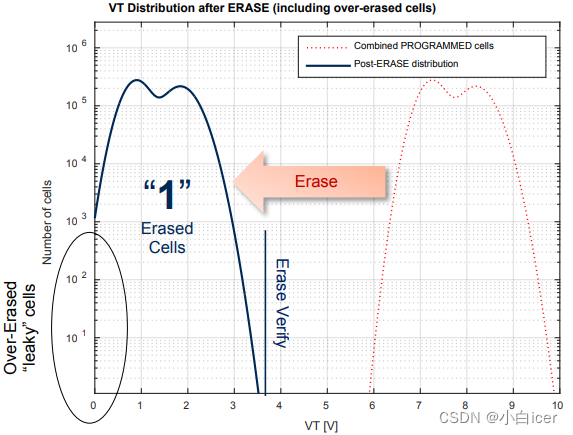

在擦除期间,也会并行地擦除多个比特,因此VT的分布可能相当大。存储单元有可能进入过擦除状态。过擦除单元即使在其栅极电压接近0V时也传导少量电流;这被称为漏电流。由于共享的位线,这样的状态对于NOR闪存架构是有问题的必须避免。 2.5 过擦在NOR闪存的使用寿命期间,设备会被多次擦除和编程。在该过程中,VT分布变化是因为单个细胞的状态从PROGRAMMED变为被擦除,反之亦然。为了保持具有良好裕度的良好VT分布,擦除操作分三个不同阶段进行: 1.预编程阶段 2.擦除阶段 3.恢复阶段 过擦就是原本已经擦除的区域,在进行擦除时,此时阈值曲线仍然会向左移,即使栅极电压为0V时。为了防止出现过擦,首先对已经擦除的单元进行预编程,预编程的目的是为了给擦除操作创造一个理想的条件。

擦除阶段如下图

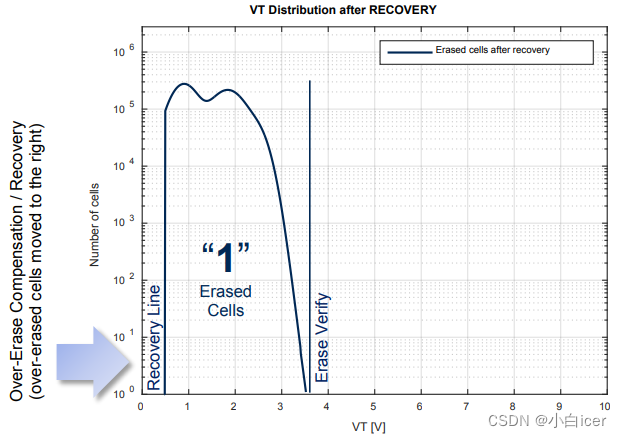

过擦除的单元被系统地软编程(在逐字节的基础上),直到它们的VT移位足够向右,使其从左侧穿过回收线,如图所示。恢复调整擦除阶段中被过度擦除的任何位的阈值。

当这些内部算法正在进行时,闪存的集成控制器会保留一个用户可读的状态位(状态寄存器中的BUSY/READY位)。该位指示正在进行的内部操作是否已经完成。用户不得重置设备、断开芯片电源或中断擦除在BUSY位被设置时以任何方式操作。 如果擦除操作因重置设备或关闭和打开其电源而中断擦除操作的三个阶段没有机会完成,这可能会留下内存未定义的状态。因此目标块中的比特可以处于三种状态中的任何一种:编程,擦除或过度擦除。在这种情况下,可以安全地假设读取的数据不可信。 |

【本文地址】