【基础知识】时序(Slack、Setup、Hold、Jitter、Skew、亚稳态) |

您所在的位置:网站首页 › 钟表max什么意思 › 【基础知识】时序(Slack、Setup、Hold、Jitter、Skew、亚稳态) |

【基础知识】时序(Slack、Setup、Hold、Jitter、Skew、亚稳态)

|

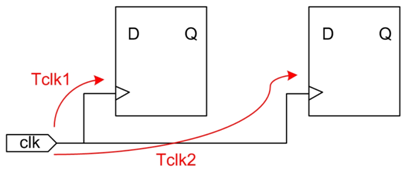

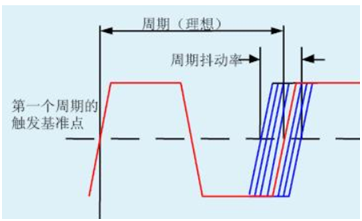

时钟信号特性有:抖动(Jitter)、偏移(skew)、占空比失真(Duty Cycle Distortion) 偏移SKEW 因时钟线长度不同或负载不同,导致时钟到达相邻单元的时间不同,这个时间上的偏差就叫时钟偏移SKEW。 在上图中的Tskew=Tc1-Tc2 偏移会一直存在,因此FPGA在设计时,会进行优化,采用全铜工艺和树状结构,设计专门的始终缓冲和驱动网络,使得时钟到达不同单元时的路径一样长,尽量减小偏移。 所以,Skew 问题的解决方法就是:设计中的主要信号应该走全局时钟网络。 此外FPGA中延迟锁定环(Delay locked ring,DLL)也可以去SKEW,延迟锁相环由控制逻辑和延时线组成,控制逻辑将输入时钟与输出时钟进行比较,并插入延时从而使得时钟同步。 但无论如何,在STA时,任然要考虑Skew。 抖动Jitter 在理想情况下,一个频率固定的完美的脉冲信号(以1MHz为例)的持续时间应该恰好是1us,每500ns有一个跳变沿。但这种信号并不存在。如图所示,信号周期的长度总会有一定变化,从而导致下一个沿的到来时间不确定。这种不确定就是抖动(jitter)。时钟抖动也永远存在。 占空比失真Duty Cycle Distortion 占空比失真即时钟不对称,高电平和低电平时间发生变化。DCD会占用时间裕量(Slack)造成数字信号的失真,使过零区间偏离理想的位置。DCD通常是由信号的上升沿和下降沿之间时序不同而造成的。 扇入扇出Fan-in/Fan-out 数字电路中,逻辑门相互连接,每个逻辑门输出端与输入端都连着大量别的单元,因此由扇入扇出表示处理外部输入以及驱动外部其他单元的能力。

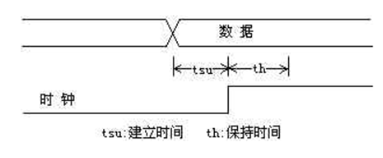

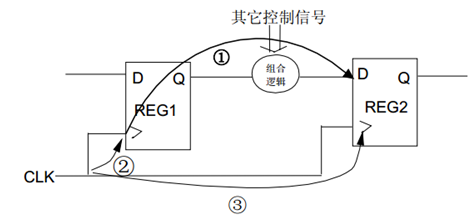

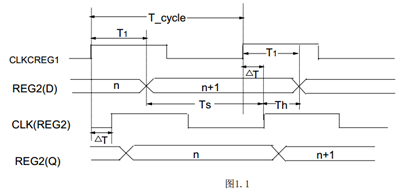

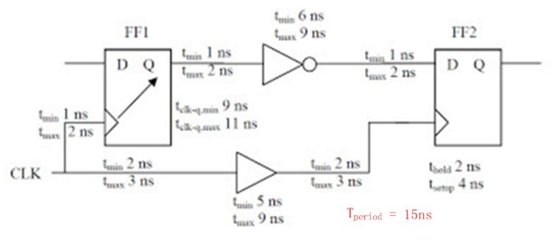

亚稳态及相关概念 同步电路中: 建立时间(Setup time):触发器时钟上升沿到来前数据保持稳定的时间。 保持时间(Hold time):触发器时钟上升沿到来后数保持据稳定的时间。 如图所示,在时钟上升沿到来前后的一段时间内数据必须保持稳定,否则数据就无法写入,造成“亚稳态“输出。如果前级驱动够强劲,电路就能按照趋势变化下去,一定时间后该点的值就会变化为“正确值”,如果驱动不够强劲,电路就会恢复之前的值,最终得到何值是不可控的,所以我们要避免亚稳态。在使用DFF时,必须满足其建立时间和保持时间的要求。 以上图为例,假设时序如下 在上图时序中: △T=Tskew T1=REG1检测到时钟后内部延时+组合逻辑延时最后到达REG2的时间 Tcycle=CLK的周期 Tsu=数据在CLK2上升沿到达前维持的时间 Tsu = Tcycle + Tskew-T1 Th=数据在CLK上升沿到达后维持的时间 Th = T1 – Tskew 如果Ts>setup time(触发器),Th>hold time(触发器)则数据能正常写入,由这个条件可以看出,Tskew与T1起着关键作用,而正之前所说如果使用全局时钟则Tskew会很小,可以忽略不计。 实例: 以上图为例Tsu= Tcycle + Tskew-T1要使Tsu最小,则Tskew最小,T1最大。 Tsu(min) = Tcycle + Tskew(min)-T1(max)=15+2+5+2-2-11-2-9-2 |

【本文地址】