FPGA逻辑设计回顾(1)新手易犯的逻辑综合错误之always块 |

您所在的位置:网站首页 › 逻辑错误是什么原因 › FPGA逻辑设计回顾(1)新手易犯的逻辑综合错误之always块 |

FPGA逻辑设计回顾(1)新手易犯的逻辑综合错误之always块

|

前言

注:本文首发自FPGA逻辑设计回顾(1)新手易犯的逻辑综合错误之always块 本文中用到了如下的小标题: “心中有路”与综合推断“心中无路”与无从推断这里所谓的路就是电路的意思,意思是逻辑工程师使用Verilog设计电路时要注重硬件思维,而不是软件编程。 心中有电路,在你使用RTL语言设计电路的时候,才能设计出综合工具能够推断出的具体硬件电路与之对应,否则可能语法过了,但是综合工具无法推断你的设计。 逻辑工程师在设计代码的时候要做到心中有电路,每一行代码的设计都是有对应硬件电路的。心中有电路,就是在编写Verilog程序的时候能明白我的设计会在FPGA中对应什么样的电路,使用的是什么样的资源,提前预知综合工具的想法,不一定全面,但是要有个大概,不要什么都交给综合工具去推断,这才是优秀的工程师应有的素质。 “心中有路”与综合推断FPGA设计中,逻辑工程师对于逻辑资源的使用,有如下几种方式:Instantiation,Inference,IP Catalog和Macro Support;其含义分别为: Instantiation即例化,例化一些Xilinx的原语资源,例如时钟BUFF资源: Inference即推断,这种方式无需你自己例化原语,综合工具会根据你的设计自动推断使用那些逻辑资源或者原语等,如: IP Catalog,即IP核的使用,这种方式是FPGA设计工程师最常用的方式,简单方便且效率高,不像原语那样,参数很多且不得不在原语模板中单独配置,IP核的定制只需在GUI界面里选择自己的参数即可。如果要使用无法推断的任何FPGA原语的大块,则应使用此方法。 例如,Xilinx的吉比特串行收发器资源: Macro Support即支持宏的方式,某些逻辑资源具有可以使用的UniMacro,这样的资源位于Xilinx的UniMacro库中,用于例化过于复杂而无法仅使用原语进行实例化的原语。综合工具见自动将UniMacros扩展为其底层原语。 这种方式过于复杂,一般不建议手动操作。 具体参考UG768 (v14.7); 注:原语是Xilinx FPGA中一种硬件资源,无须综合。在实现的过程中与综合之后的资源一起参与映射,布局布线等过程。 下面参考文献FPGA之道,给出原语的说法: 原语,英文名称primitive,是FPGA软件集成开发环境所提供的一系列底层逻辑功能单元。由于是底层逻辑功能单元,所以它们往往跟目标FPGA芯片以及芯片厂商紧密相关,因此不同厂商、不同器件的原语往往不能通用。当编译器对我们的HDL代码进行编译时,其中间环节的一些输出往往就是由原语组成的逻辑网表。因此,原语往往是不参与综合过程的,而使用原语描述的逻辑往往也不会被综合工具所优化。例如,Xilinx公司的ISE软件集成开发环境中的unisims库中定义了所有用于综合的原语,而simprims库中则定义了所有用于实现的原语。需要注意的是,如果我们去ISE安装目录下的verilog\src\unisims或verilog\src\simprims文件夹下去看这些原语的代码,可以发现其实这些并不是真正的原语,而是在原语的基础上又封装了一层,不过人们常常将它们也泛称为原语。 也可见授权分享链接:FPGA之道(68)原语的使用 总体而言,除了Inference不需要手动操作,其他都需要逻辑工程师自己动手。但并不是说Inference就很是一种傻瓜式的方式,非也!反而,对于优秀的逻辑工程师要求更高。逻辑工程师在设计代码的时候要做到心中有电路,每一行代码的设计都是有对应硬件电路的。心中有电路,就是在编写Verilog程序的时候能明白我的设计会在FPGA中对应什么样的电路,使用的是什么样的资源,提前预知综合工具的想法,不一定全面,但是要有个大概,不要什么都交给综合工具去推断,这才是优秀的工程师应有的素质。 “心中无路”与无从推断下面就讲两个小例子,关于设计师“心中无路”导致综合工具无从推断的示例: 你的设计在FPGA中无此资源对应如下一个例子是一个设计三分频电路的方面教材,其思路是想在参考时钟的1.5个周期处对分频时钟进行翻转来实现三分频: `timescale 1ns / 1ps // // Engineer: 李锐博恩 // Create Date: 2020/12/06 12:32:01 // Module Name: bad_demo // Additional Comments: // 这是一个方面素材,测试使用推断的方式来实现三分频电路,重点测试always块内双时钟的例子 // module bad_demo( input clk, input rst_n, output reg clk_divide ); wire clk_reverse; assign clk_reverse = ~clk; reg [3:0] count; always @ (posedge clk or posedge clk_reverse or negedge rst_n) begin if(!rst_n) begin count |

【本文地址】

今日新闻 |

推荐新闻 |

如上差分转差分的IBUFGDS原语,Xilinx推荐的使用方式就是通过直接例化的方式。

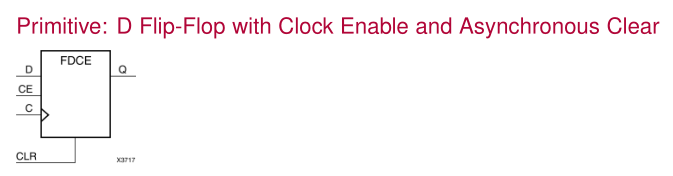

如上差分转差分的IBUFGDS原语,Xilinx推荐的使用方式就是通过直接例化的方式。 上图中的具有时钟使能以及异步复位的D触发器原语,Xilinx推荐的设计方式就是通过工具推断的方式。

上图中的具有时钟使能以及异步复位的D触发器原语,Xilinx推荐的设计方式就是通过工具推断的方式。 对于吉比特收发器资源的使用,Xilinx推荐是用IP核定制例化的方式。

对于吉比特收发器资源的使用,Xilinx推荐是用IP核定制例化的方式。