SPI协议详解(工作特点、时序图) |

您所在的位置:网站首页 › 通信协议的基本要求 › SPI协议详解(工作特点、时序图) |

SPI协议详解(工作特点、时序图)

|

文章目录

一、SPI总线介绍1.1.SPI信号列表1.2.SPI工作模式1.3.SPI特点——同步、串行、全双工、主从结构

二、SPI传输时序2.1.时钟极性CPOL与时钟相位CPHA2.2.时序图2.3.SPI配置信息2.4.SPI数据交换过程

一、SPI总线介绍

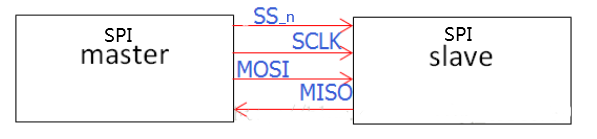

SPI,是英语Serial Peripheral interface的缩写,顾名思义就是串行外设接口。SPI协议主要作为主控芯片去配置外围芯片的接口协议。SPI接口主要应用在 EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。SPI是一种高速的,全双工,同步,串行,主从结构通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议。 SPI总线的传输速率需要自定义,没有具体的规定,一般为:400KHz~10MHz(AHB:100MHz,APB:50MHz) 主要功能:实现MCU与各种外接设备连接(芯片与芯片之间的连接),以串行的方式进行数据交换(串并转换)。拓扑结构:一个SPI Master可以通过共享数据线的方式可以连接多个SPI Slave(一主多从);接口配置:作为芯片与芯片之间互连的接口,通过配置寄存器实现主控芯片(SPI Master)对外围芯片(SPI Slave)的配置; 1.1.SPI信号列表 信号名含义描述SCKSerial Clock、时钟信号线Master 设备往 Slave 设备传输时钟信号, 同步控制数据交换的时机以及速率MOSIMaster Ouput Slave Input、主设备输出从设备输入数据线在 Master 上面也被称为 Tx-Channel, 作为数据的出口, 用于SPI主设备发送数据MISOMaster Input Slave Ouput、主设备输入从设备输出数据线在 Master 上面也被称为 Rx-Channel, 作为数据的入口, 主要用于SPI从设备接收数据SS_nSlave Select、从机选择线,低电平有效Master 设备片选 Slave 设备, 使被选中的 Slave 设备能够被 Master 设备所访问SS_n、SCK、MOSI信号均由主设备产生,MISO信号由从设备产生。在SS_n为低电平的前提下,MOSI和MISO信号才有效,在每个时钟周期MOSI和MISO传输一位数据。 1.2.SPI工作模式 SPI通讯需要使用4条线:3条总线和1条片选,物理连接如下: 需要说明的是,SPI只有主模式和从模式之分,没有读和写的说法,因为实质上每次SPI是主从设备在交换数据。也就是说,你发一个数据必然会收到一个数据;你要收一个数据必须也要先发一个数据。 二、SPI传输时序SPI 设备在进行通信的过程中, Master 设备和 Slave 设备之间会产生一个数据链路回环(Data Loop)。 SPI接口有四种不同的数据传输时序,取决于时钟极性(CPOL)和时钟相位(CPHA)的组合。 2.1.时钟极性CPOL与时钟相位CPHA CPOL:表示当SCLK空闲idle的时候,其电平的值是低电平0还是高电平1;CPHA:表示对应着数据采样是在第几个边沿(edge),是第一个边沿还是第二个边沿,0对应着第一个边沿,1对应着第二个边沿;1)、CPHA=0,表示第一个边沿: 对于CPOL=0,idle时候的是低电平,第一个边沿就是从低变到高,所以是上升沿; 对于CPOL=1,idle时候的是高电平,第一个边沿就是从高变到低,所以是下降沿; 2)、CPHA=1,表示第二个边沿: 对于CPOL=0,idle时候的是低电平,第二个边沿就是从高变到低,所以是下降沿; 对于CPOL=1,idle时候的是高电平,第一个边沿就是从低变到高,所以是上升沿; 参考:https://blog.csdn.net/ivy_reny/article/details/78189058?depth_1-utm_source=distribute.pc_relevant.none-task-blog-BlogCommendFromBaidu-6&utm_source=distribute.pc_relevant.none-task-blog-BlogCommendFromBaidu-6

|

【本文地址】

今日新闻 |

推荐新闻 |

SPI还是遵循主从结构,SPI协议适用于一主 多从的工作场景:

SPI还是遵循主从结构,SPI协议适用于一主 多从的工作场景:

Bit1为MSB,Bit8为LSB。假设CPOL=0,CPHA=0。在SCK的第一个时钟周期,在时钟的前沿采样数据(上升沿),在时钟的后沿输出数据。先看主器件,主器件的输出口(MOSI)输出数据bit1,在时钟的前沿被从器件采样,那主器件是何时输出bit1的呢?bit1的输出时刻实际上在SCK信号有效以前,比SCK的上升沿还要早半个时钟周期,bit1的输出时刻与SS_n信号没有关系。再来看从器件,主器件的输入口MISO同样是在时钟的前沿采样从器件输出的bit1的,那从器件又是在何时输出bit1的呢?从器件实在SS_n信号有效后,立即输出bit1,尽管此时SCK信号还没有生效。

Bit1为MSB,Bit8为LSB。假设CPOL=0,CPHA=0。在SCK的第一个时钟周期,在时钟的前沿采样数据(上升沿),在时钟的后沿输出数据。先看主器件,主器件的输出口(MOSI)输出数据bit1,在时钟的前沿被从器件采样,那主器件是何时输出bit1的呢?bit1的输出时刻实际上在SCK信号有效以前,比SCK的上升沿还要早半个时钟周期,bit1的输出时刻与SS_n信号没有关系。再来看从器件,主器件的输入口MISO同样是在时钟的前沿采样从器件输出的bit1的,那从器件又是在何时输出bit1的呢?从器件实在SS_n信号有效后,立即输出bit1,尽管此时SCK信号还没有生效。

SPI是一个环形总线结构,由SS_n (CS)、SCK、MOSI、MISO构成,时序很简单,在SCK的控制下,SSPSR是SPI设备内部的移位寄存器,根据SPI时钟信号状态,往SSPBUF里移入或移出数据,每次移动的数据大小由Bus-width和Channel-width决定。在正常工作时,两个双向移位寄存器进行数据交换,寄存器中的内容全部移出时,相当于完成了两个寄存器内容的交换。在每个时钟周期内,Master与Slave之间交换的数据其实都是SPI内部移位寄存器从SSPBUF里面拷贝的,可以通过往SSPBUF对应的寄存器(Tx-Data/Rx-Data register)里读写数据,间接操控SPI内部的SSPBUF。SSPSR控制数据移入移出SSPBUF。Master里面的Controller主要通过时钟信号以及片选信号来控制Slave。Slave会一直等待,直到接收到Master发过来的片选信号,然后根据时钟信号来工作。Master的片选操作必须由程序实现。。

SPI是一个环形总线结构,由SS_n (CS)、SCK、MOSI、MISO构成,时序很简单,在SCK的控制下,SSPSR是SPI设备内部的移位寄存器,根据SPI时钟信号状态,往SSPBUF里移入或移出数据,每次移动的数据大小由Bus-width和Channel-width决定。在正常工作时,两个双向移位寄存器进行数据交换,寄存器中的内容全部移出时,相当于完成了两个寄存器内容的交换。在每个时钟周期内,Master与Slave之间交换的数据其实都是SPI内部移位寄存器从SSPBUF里面拷贝的,可以通过往SSPBUF对应的寄存器(Tx-Data/Rx-Data register)里读写数据,间接操控SPI内部的SSPBUF。SSPSR控制数据移入移出SSPBUF。Master里面的Controller主要通过时钟信号以及片选信号来控制Slave。Slave会一直等待,直到接收到Master发过来的片选信号,然后根据时钟信号来工作。Master的片选操作必须由程序实现。。