|

蜂鸣器按照构造方式的不同,可分为压电式蜂鸣器和电磁式蜂鸣器两种类型,由于两种蜂鸣器发音原理不同,压电式结构简单耐用但音调单一音色差,适用于报警器等设备。而电磁式由于音色好,所以多用于语音、音乐等设备。

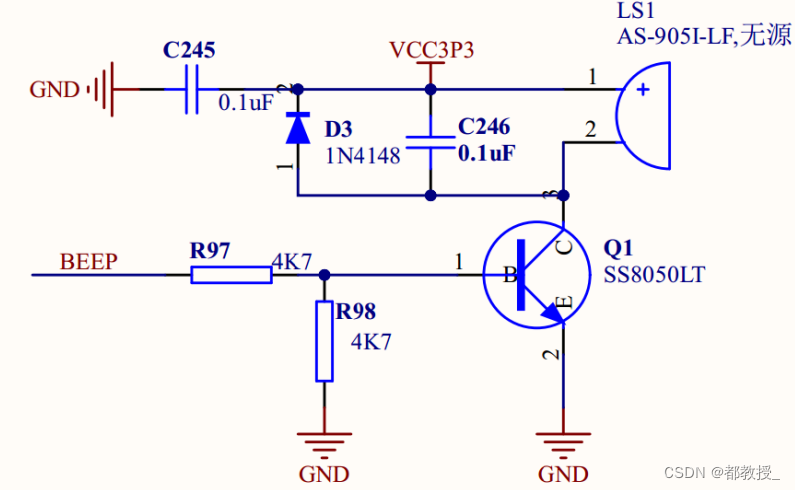

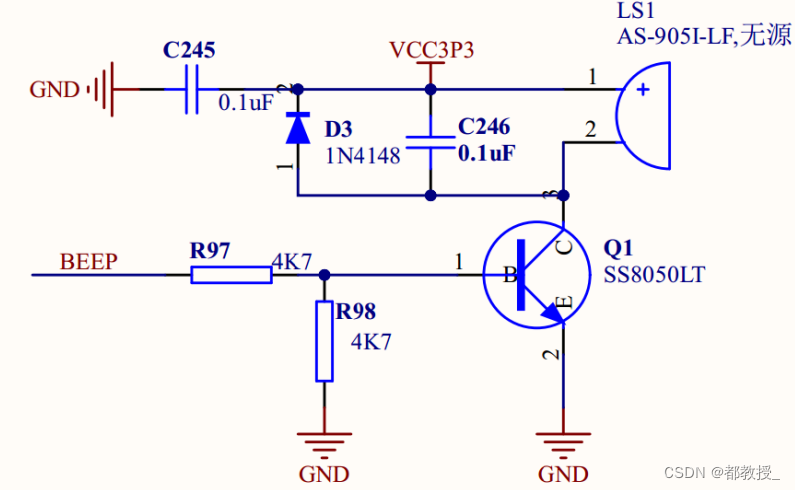

蜂鸣器按照驱动电路的不同可以分为有源蜂鸣器与无源蜂鸣器。有源蜂鸣器内部带震荡源,所以只要通电就会鸣叫;而无源蜂鸣器内部不带震荡源,因此如果用直流信号无法令其鸣叫,这就需要用 2K-5K 的方波(声音频率)去驱动。ACZ702 开发板上使用了一枚 3.3V 直流电压驱动的电磁式无源蜂鸣器。其原理图如下图所示:

BEEP 端口接FPGA 输出管脚,使用时只需要在 BEEP 信号上输入 2~5KHz 的 PWM 波,就能

驱动蜂鸣器按照既定的频率产生振动信号。

二:无源蜂鸣器驱动原理

通过前面对无源蜂鸣器的特点介绍可知,要使无源蜂鸣器能够正常发声,需要在控制端 BEEP

给出相应频率的

PWM

波。因此,对于无源蜂鸣器的控制,

就转化为了设计一个

PWM

波发生电路。因此,接下来将介绍

PWM

波的发生部

分相关设计。

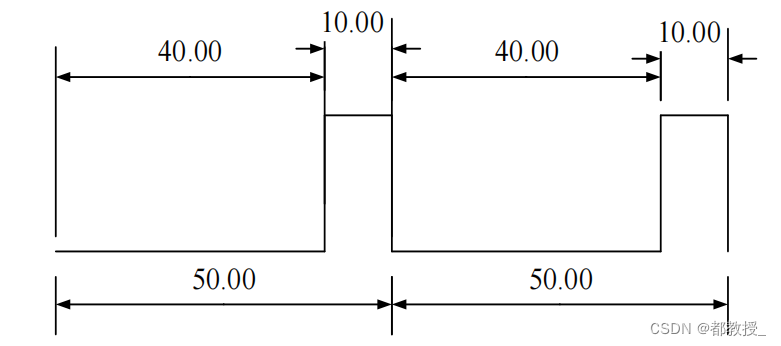

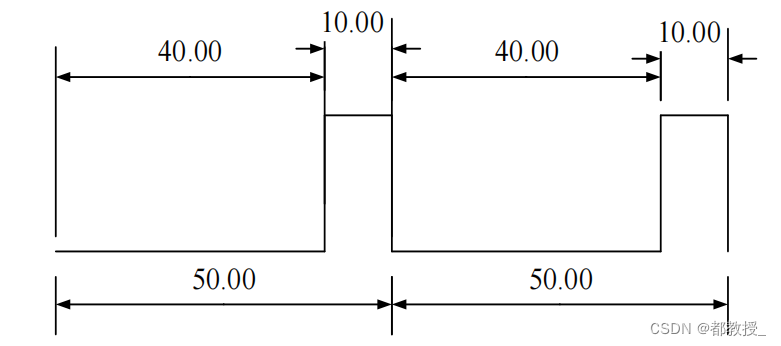

PWM 波即脉冲宽度调制,以下为周期为

1KHz

,脉冲宽度(占空比)为

20%的示意图

由上图可知,当信号周期一定,信号高电平时间所占信号周期的百分比不一样,即为不同占空比的

PWM 波。而除了调整

PWM

信号的占空比,

PWM 信号的周期也是可以调整的,

对于不同的器件,对驱动信号的频率要求也不一样,还需要能够对

PWM

波的频率进行调整。

通过以上分析,可以看出,要设计一个

PWM

发生电路,需要能够实现对信号的频率和占空比的调节。

在

单片机或者 DSP

中,产生

PWM

波的方法就是

使用片上定时器进行循环计数,通过设定定时器的一个定时周期时长来确定对

应输出

PWM

信号的频率,同时还有一个比较器,该比较器比较定时器的实时

计数值与用户设定的比较值的大小,根据比较结果来控制输出信号的电平高低。

通过设定不同的比较值,即可实现不同占空比的

PWM 信号输出。使用定时器产生

PWM

原理图如下:

三:PWM 发生器模块设计

对于

FPGA

来说,要产生

PWM

波,也可以借鉴单片机或

DSP

使用定时器产生

PWM

波的思路。依据

PWM 模块发生器原理可知需设计两个主要电路:定

时器

/

计数器电路以及输出比较电路。

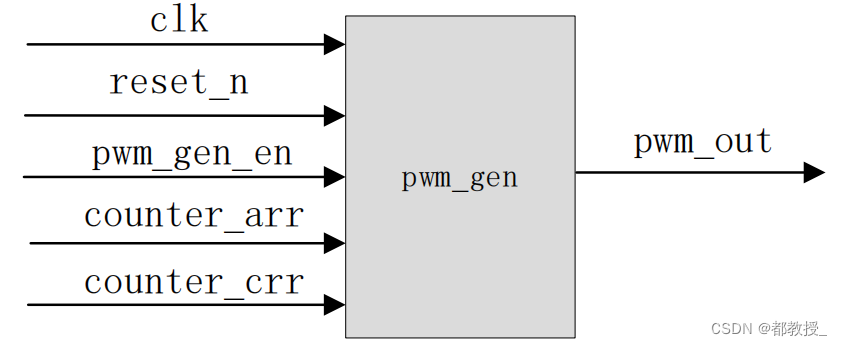

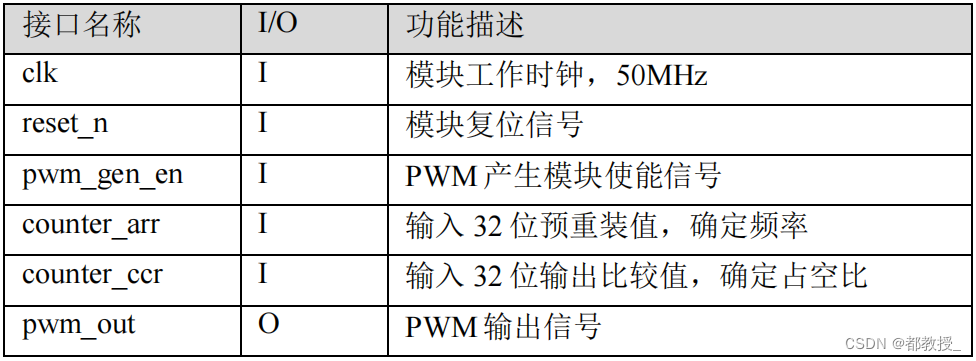

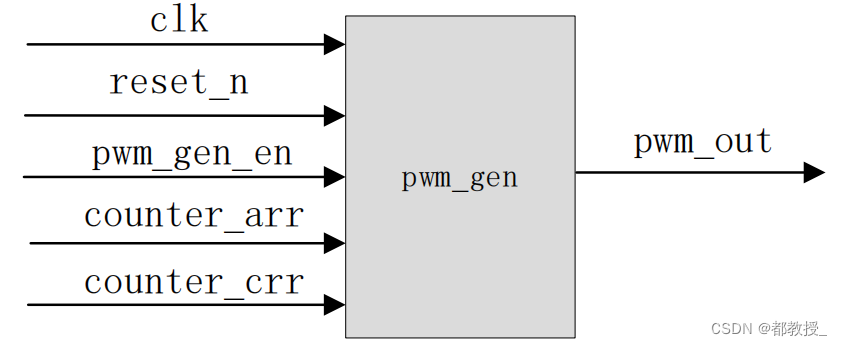

3.1 PWM 发生器模块框图

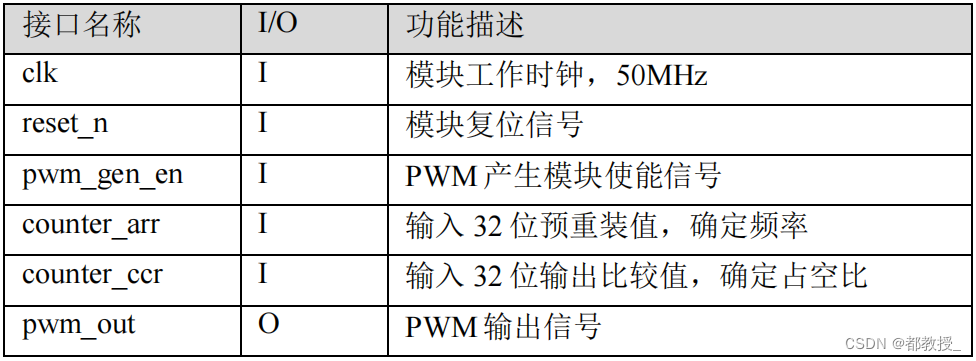

3.2 PWM 发生器模块接口功能描述

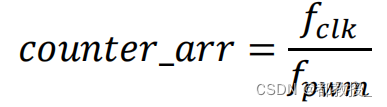

最终输出

PWM

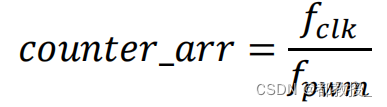

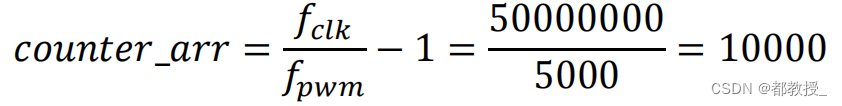

波的频率计算公式为:

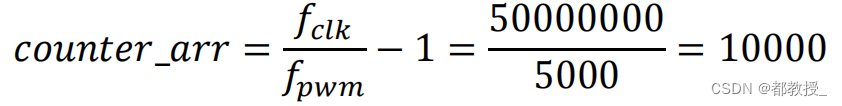

其中,这里的

counter_arr

是自减计数器的预重装值,计数器是从

counter_arr开始递减到

1

。因此,当输出频率确定时,可计算得到预重装值,计算公式为:

例如,当希望设置输出信号频率为

5KHz

时

因此,只需要设置

counter_arr

值为

10000

即可使得最终输出信号频率为5KHz

。

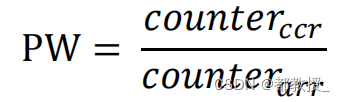

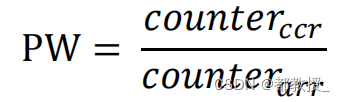

当输出

PWM

频率确定后,其输出占空比计算则为输出比较值与预重装值

之商。计算公式为:

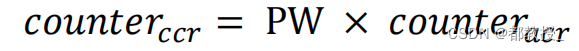

因此,当输出占空比确定时,可计算得到输出比较值,计算公式为:

在运行过程中,修改预重装值可以设置输出 PWM

信号的频率,并将同时影响输出占空比,而在预重装值确定的情况下,修改输出比较值,则可以设置

输出占空比。

3.3 PWM波生成设计文件代码

module pwm_gen(

input clk,

input reset_n,

input pwm_gen_en,//使能信号

input [31:0]counter_arr,//预重装值,用来设定频率

input [31:0]counter_crr,//比较值,用来调节占空比

output reg pwm_out//输出pwm波

);

reg [31:0]pwm_gen_cnt;

always@(posedge clk or negedge reset_n)

if(!reset_n)

pwm_gen_cnt |